Laterally diffused metal oxide semiconductor transistor and manufacturing method thereof

A technology of oxide semiconductors and production methods, which is applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of electric field line bending, channel penetration, leakage, etc., and achieve effective path shortening, channel area Effects of shrinkage and on-resistance reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

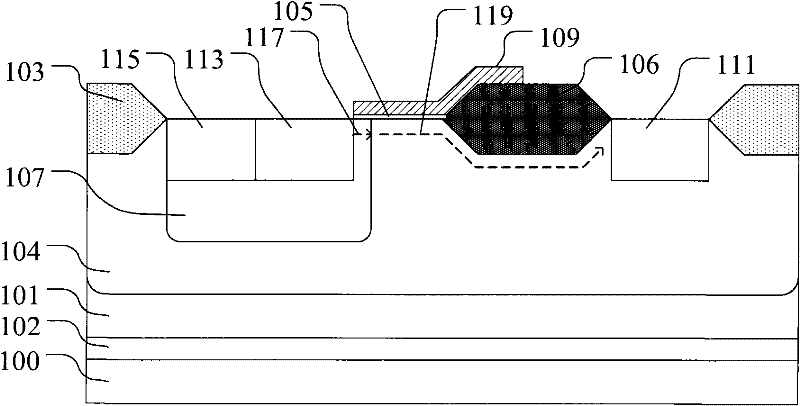

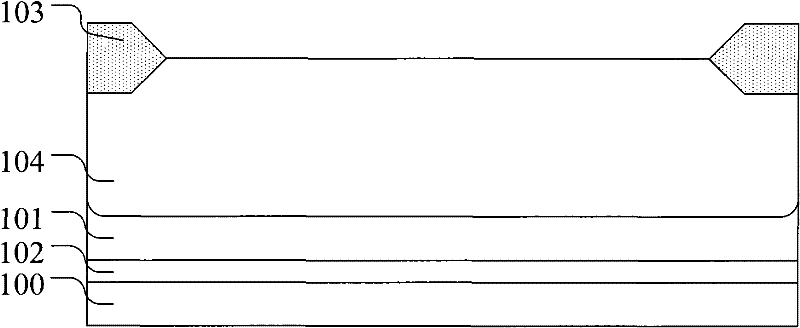

[0028] In the LDMOS transistor in the prior art, the field plate of the LDMOS transistor is formed by using the LOCOS oxide layer, and the unique bird's beak region of the LOCOS oxide layer can make the gate electrode gradually expand from a thinner gate dielectric layer to a thicker field plate. This gradual gate electrode structure can weaken the surface electric field near the gate electrode, which is beneficial to improve the breakdown voltage of the LDMOS transistor.

[0029] However, the bird's beak region of the LOCOS oxide layer will partially sag the silicon-silicon oxide interface downward, and change the direction of the current flow in the drift region, which makes the electric field lines in the channel region bend, and the curved electric field lines As a result, the electric field lines near the drain region are concentrated, and channel punch-through is prone to occur.

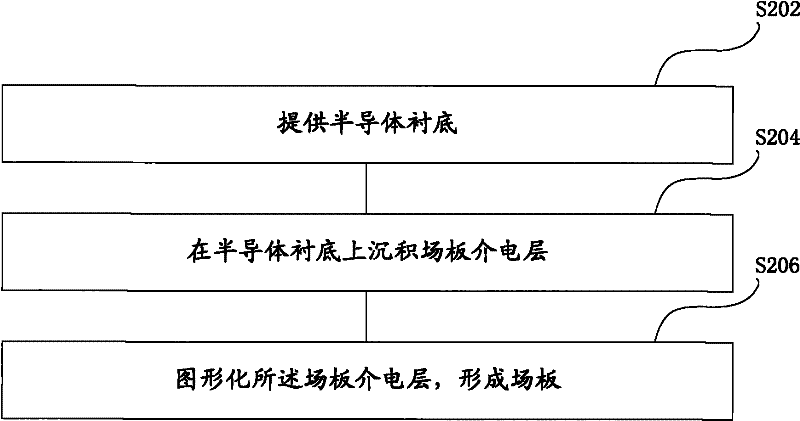

[0030] In view of the above problems, the inventor provides the following technical solutio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More