Turnover type sampling hold circuit

A sample-and-hold circuit and flip-type technology, applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, physical parameter compensation/prevention, etc., can solve the problem of limiting input signal bandwidth, large distortion, Large consumption and other issues, to achieve the effect of increased input bandwidth, reduced nonlinearity, and reduced power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

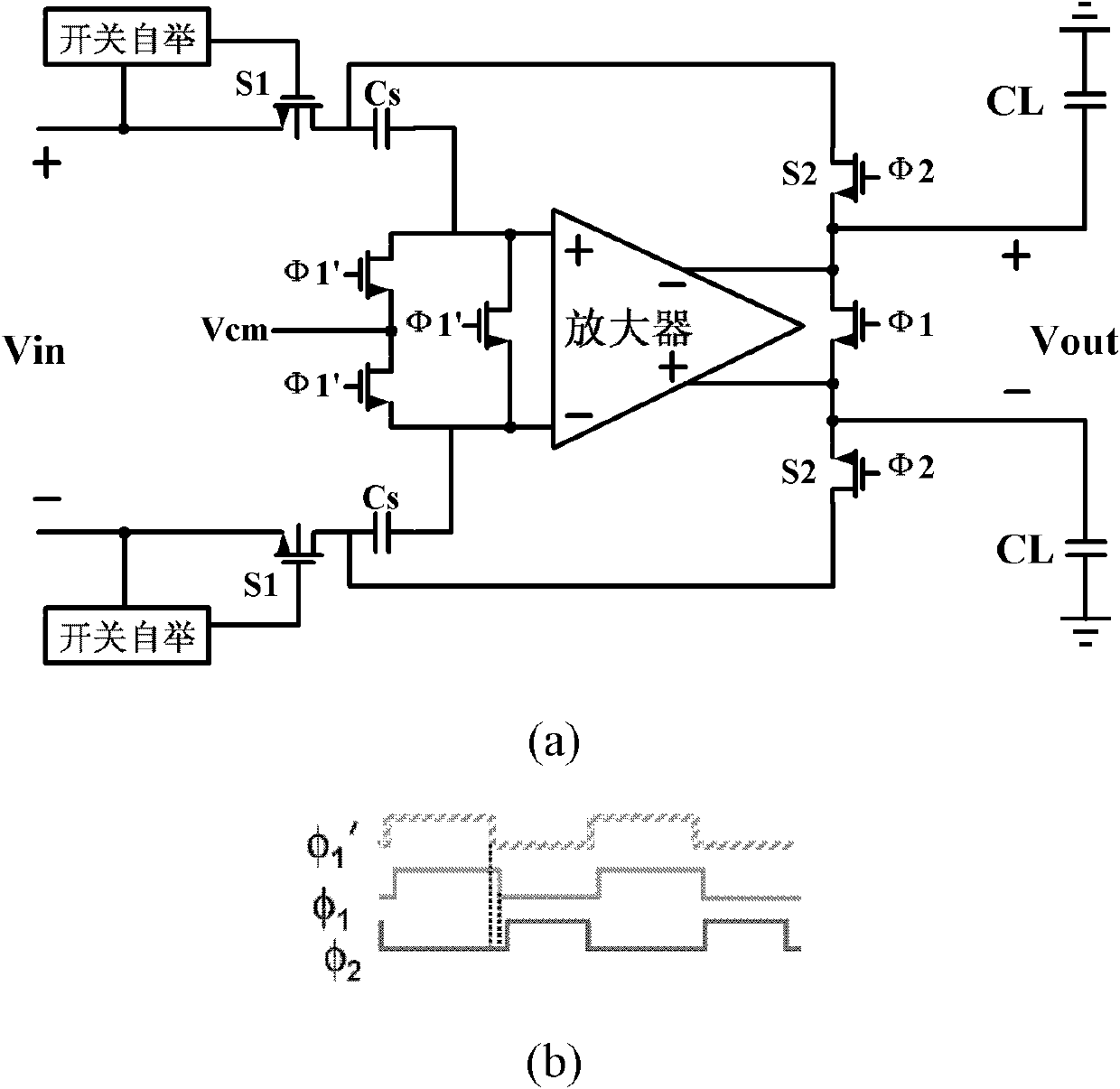

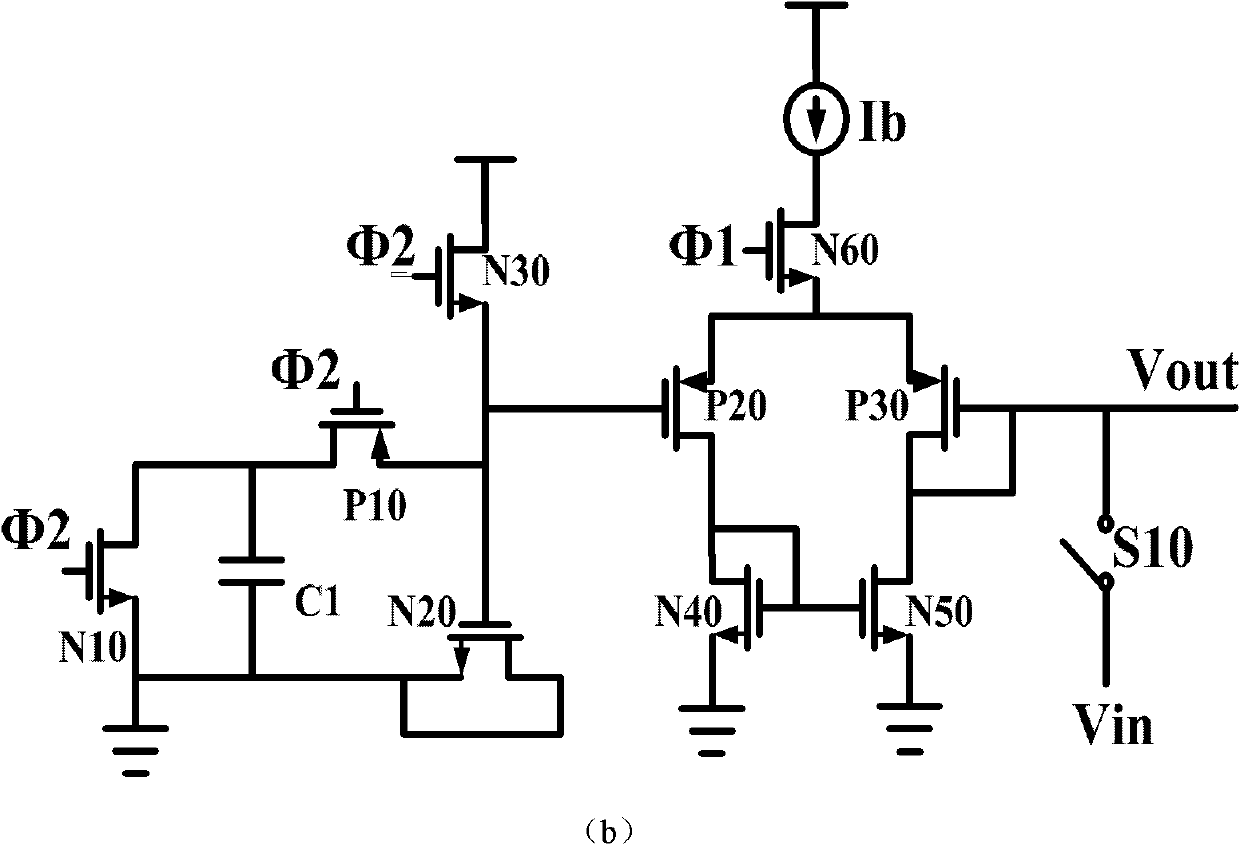

[0018] see Figure 2-4 .

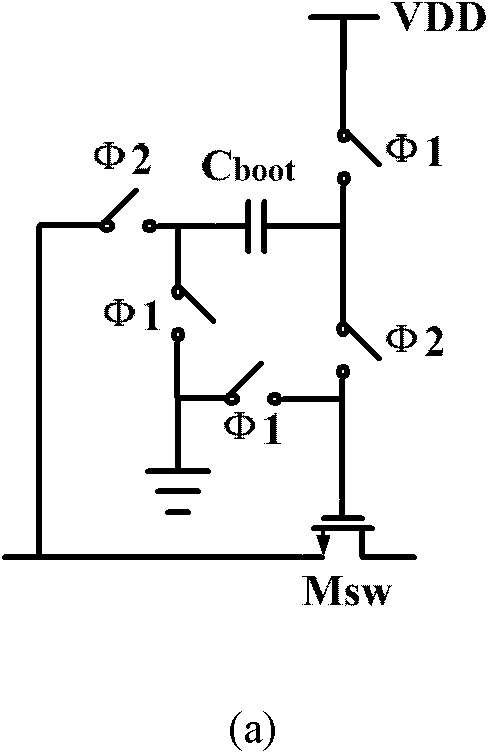

[0019] The inverted sample-and-hold circuit of the present invention includes a first switch bootstrap circuit 101, a first sampling switch tube S11, a second switch bootstrap circuit 102, a second sampling switch tube S12, an amplifier and a first load capacitance circuit, a second The load capacitor circuit is characterized in that the first switch bootstrap circuit and the second switch bootstrap circuit have the same structure, the first switch bootstrap circuit 101 includes a charge compensation circuit, and the charge compensation circuit includes a first capacitor forming a loop C1 and the second NMOS transistor N20.

[0020] The first switch bootstrap circuit includes:

[0021] The gate of the first NMOS transistor N10 is connected to the second control signal Ф2, the drain is connected to the drain of the first PMOS transistor P10, and the source is grounded;

[0022] The gate of the first PMOS transistor P10 is connected to the second co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More