Condition-precharged sense-amplifier-based flip flop

A technology of sensitive amplifiers and triggers, applied to instruments, static memory, digital memory information, etc., to eliminate competition problems, overcome timing errors, and reduce energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

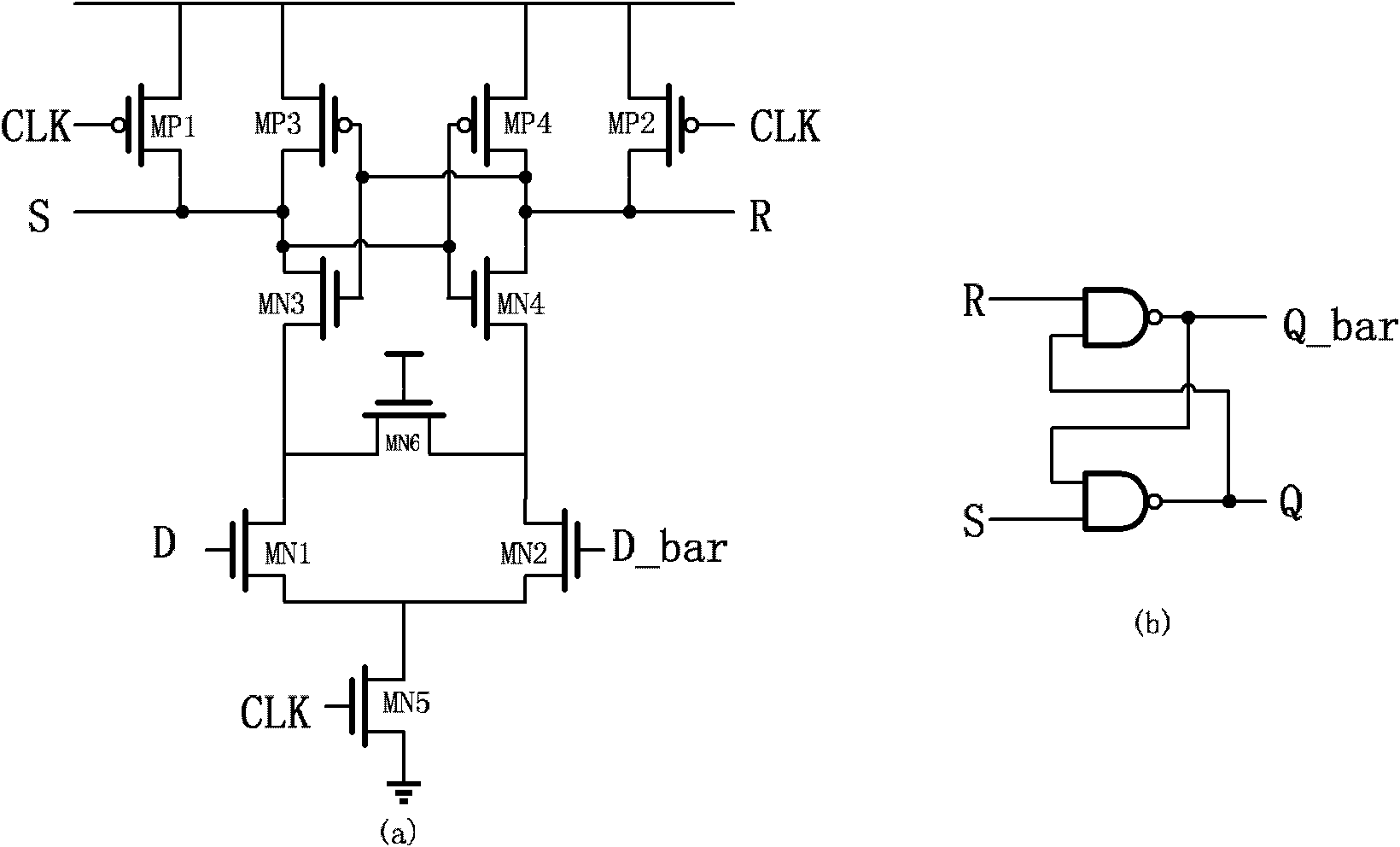

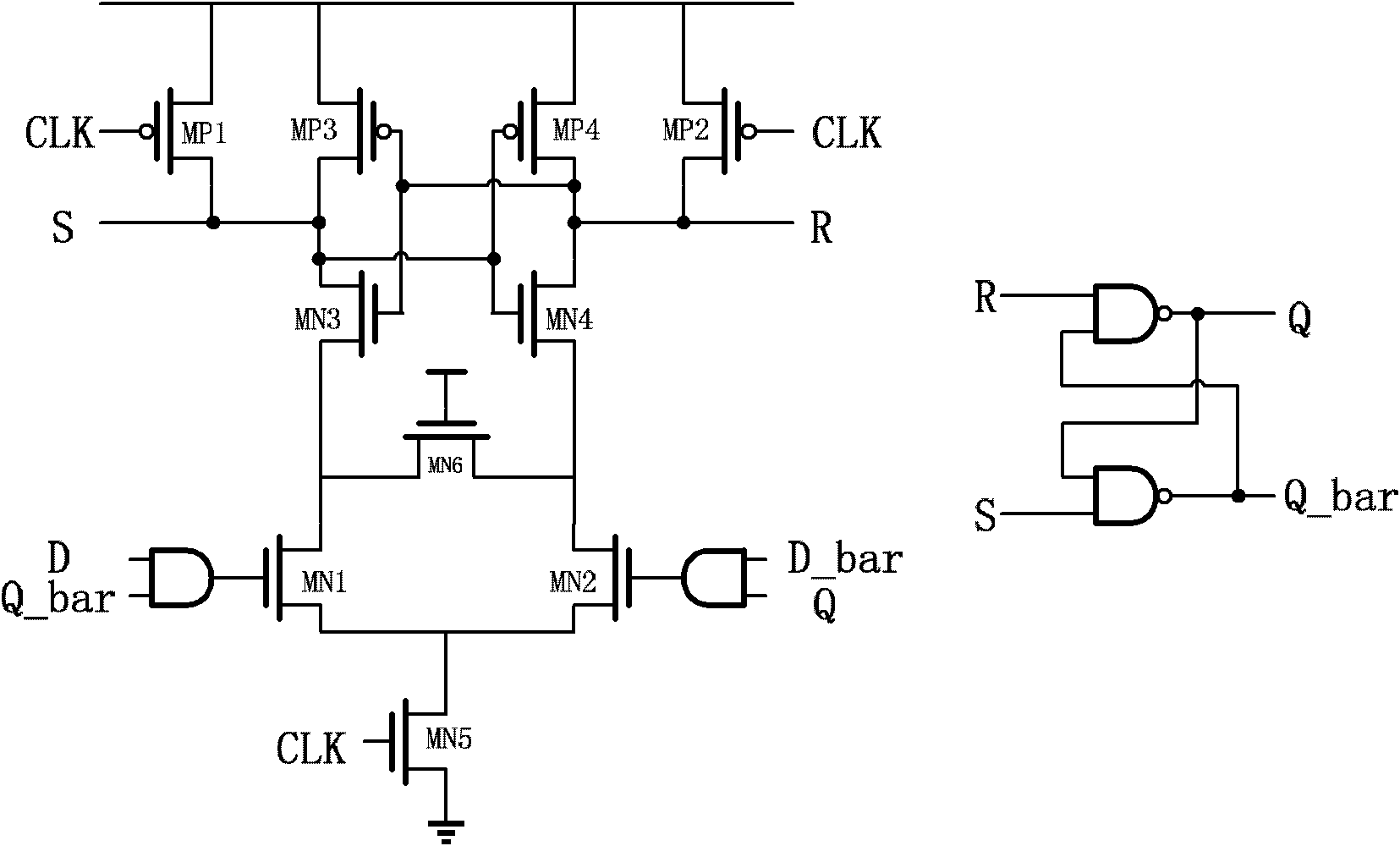

[0040] The present invention proposes a conditionally precharged sense-amplifier-based flip-flop (Data-Dependent-Precharge Sense-Amplifier-based Flip-Flop, abbreviated as DDP-SAFF in the present invention).

[0041] The invention adopts the way of feedback control precharge, redesigns the first-stage sensitive amplifier, and reduces the power consumption of SAFF. The second-stage sense amplifier is combined with a high-speed SR latch to form a high-performance flip-flop.

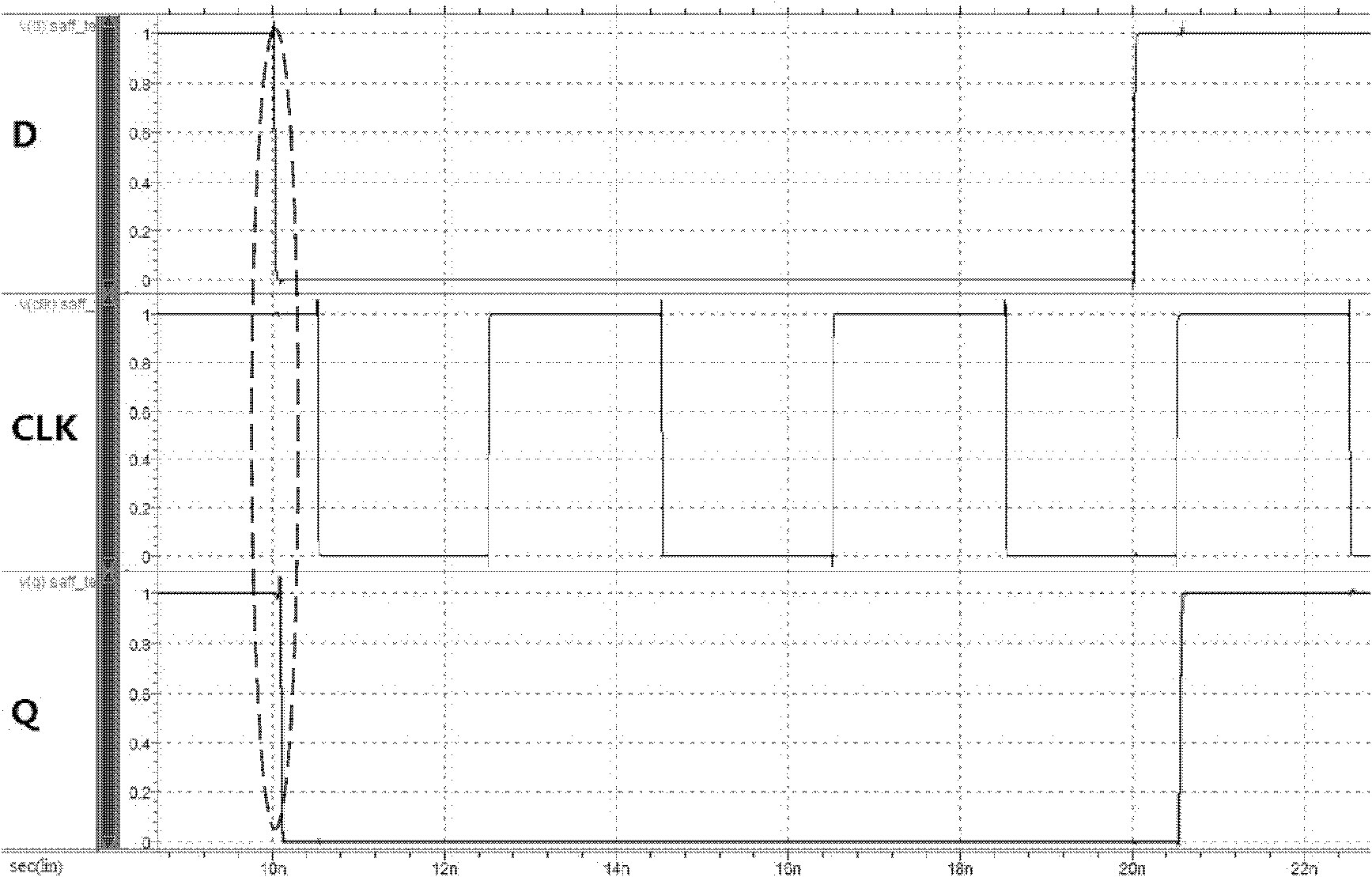

[0042] The invention is based on figure 1 The different states of D point and Q point in the middle control the jump of internal nodes, thus saving a lot of unnecessary energy consumption. From the ab...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More