DMOS device and manufacturing methods thereof

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve the effects of increasing doping concentration, improving conduction breakdown voltage, and widening the safe working area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

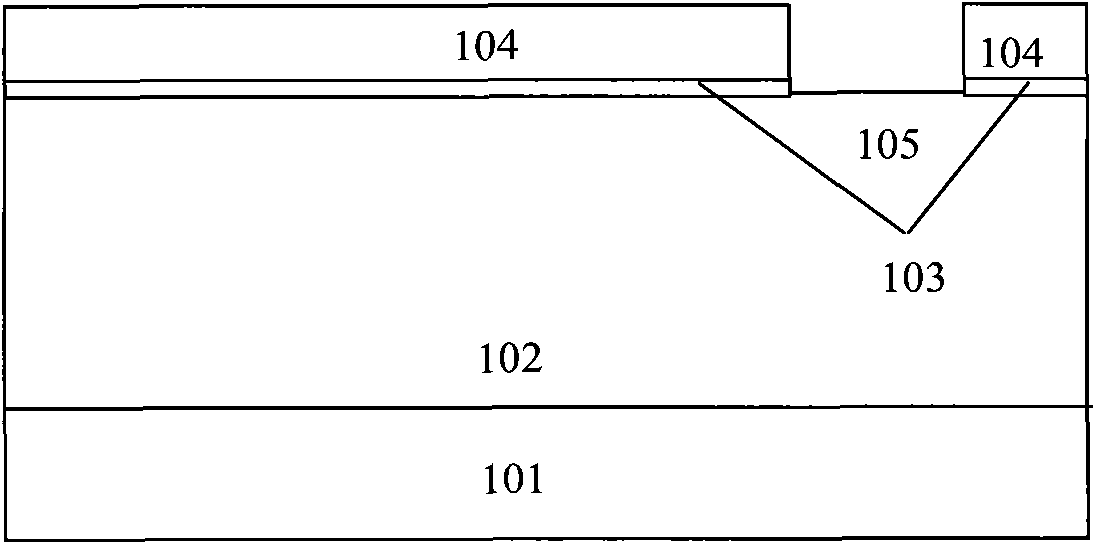

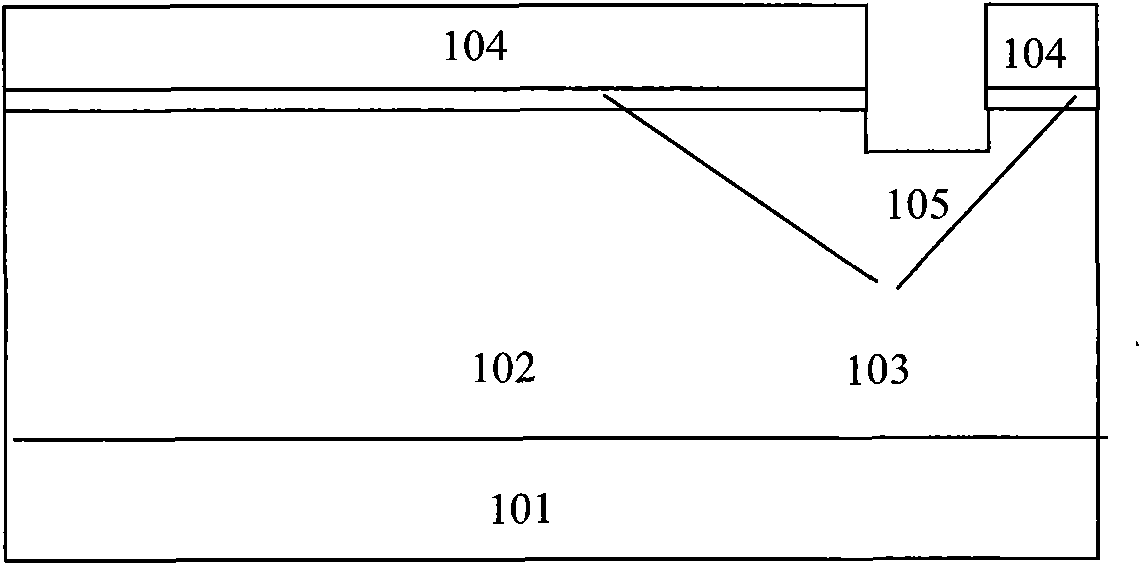

[0027] Such as Figure 1 to Figure 5 As shown, it is a schematic diagram of the device structure in each step of a DMOS device manufacturing method according to the embodiment of the present invention. Embodiment 1 DMOS device manufacturing method of the present invention comprises the following steps:

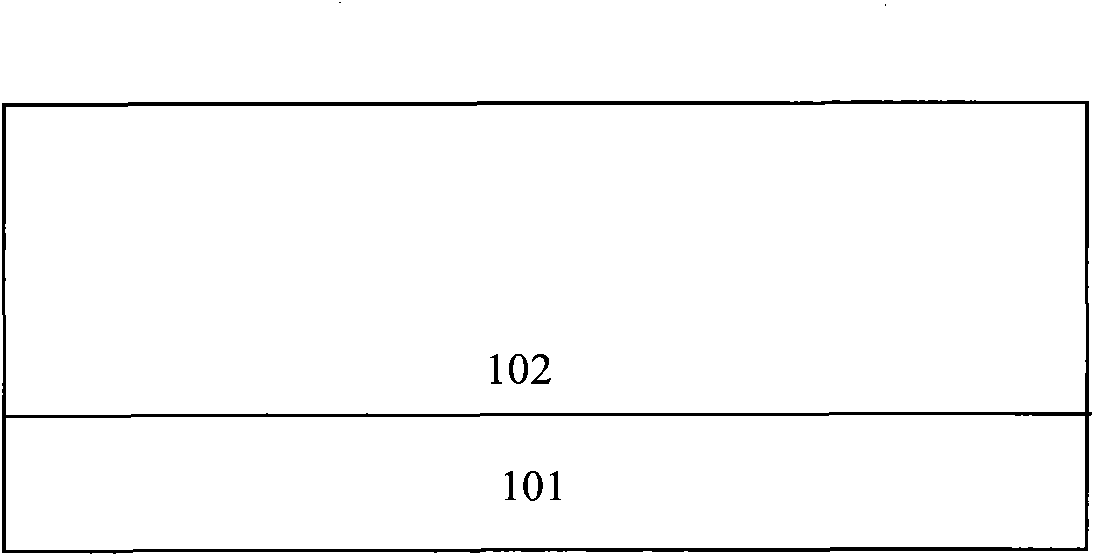

[0028] Step 1, such as figure 1 As shown, multiple second conductivity type ion implantations are performed on the first conductivity type silicon substrate 101, and the implantation energy of the second conductivity type multiple ion implantations is gradually reduced according to the order of implantation, and finally a light doping drift is formed. region 102 , where the impurity implanted with ions with low implantation energy is at the upper position of the lightly doped drift region 102 . For N-type DMOS, the implantation impurity for multiple ion implantations of the second conductivity type is phosphorus or arsenic, the implantation energy is 10KeV-1500KeV, and the ...

Embodiment 2

[0033] Such as Figure 6 to Figure 10 Shown is a schematic diagram of the device structure in each step of the DMOS device manufacturing method in Embodiment 2 of the present invention. The second DMOS device manufacturing method of the present invention includes the following steps:

[0034] Step 1, such as Figure 6 As shown, the first ion implantation of the second conductivity type is performed on the substrate 201 of the first conductivity type to form a lightly doped drift region 202 ; an isolation oxide layer is formed, and the lightly doped drift region 202 is thermally advanced. For N-type DMOS, the impurity implanted in the first ion implantation is phosphorus or arsenic, the implantation energy is 10KeV-1500KeV, and the implantation dose ranges from 1e11cm -2 ~1e13cm -2 . For P-type DMOS, the implanted impurity for the first ion implantation is boron, the implantation energy is 5KeV-1000KeV, and the implantation dose range is 1e11cm -2 ~1e13cm -2 . The isolat...

Embodiment 40V

[0039] Such as Figure 5 As shown, the DMOS device of the embodiment of the present invention realizes the high breakdown voltage of the DMOS device through the drift region under the local field oxygen isolation oxide layer 106, that is, the lightly doped drift region 105, that is, the cut-off breakdown voltage of the DMOS device can be maintained. unchanged or improved; and through the drift region of the active region, that is, the improvement of the doping concentration of the middle-doped drift region 107 between the channel region 108 and the local field oxygen isolation oxide layer 106, it can effectively improve The on-breakdown voltage of the DMOS can also reduce the on-resistance of the DMOS and widen the safe working area of the DMOS. The main theoretical basis is: since the drift region mainly relies on the region under the isolation oxide layer, namely the lightly doped drift region 105 for voltage division, light doping is required to ensure a high breakdown vo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More