Polishing pad, polyurethane layer therefor, and method of polishing a silicon wafer

A polyurethane layer, polishing pad technology, applied in the field of 20 to 200 micron pores, chemical-mechanical polishing pads, can solve problems such as increased surface roughness, undulation damage, chemical properties of CMP pads and mechanical structure deterioration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0123] Polyurethane layers were prepared by the method described above using the formulations shown in Table 3.

[0124] table 3

[0125] Example 1

components

number of copies

Part A

PTMEG

60.60

MP diol

13.70

13.41

Surfactant

1.88

Catalyst-1

5.81

PTFE No.2

4.61

Total, Part A

100.01

OH#

284

Part B

94.46

total number of copies

[0126] Materials prepared according to this formulation are rigid microcellular high modulus polyurethanes. For Example 1, the M of the foamed cured polyurethane C (Molecular weight between crosslinking points) is equal to 4521.33.

[0127] To test the material for CMP polishing, a polishing pad made from the formulation of Example 1 (Example P-1) was used for copper planarization, which was then compared to a conventional IC1000 CMP pad made by Rohm and Haas . T...

Embodiment 2

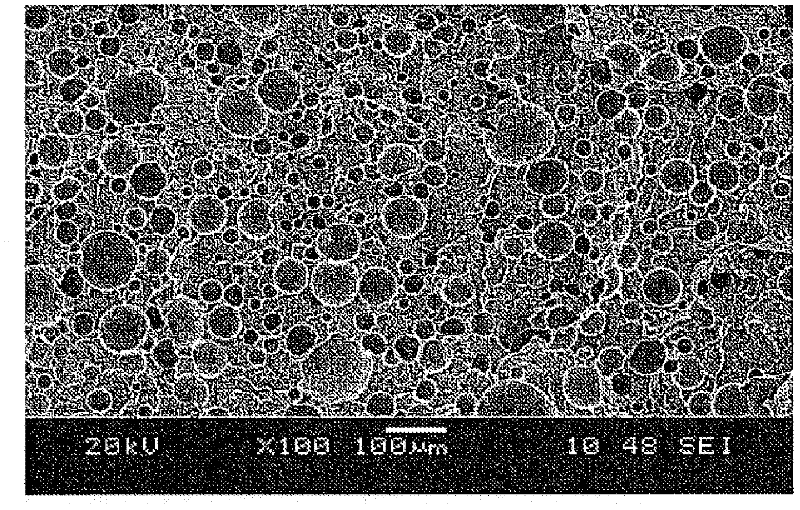

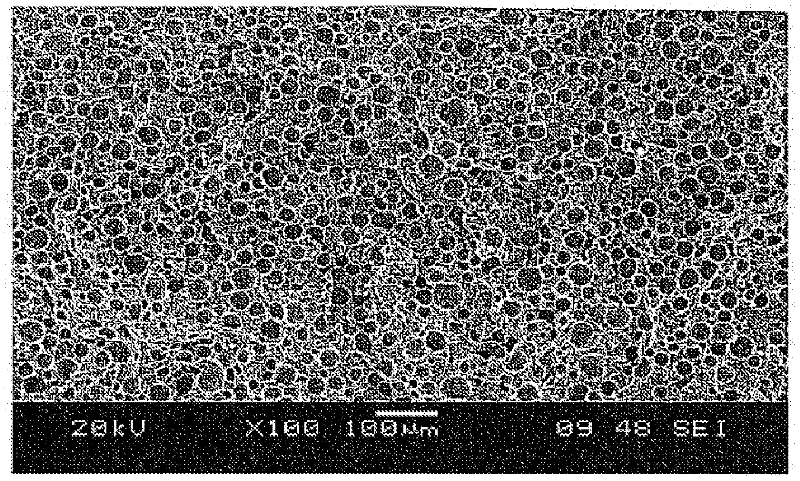

[0141] Different formulations containing hydrophobic particles were prepared. figure 1 shows a scanning electron microscope (SEM) of a polyurethane material prepared generally according to the examples described herein without the use of PTFE microparticles, figure 2 A comparable formulation using PTFE microparticles is shown. The effect of the PTFE microparticles in the polyurethane foam was to produce smaller and more consistent cells based on the SEM images.

[0142] Measured using the above surface energy test figure 2 The surface of the polyurethane material in the surface. The results of contact angle (CA) and surface energy are shown in Table 6.

[0143] Table 6

[0144]

[0145] Therefore, it is believed that the presence of hydrophobic particles reduces the surface energy of the polyurethane material. In forming a CMP polishing pad, the resulting surface can be abraded, which can change the measured surface energy of the polyurethane.

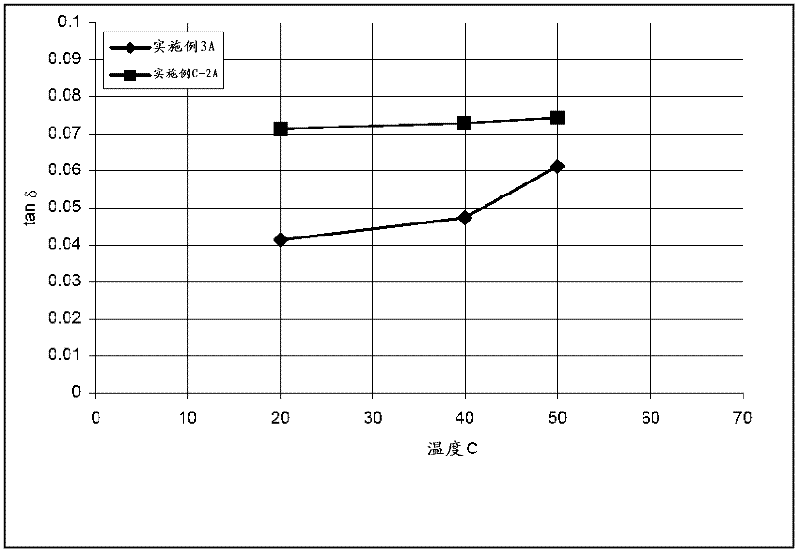

Embodiment 3-6

[0147] These examples illustrate the tuning of the modulus properties of polyurethane materials for CMP polishing by varying the concentrations of the individual components of the reaction mixture used to form the polyurethane materials. Top pads based on the two formulations shown in Table 7 were prepared.

[0148] Table 7

[0149] Example 3

Example 4

Material

number of copies

number of copies

Part A

PTMEG polyol

66.41

63.41

MP diol

7.89

10.89

13.41

13.41

Surfactant

3.76

3.76

Catalyst-2 *

5.81

5.81

PTFE No. 2

4.61

4.61

Total Copies, Part A

101.89

101.89

OH#

280

315

Part B

93.01

106.65

[0150] * dilute with polyol

[0151] The microporous topsheet prepared according to Example 3 was similar to the formulation of Example 1 above...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Density | aaaaa | aaaaa |

| Median particle size | aaaaa | aaaaa |

| Median particle size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More