Forming method of grid oxidation layer

A technology of gate oxide layer and gate oxide, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problem of reducing the probability of carrier capture, etc., to suppress thermionic effect and reduce interface defects , reducing the effect of silicon dangling bonds

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

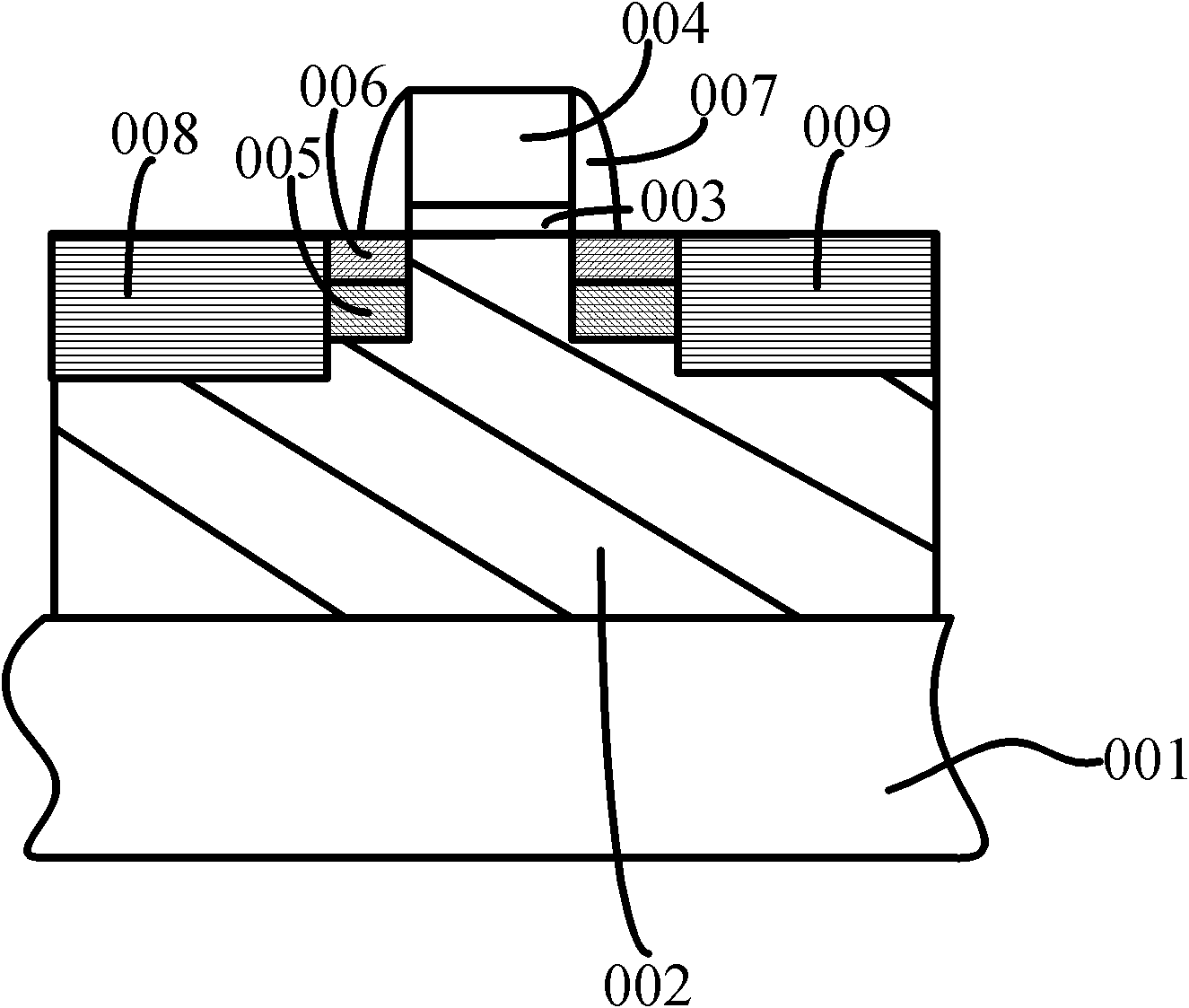

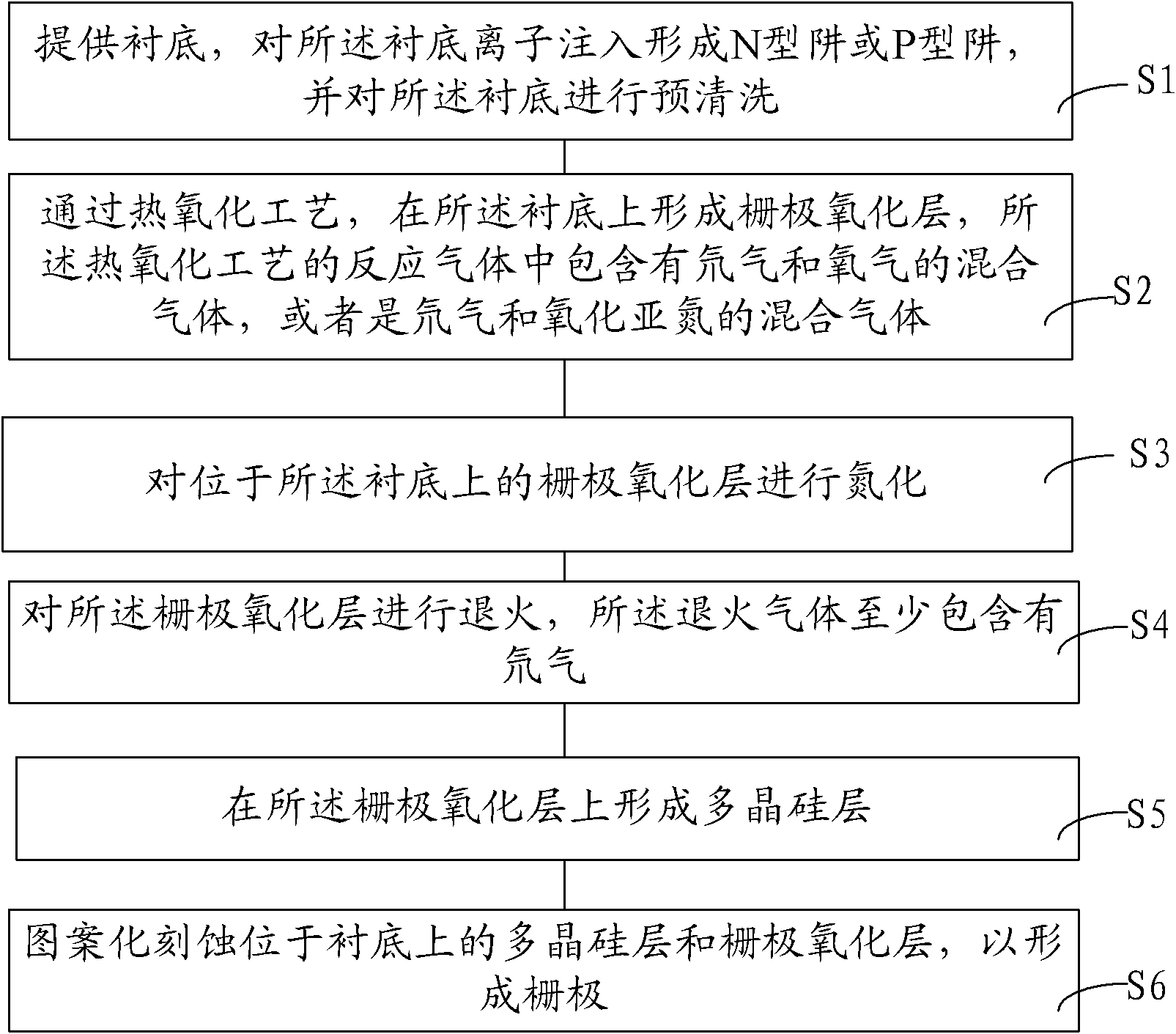

[0024] As the device size shrinks, the thickness of the gate oxide layer becomes correspondingly thinner at the same time. However, when the thickness is reduced to a certain extent, the gate oxide layer is too thin to provide sufficient electrical isolation between the gate conductive material and the underlying semiconductor substrate. More importantly, a thinner gate oxide tends to allow implanted dopant ions to diffuse into the gate oxide. Further, through the semiconductor process environment, the interface between the gate oxide layer and the silicon substrate contains a large number of silicon dangling bonds, and interface defects are formed in the gate oxide layer, making the silicon dangling bonds easy to capture electrons, resulting in hot electrons effect; the silicon dangling bond may also bond with hydrogen in the thermal oxidation process, the silicon-hydrogen bond is weak, and it is easy to break the bond in an external stress environment, and the silicon dangli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More