Flash sense amplifier

A sensitive amplifier and sensitive amplification technology, which is applied in the direction of instruments, static memory, digital memory information, etc., can solve problems such as unresolved impact, circuit power consumption, circuit working state change, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

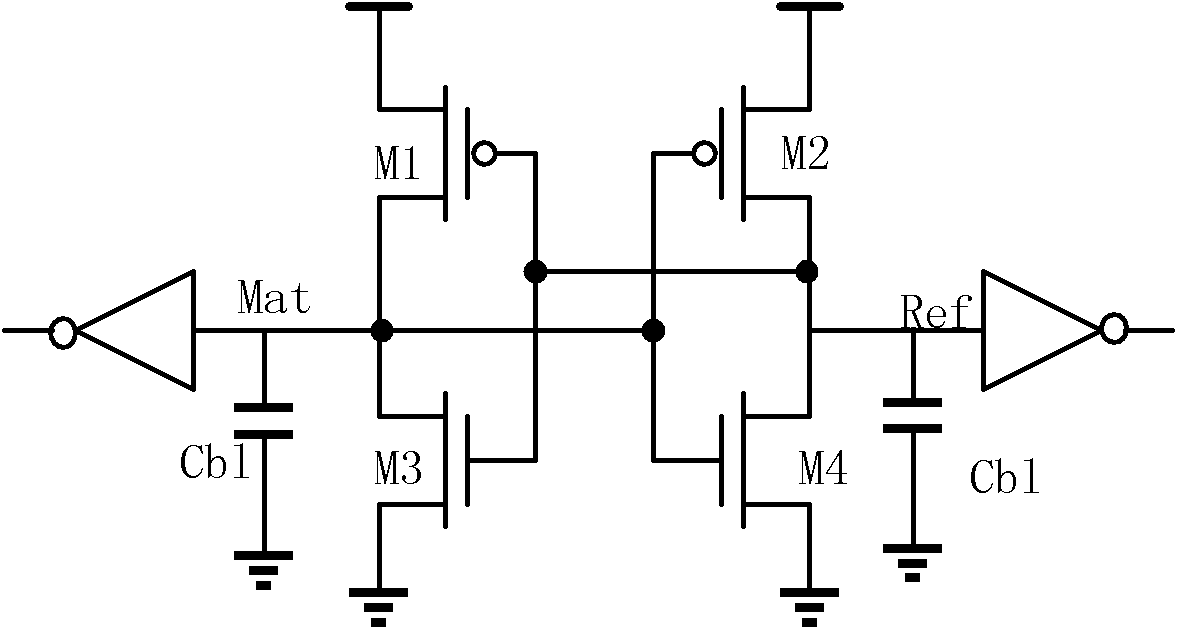

[0047] This embodiment describes a kind of Flash sensitive amplifier, comprising:

[0048] first inverter;

[0049] The second inverter is used to couple with the first inverter to form a bistable circuit of positive feedback amplification;

[0050]The first amplification control unit is used to realize the on-off between the input terminal of the first inverter and the output terminal of the second inverter under the control of the sensitive signal, that is, to connect in the sensitive amplification stage, and in the The potential input stage is disconnected;

[0051] The second amplification control unit is used to realize the on-off between the output terminal of the first inverter and the input terminal of the second inverter under the control of the sensitive signal, that is, in the sensitive amplification stage Connected, disconnected during the potential input stage;

[0052] a third inverter, the input end of which is connected to the input end of the first inverter...

Embodiment 2

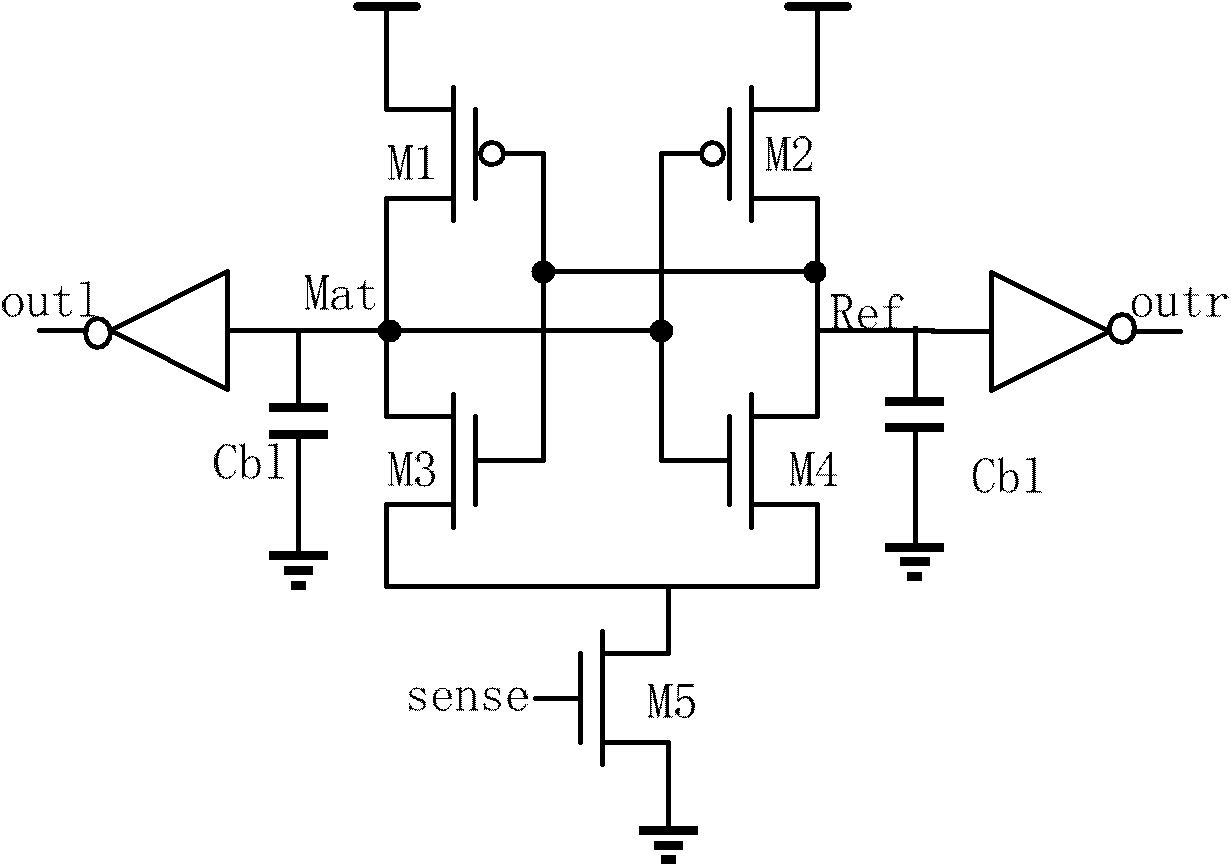

[0061] Such as Figure 5 Shown, the Flash sensitive amplifier of present embodiment record comprises:

[0062] first inverter inv101;

[0063] The second inverter inv102 is used to couple with the first inverter inv101 to form a bistable circuit of positive feedback amplification;

[0064] The gate of the first NMOS transistor M101 is connected to the sensitive signal sense, and the non-gate poles are respectively connected to the input terminal in101 of the first inverter inv101 and the output terminal out102 of the second inverter inv102;

[0065] The gate of the second NMOS transistor M102 is connected to the sensitive signal sense, and the non-gate poles are respectively connected to the output terminal out101 of the first inverter inv101 and the input terminal in102 of the second inverter inv102;

[0066] The third inverter inv103, the input terminal is connected to the input terminal in101 of the first inverter inv101, and the output terminal is connected to the left o...

Embodiment 3

[0084] Such as Figure 8 As shown, the basic structure of this embodiment is the same as that of Embodiment 2, the difference is that this embodiment will:

[0085] The first NMOS transistor in the second embodiment is replaced by the first CMOS transmission gate G201, the gate of the NMOS transistor is connected to the sensitive signal sense, the gate of the PMOS transistor is connected to the dual signal sense_bar complementary to the sensitive signal sense, two The signal input and output terminals are respectively connected to the input terminal in201 of the first inverter inv201 and the output terminal of the second inverter inv202 to out202;

[0086] The second NMOS transistor in the second embodiment is replaced by a second CMOS transmission gate G202, the gate of the NMOS transistor is connected to the sensitive signal sense, the gate of the PMOS transistor is connected to the dual signal sense_bar complementary to the sensitive signal sense, two The signal input and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More