Method for manufacturing vertically interconnecting carbon nanotube bundle

A technology of carbon nanotube bundles and manufacturing methods, which is applied in the field of three-dimensional stacking, can solve problems such as process incompatibility, inapplicability of carbon nanotube bundles, and difficult implementation of mature processes, so as to improve interconnection reliability and performance, and improve interconnection. Reliability and performance, the effect of mature and easy process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0060] The specific process steps are as follows:

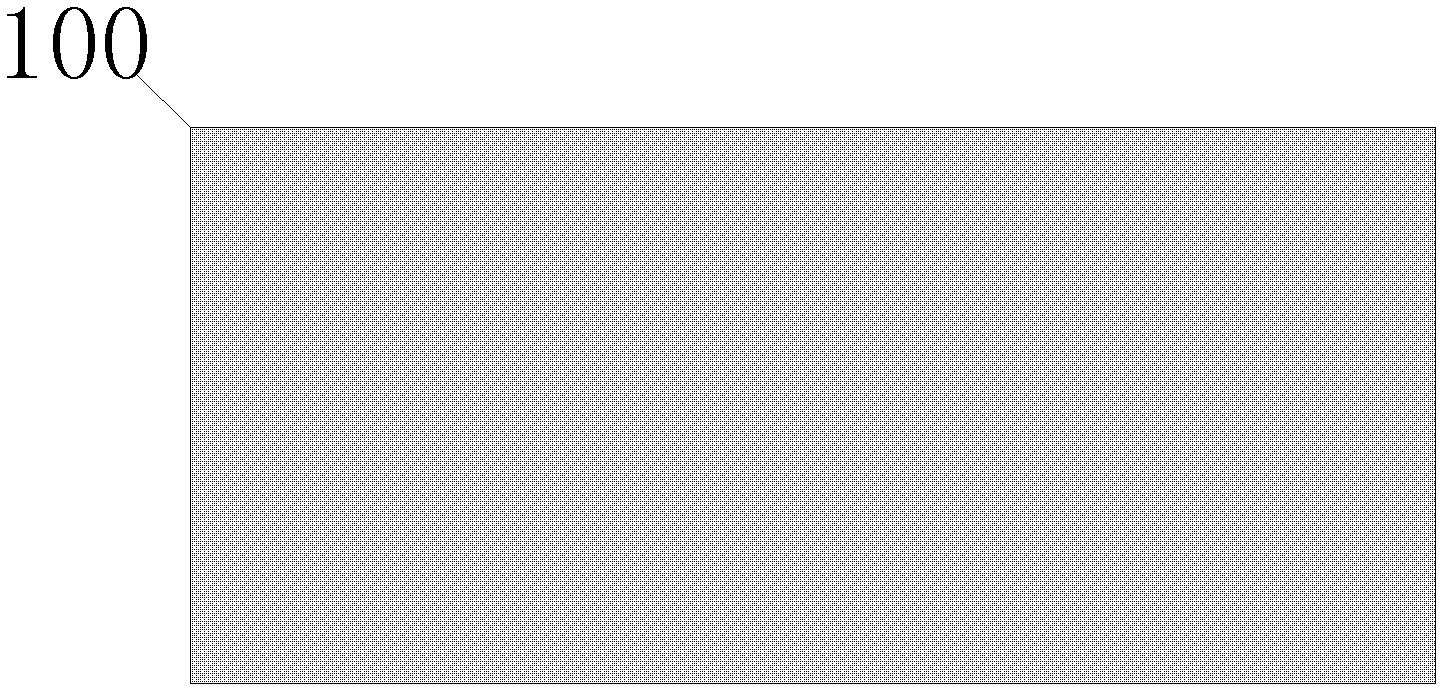

[0061] Step 01, such as figure 1 As shown, in the silicon substrate used for making carbon nanotube bundles provided in this embodiment, a 4-inch silicon wafer is selected as the upper end 100 of the silicon substrate, and the thickness of the bottom of the silicon substrate is 500 microns.

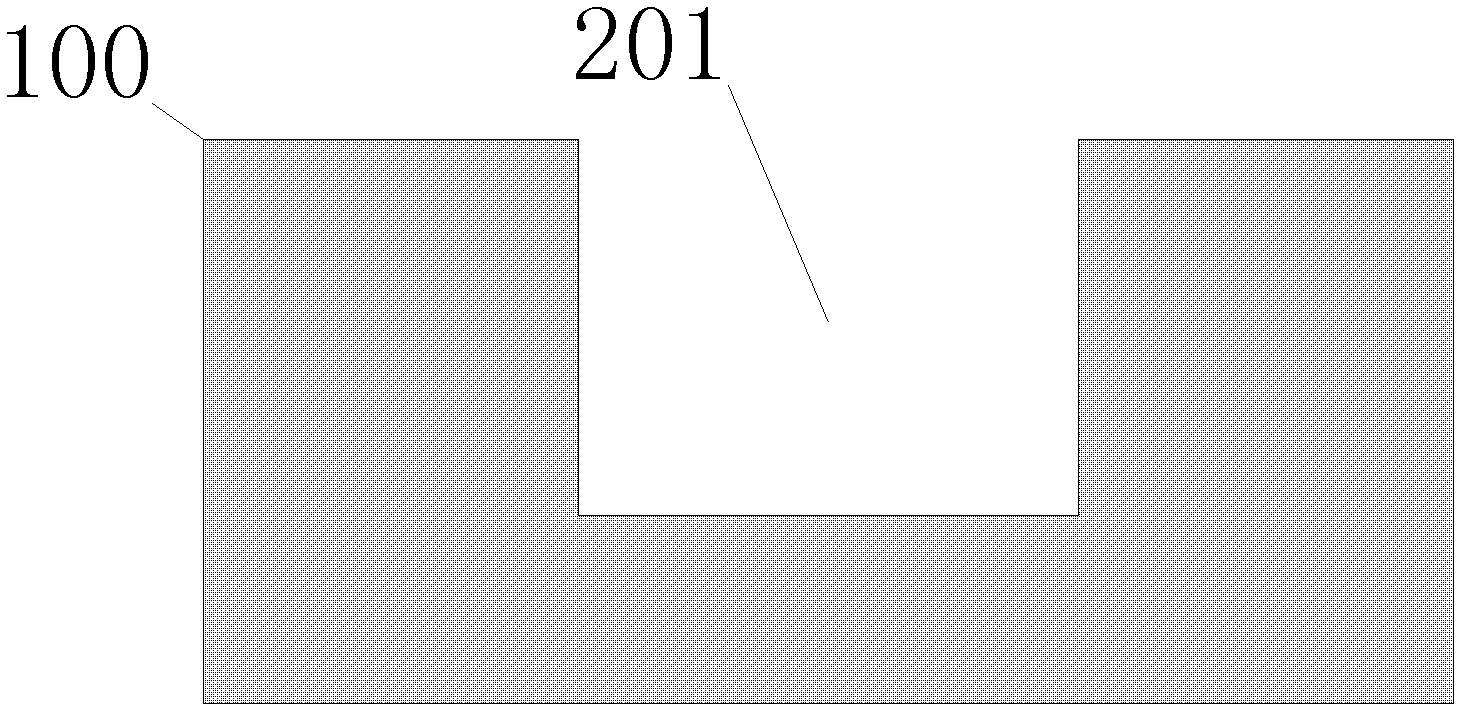

[0062] Step 02, using DRIE (Deep Reactive Ion Etching) method to make TSV blind holes 201, such as figure 1 As shown, a TSV blind via is fabricated on the silicon substrate provided in this embodiment, the size of the hole is 10 microns, and the depth of the hole is 50 microns.

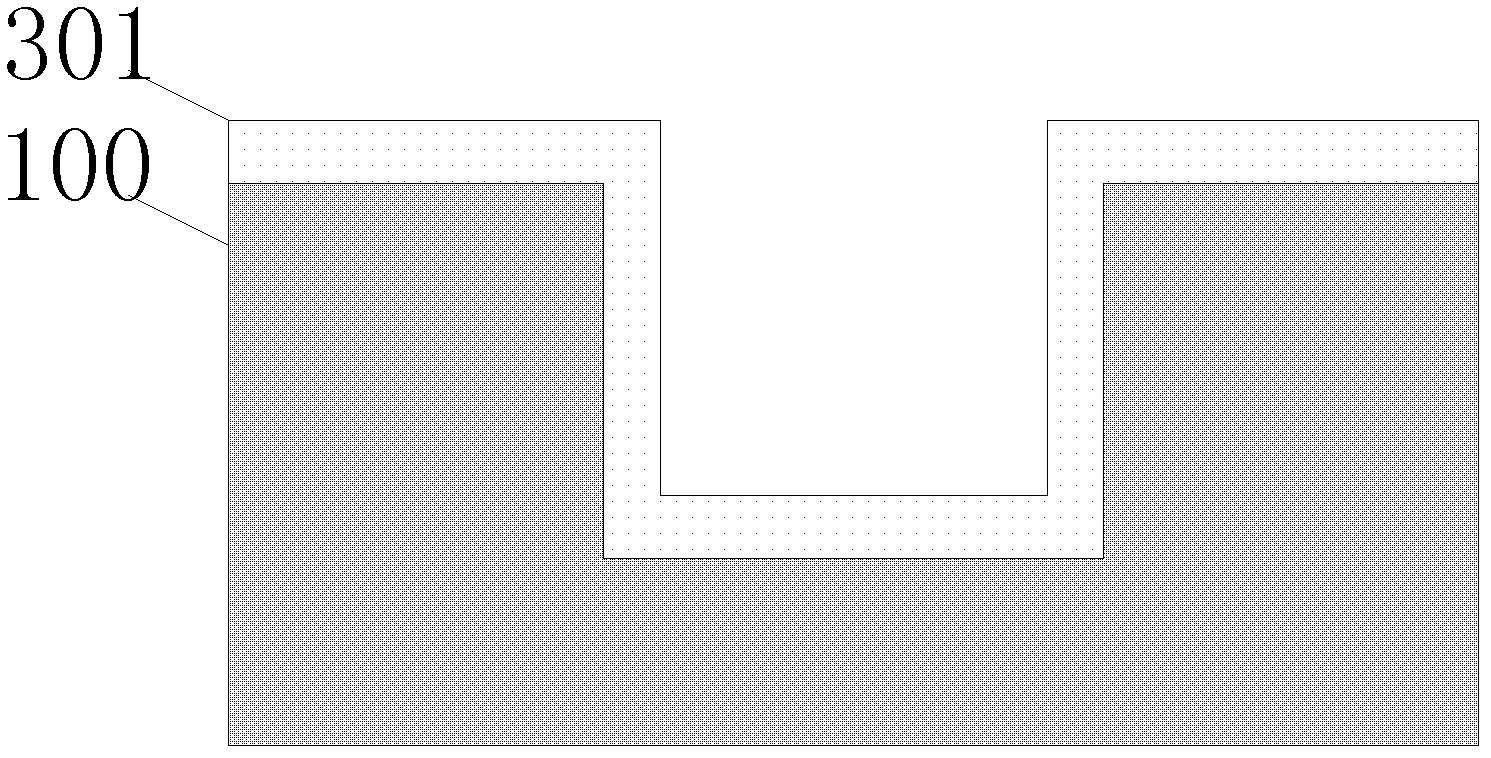

[0063] Step 03, using a thermal oxidation method to make a silicon dioxide insulating layer, such as image 3 As shown, in this embodiment, an insulating layer 301 and a barrier layer are formed in the TSV blind hole and on the upper end of the silicon substrate. The thickness of the insulating layer is 1 micron, and titanium nitride is formed on the insulatin...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More