SDLC (System Development Life Cycle) protocol bus communication testing device based on FPGA (Field-Programmable Gate Array)

A test device, bus communication technology, applied in the bus network, data exchange through path configuration, digital transmission system, etc., can solve the problems of unfavorable system integration application, inconvenient installation and operation, complicated operation, etc., and achieve small size and meet the test requirements , the effect of strong versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

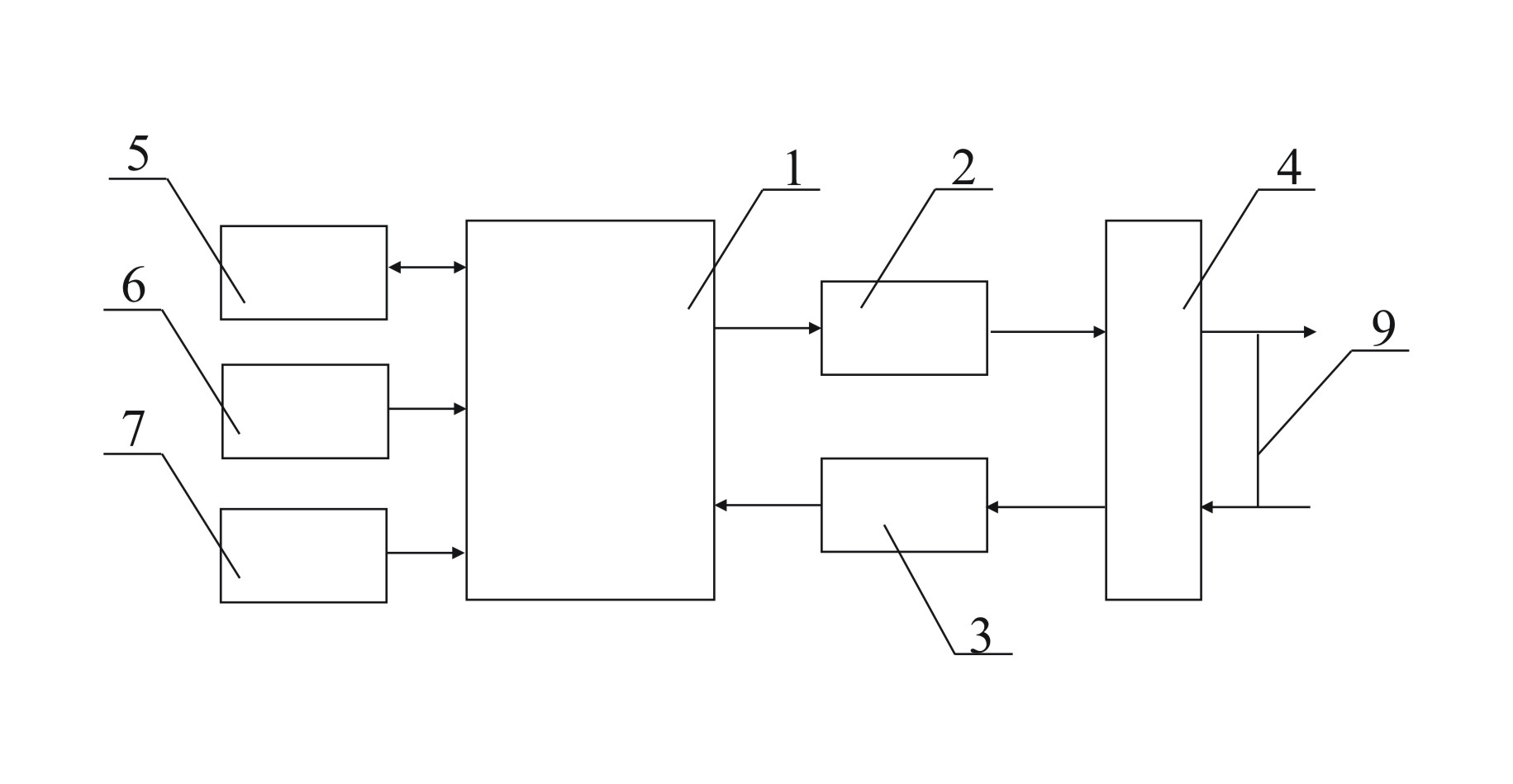

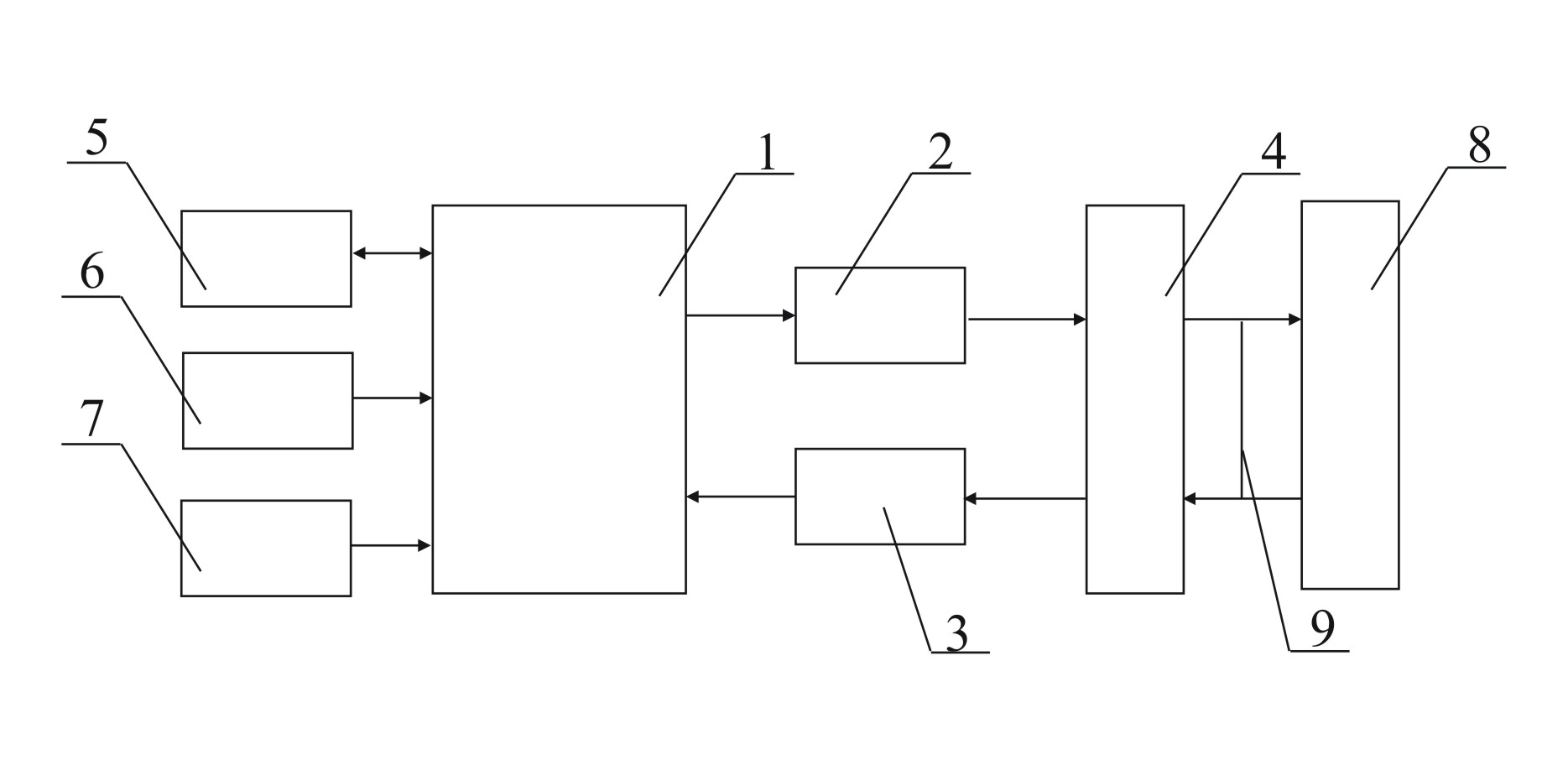

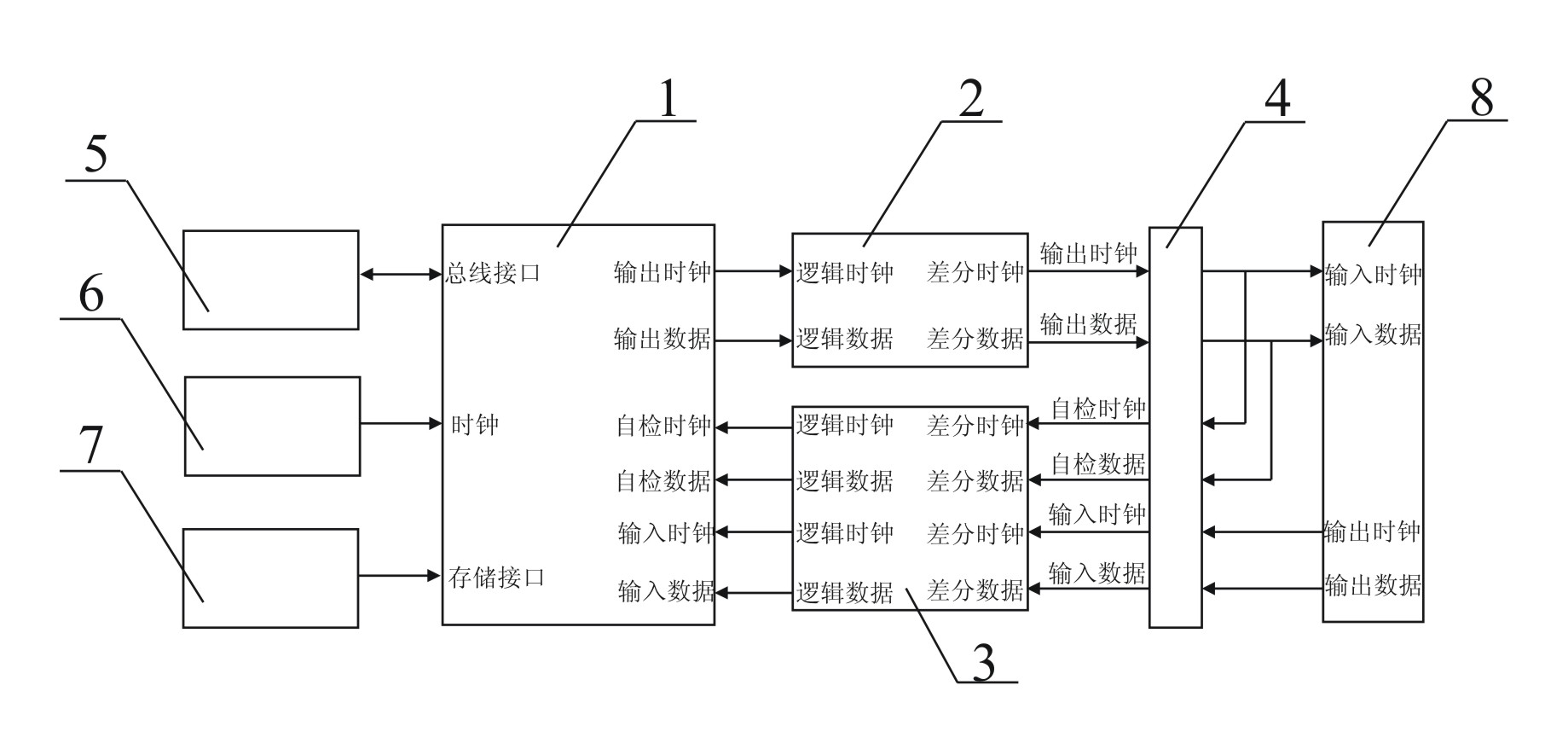

[0026] See attached figure 2 , connector 4 of the present invention is connected to the tested module 8 of the product, and FPGA test module 1 is used for the test of signal error rate and delay time; Memory 7 provides loading program for FPGA test module 1; Crystal oscillator 6, for FPGA The test module 1 provides a clock source; the differential driver 2 is used to convert the SDLC signal output by the FPGA test module 1 into a differential signal output; the differential receiver 3 is used to convert the input differential signal into a logic signal and send it to the FPGA test module 1 for processing; the computer 5 is used to send test instructions and data to the FPGA test module 1, and receive data from the FPGA test module 1 for data processing.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More