Charge pump and charge pump system

A charge pump and circuit technology, applied in the direction of conversion equipment without intermediate conversion to AC, can solve the problems affecting the transmission efficiency of the charge pump, and achieve the effect of eliminating the lining effect, improving the transmission efficiency, and improving the reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

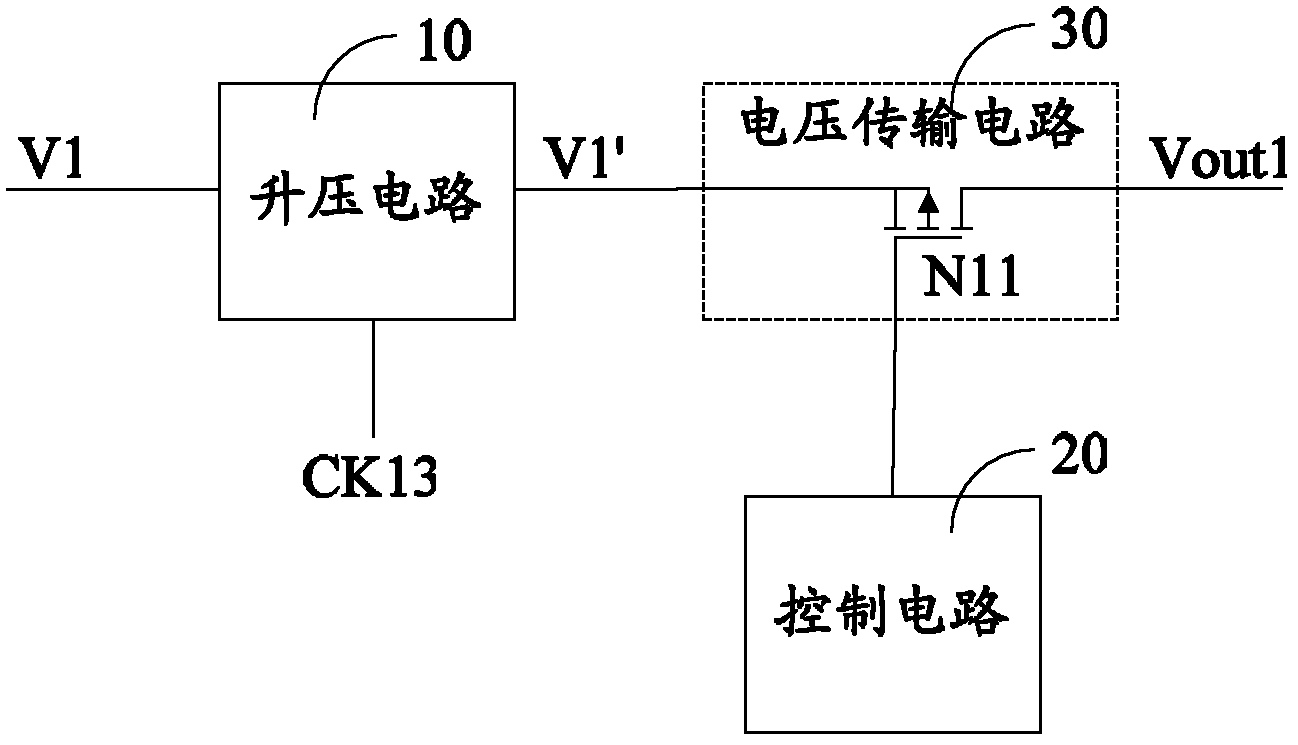

[0048] Figure 5 A schematic diagram of Embodiment 1 of the charge pump of the present invention is shown. Such as Figure 5 As shown, the charge pump includes a boost circuit 10 , a control circuit 20 and a voltage transmission circuit 30 .

[0049] The voltage transmission circuit 30 includes a first NMOS transistor N11. The source of the first NMOS transistor N11 is commonly connected to the node e with the output terminal of the booster circuit 10, the gate is commonly connected to the node f with the control circuit 20, and the drain is used as the first output terminal of the charge pump , for the output voltage Vout1.

[0050] The boost circuit 10 includes: a first capacitor C11 and an inverter INV1. One end of the first capacitor C11 is connected to the source of the first NMOS transistor N11, that is, the node e, and the other end is connected to the output end of the inverter INV1, and the input end of the inverter INV1 receives the first Control signal CK13.

...

Embodiment 2

[0072] Figure 6 A schematic diagram of Embodiment 2 of the charge pump of the present invention is shown. refer to Figure 6, compared with Embodiment 1, the charge pump of this embodiment further includes a third NMOS transistor N13.

[0073] The source of the third NMOS transistor N13 is connected to the source of the first NMOS transistor N11, the gate is connected to the drain of the first NMOS transistor N11, and the drain is connected to the gate of the first NMOS transistor N11 and receives the first NMOS transistor N11. Two input voltage V2.

[0074] Moreover, in this embodiment, the third NMOS transistor N13 includes a P-type substrate, an N-type well region is included in the P-type substrate, a P-type well region is included in the N-type well region, and a P-type well region is included in the N-type well region. The P-type well region includes an N-type doped source region and a drain region; the substrate of the third NMOS transistor is connected to the sourc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More