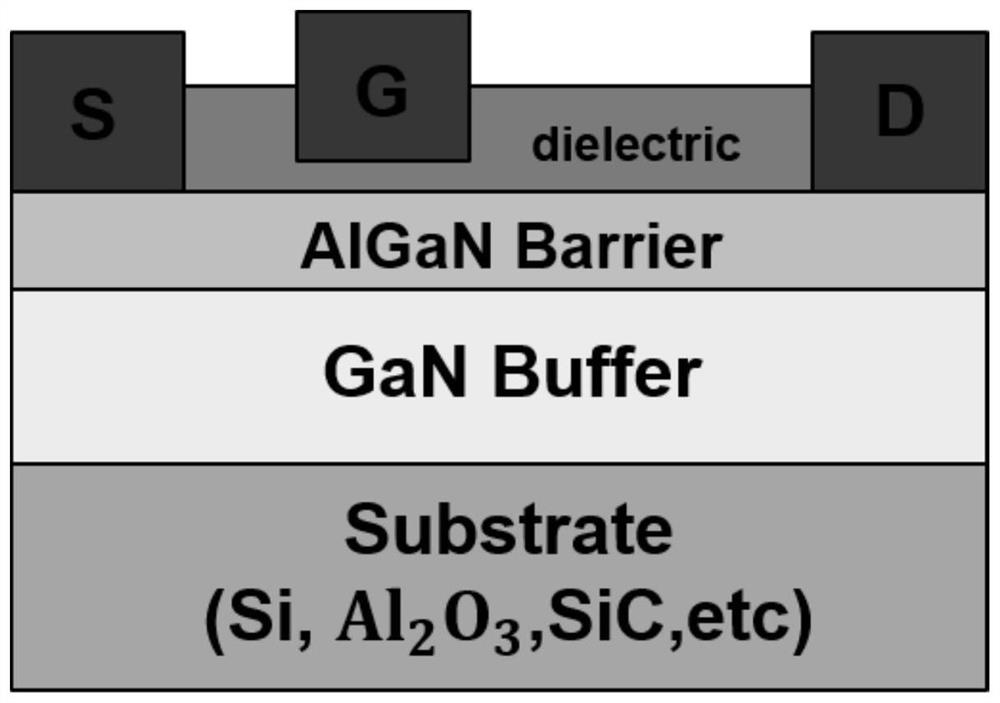

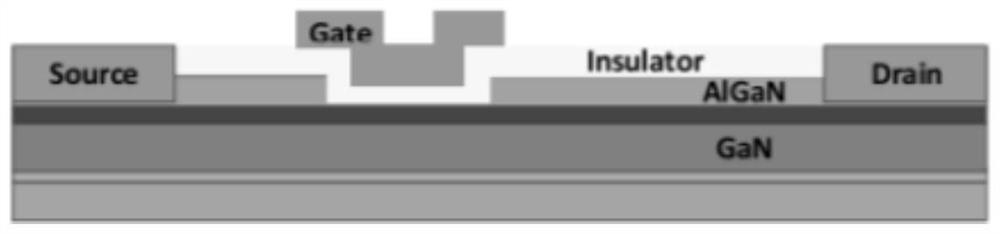

Preparation method of SOI-based concave gate enhanced GaN power switch device

A power switching device, enhanced technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as lattice mismatch and thermal mismatch, and achieve low gate leakage current and breakdown voltage The effect of improving and suppressing the current collapse phenomenon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

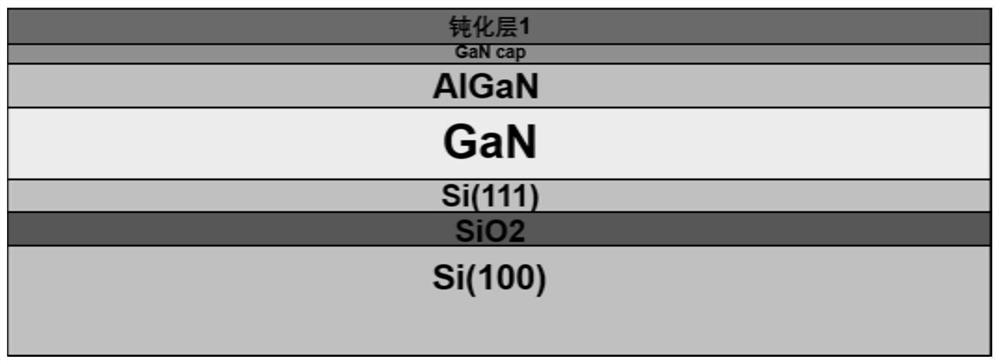

[0049] This embodiment provides a method for fabricating an SOI-based concave gate enhanced GaN power switching device, and the specific steps are as follows:

[0050] (1) if image 3 As shown, 100nmSi was deposited on the surface of SOI-based GaN epitaxial layer by LPCVD technology 3 N 4 As the first passivation layer, the SOI-based epitaxial layer includes from bottom to top: Si(100), SiO 2 , Si(111), GaN (including transition layer and channel layer), AlGaN, GaN cap layer;

[0051] (2) if Figure 4 As shown, the photoresist is spin-coated, and the photolithography is developed to determine the source and drain regions. After development, RIE technology is used to etch the Si in the source and drain regions. 3 N 4 , the etching atmosphere is SF 6 、C 4 f 8 Wait. Then use the magnetron sputtering method to grow Ti(20nm) / Al(100nm) / Ti(20nm) / TiN(60nm) metal stacks as the source and drain metal, use the lift-off method to strip off the remaining metal and then anneal to f...

Embodiment 2

[0061] This embodiment provides a method for fabricating an SOI-based concave gate enhanced GaN power switching device, and the specific steps are as follows:

[0062] (1) if image 3 As shown, 100nmSi was deposited on the surface of SOI-based GaN epitaxial layer by LPCVD technology 3 N 4 As the first passivation layer, the SOI-based epitaxial layer includes from bottom to top: Si(100), SiO 2 , Si(111), GaN (including transition layer and channel layer), AlGaN, GaN cap layer;

[0063] (2) if Figure 4 As shown, the photoresist is spin-coated, and the photolithography is developed to determine the source and drain regions. After development, RIE technology is used to etch the Si in the source and drain regions. 3 N 4 , the etching atmosphere is SF 6 、C 4 f 8 Wait. Then use the magnetron sputtering method to grow Ti(20nm) / Al(100nm) / W(60nm) metal stack as the source and drain metal, use the lift-off method to strip off the remaining metal and then anneal to form an ohmic...

Embodiment 3

[0073] This embodiment provides a method for fabricating an SOI-based concave gate enhanced GaN power switching device, and the specific steps are as follows:

[0074] (1) if image 3 As shown, 100nmSi was deposited on the surface of SOI-based GaN epitaxial layer by LPCVD technology 3 N 4 As the first passivation layer, the SOI-based epitaxial layer includes from bottom to top: Si(100), SiO 2 , Si(111), GaN (including transition layer and channel layer), AlGaN, GaN cap layer;

[0075] (2) if Figure 4 As shown, the photoresist is spin-coated, and the photolithography is developed to determine the source and drain regions. After development, RIE technology is used to etch the Si in the source and drain regions. 3 N 4 , the etching atmosphere is SF 6 、C 4 f 8 Wait. Then use the magnetron sputtering method to grow Ti(20nm) / Al(100nm) / Ti(20nm) / TiN(60nm) metal stacks as the source and drain metal, use the lift-off method to strip off the remaining metal and then anneal to f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More