Array substrate and manufacturing method thereof, liquid crystal panel, and display device

An array substrate and substrate technology, applied in the field of liquid crystal panels and display devices, array substrates and manufacturing methods thereof, can solve problems such as easy peeling, diffusion, and affecting the conduction performance of TFT structures, and achieve the effect of increasing adhesion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

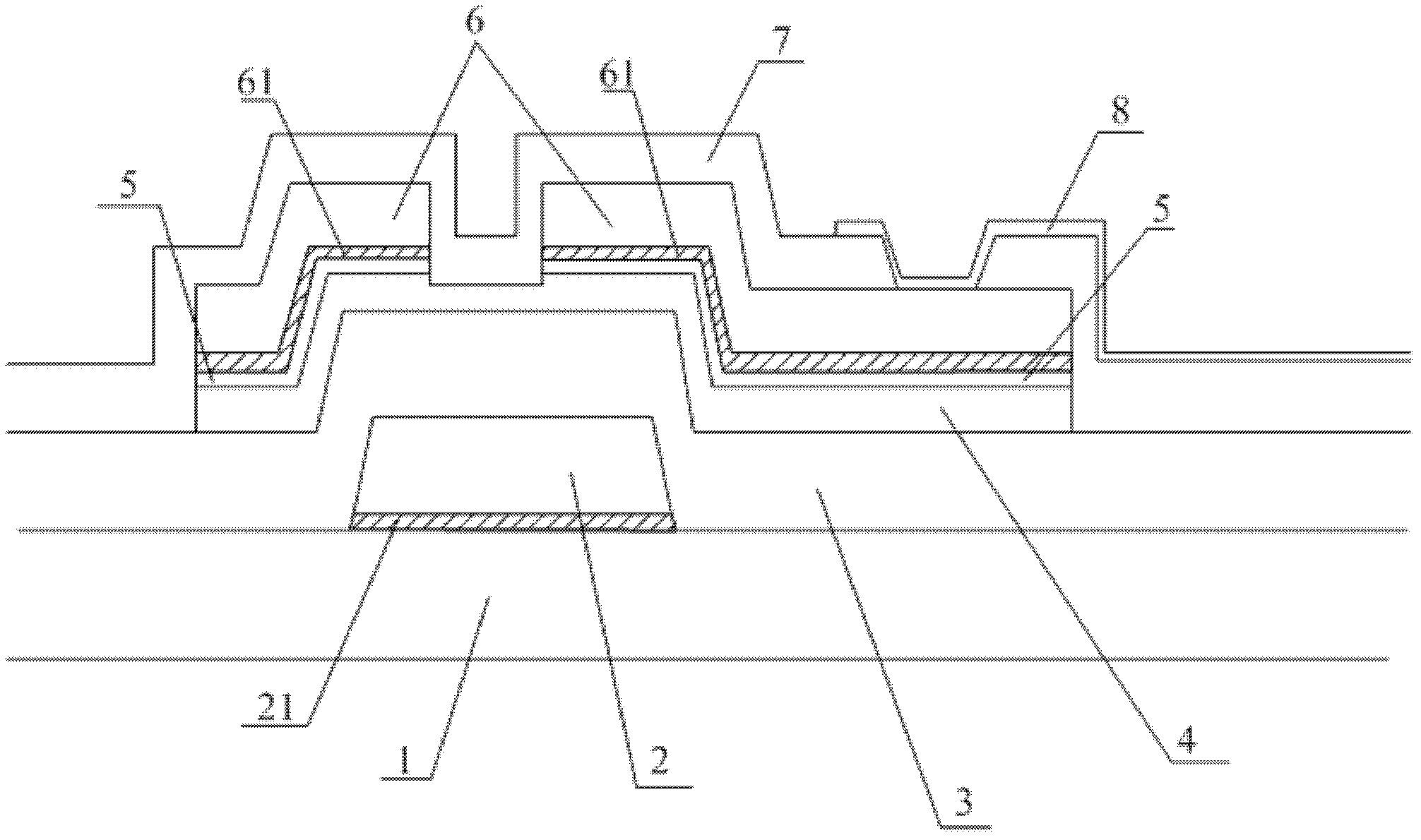

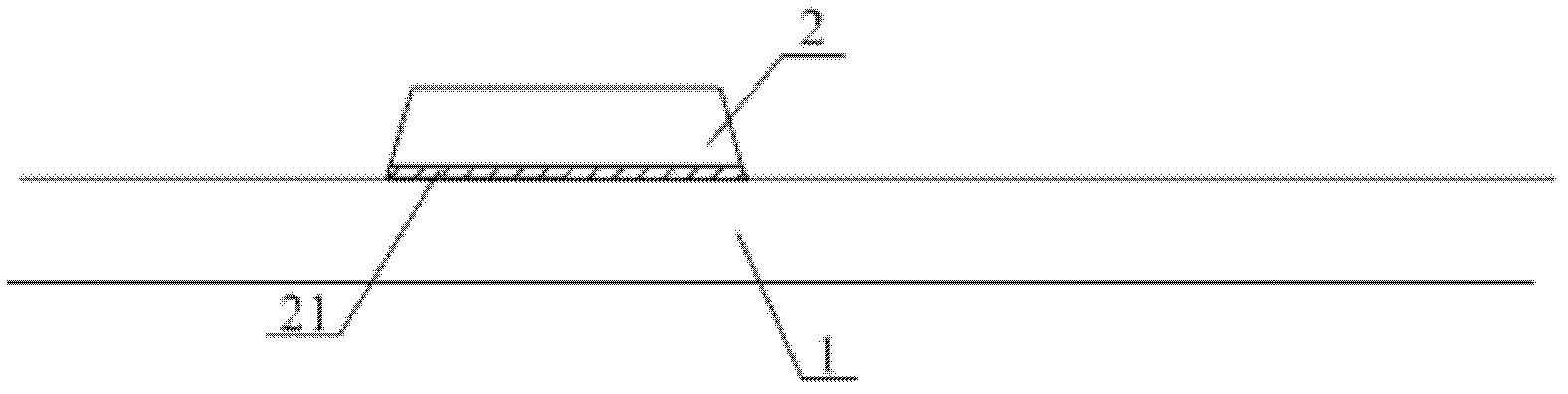

[0046] like figure 1 As shown, an array substrate provided by an embodiment of the present invention includes a substrate 1 and a gate metal layer 2, a gate insulating layer 3, a semiconductor layer 4, an ohmic contact layer 5, and a source / drain metal layer 6 formed on the substrate 1. , and the passivation layer 7 and the pixel electrode 8; wherein, a first isolation buffer layer 21 is formed between the gate metal layer 2 and the substrate 1, and a second isolation buffer layer 21 is formed between the ohmic contact layer 5 and the source / drain metal layer 6 Isolation buffer layer 61;

[0047] Wherein, the substrate 1 may be, but not limited to, a glass substrate or a quartz substrate;

[0048] The gate metal layer 2 and the source / drain metal layer 6 take metal Cu as an example in this embodiment;

[0049] The gate insulating layer 3 is made of Si x N y (silicon nitride) or Si x o y (silicon oxide) and other silicon series materials;

[0050] The semiconductor layer 4...

Embodiment 2

[0076] On the basis of the array substrate provided in Embodiment 1, this embodiment further improves it to obtain another array substrate structure. specifically,

[0077] like image 3 As shown, another array substrate provided in this embodiment includes a substrate 1 and a gate metal layer 2, a gate insulating layer 3, a semiconductor layer 4, an ohmic contact layer 5 and a source / drain metal layer 6 formed on the substrate 1. , and the passivation layer 7 and the pixel electrode 8; wherein, a first isolation buffer layer 21 is formed between the gate metal layer 2 and the substrate 1, and a second isolation buffer layer 21 is formed between the ohmic contact layer 5 and the source / drain metal layer 6 Isolation buffer layer 61;

[0078] In addition, a third isolation buffer layer 22 is formed between the gate metal layer 2 and the gate insulating layer 3 .

[0079] Wherein, the gate metal layer 2 and the source / drain metal layer 6 are metal Cu in this embodiment;

[00...

Embodiment 3

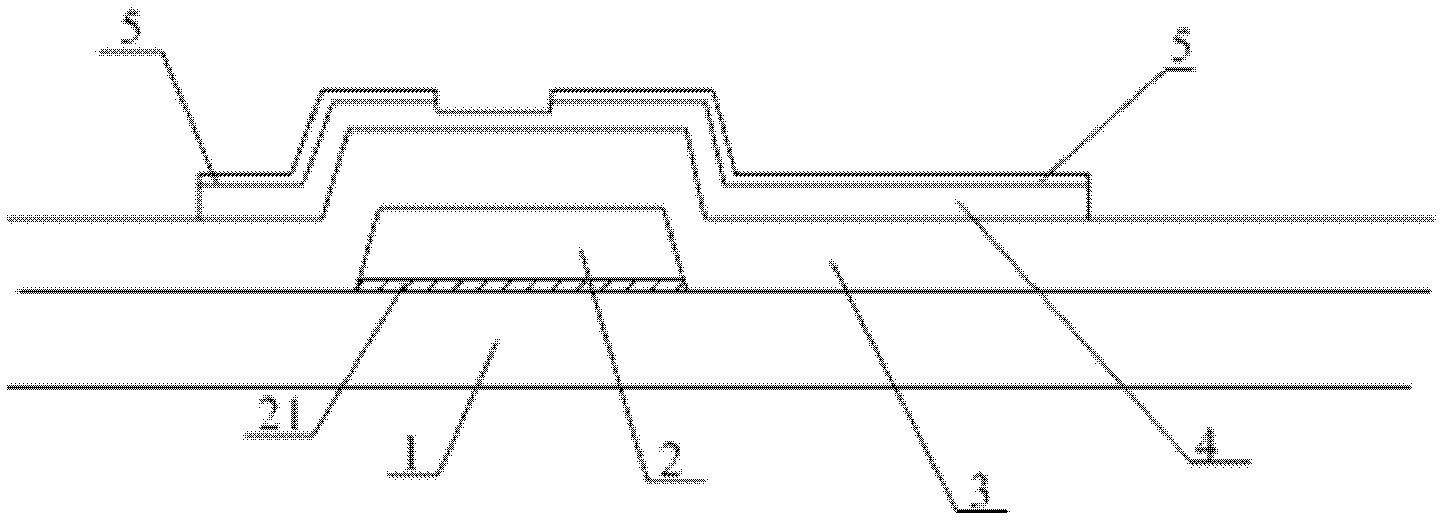

[0087] On the basis of the array substrate provided in Embodiment 1, this embodiment further improves it to obtain another array substrate structure. specifically,

[0088] like Figure 4 As shown, another array substrate provided in this embodiment includes a substrate 1 and a gate metal layer 2, a gate insulating layer 3, a semiconductor layer 4, an ohmic contact layer 5 and a source / drain metal layer 6 formed on the substrate 1. , and the passivation layer 7 and the pixel electrode 8; wherein, a first isolation buffer layer 21 is formed between the gate metal layer 2 and the substrate 1, and a second isolation buffer layer 21 is formed between the ohmic contact layer 5 and the source / drain metal layer 6 Isolation buffer layer 61;

[0089] In addition, a fourth isolation buffer layer 62 is formed between the source / drain metal layer 6 and the passivation layer 7 .

[0090] Wherein, the gate metal layer 2 and the source / drain metal layer 6 are metal Cu in this embodiment; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More