Through-silicon-vias structure and formation method thereof

A through-silicon via and polysilicon technology, which is applied to semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of the reliability drop of the through-silicon via structure, improve the filling effect and avoid void defects Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

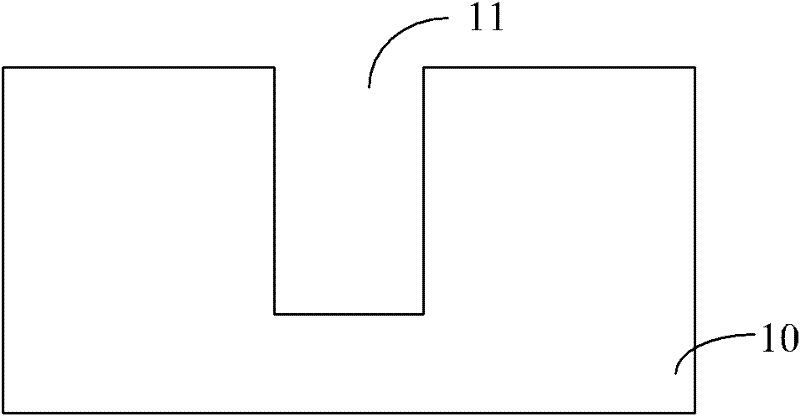

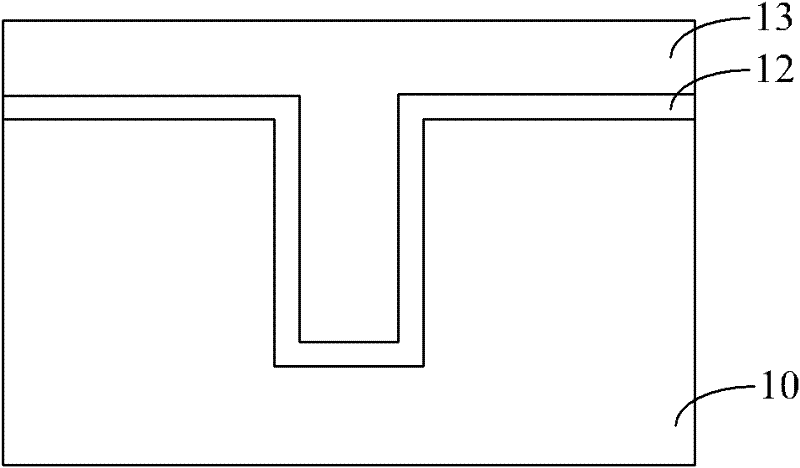

[0048] The method of forming through silicon via structure in the prior art is mainly based on the copper interconnection process. As the density of the through silicon via structure increases, its aspect ratio increases correspondingly, resulting in a copper diffusion barrier and copper seed crystals. The layer may not completely cover the inner surface of the through hole, thereby causing void defects in the connecting nail formed after electroplating and filling, resulting in a decrease in the reliability of the through silicon via structure, and even an open circuit problem.

[0049] In the method for forming the through silicon via structure of the embodiment of the present invention, an opening with a moderate aspect ratio is first formed on the upper surface of the semiconductor substrate, and the first connecting pin is filled in it. Generally, the width of the opening is A more moderate value is selected to improve the filling effect of the first connecting nail and avoid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More