Low dropout regulator

A low-dropout linear, voltage-stabilizing circuit technology, applied in the direction of adjusting electrical variables, control/regulation systems, instruments, etc., can solve the problems of increasing the difficulty of system compensation, reducing system bandwidth, slowing down the charging and discharging speed of parasitic capacitance, etc., to achieve Reduce the transmission delay, the effect of good output linearity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

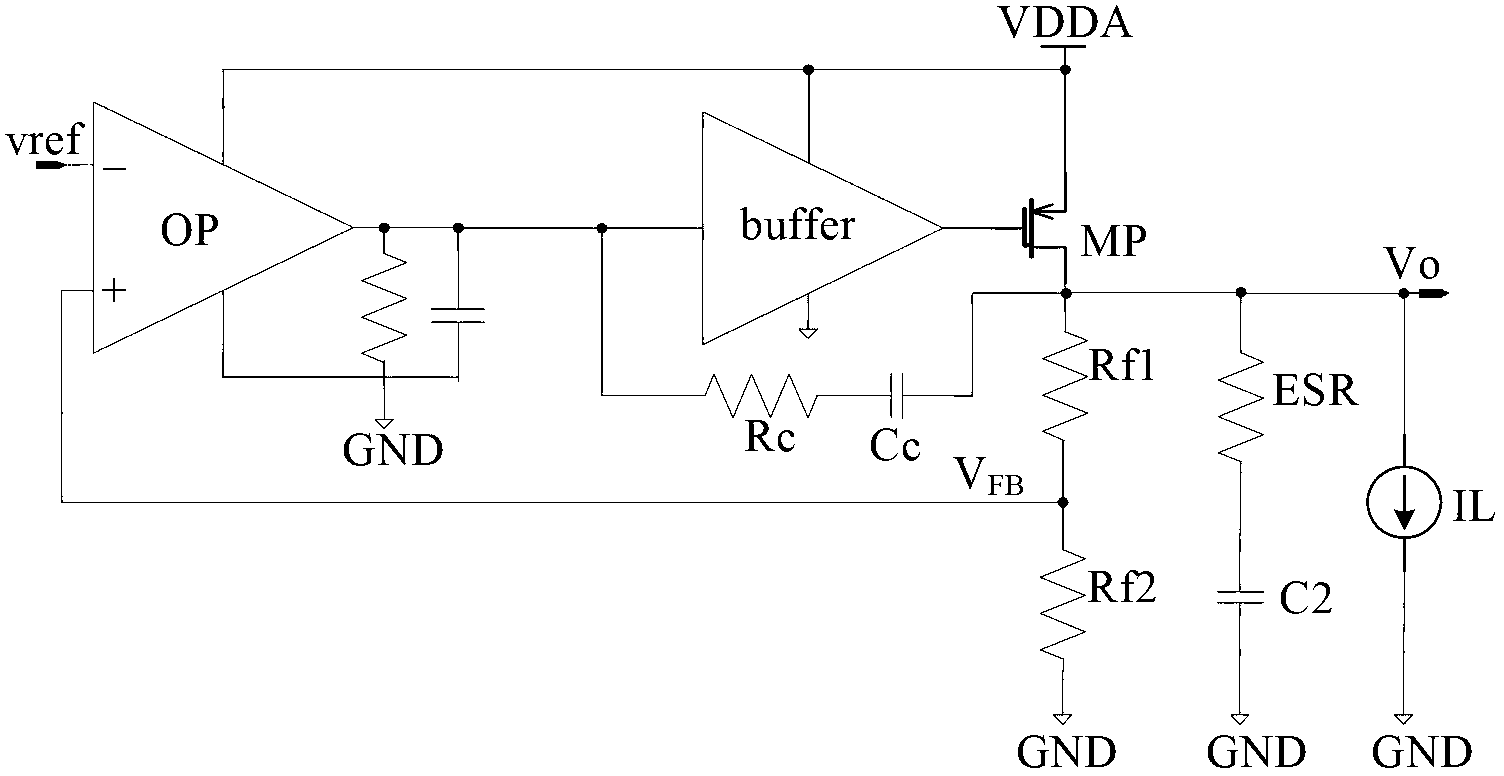

[0048] As mentioned in the background art, the traditional LDO circuit has defects such as slow transient response speed and low output voltage accuracy.

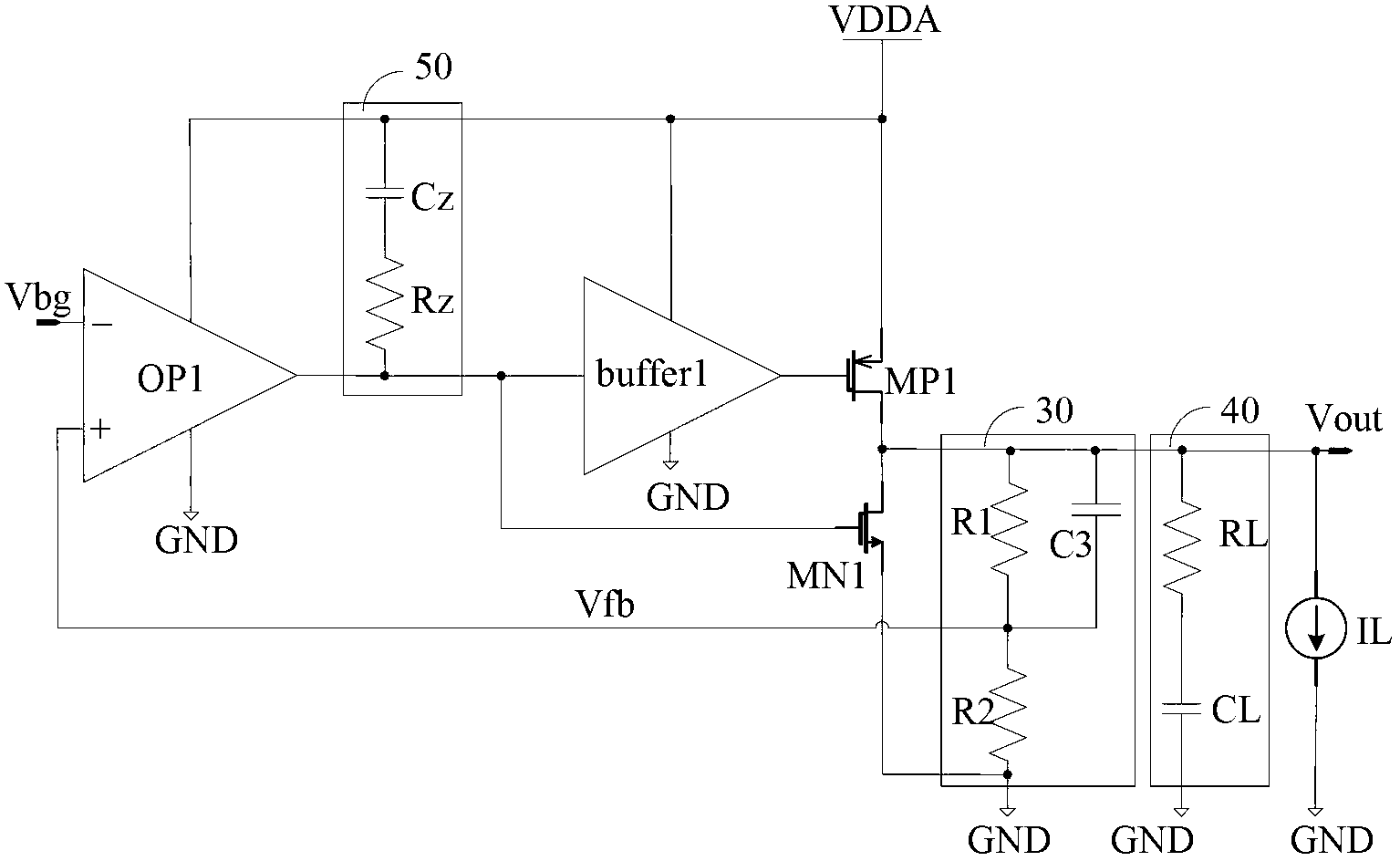

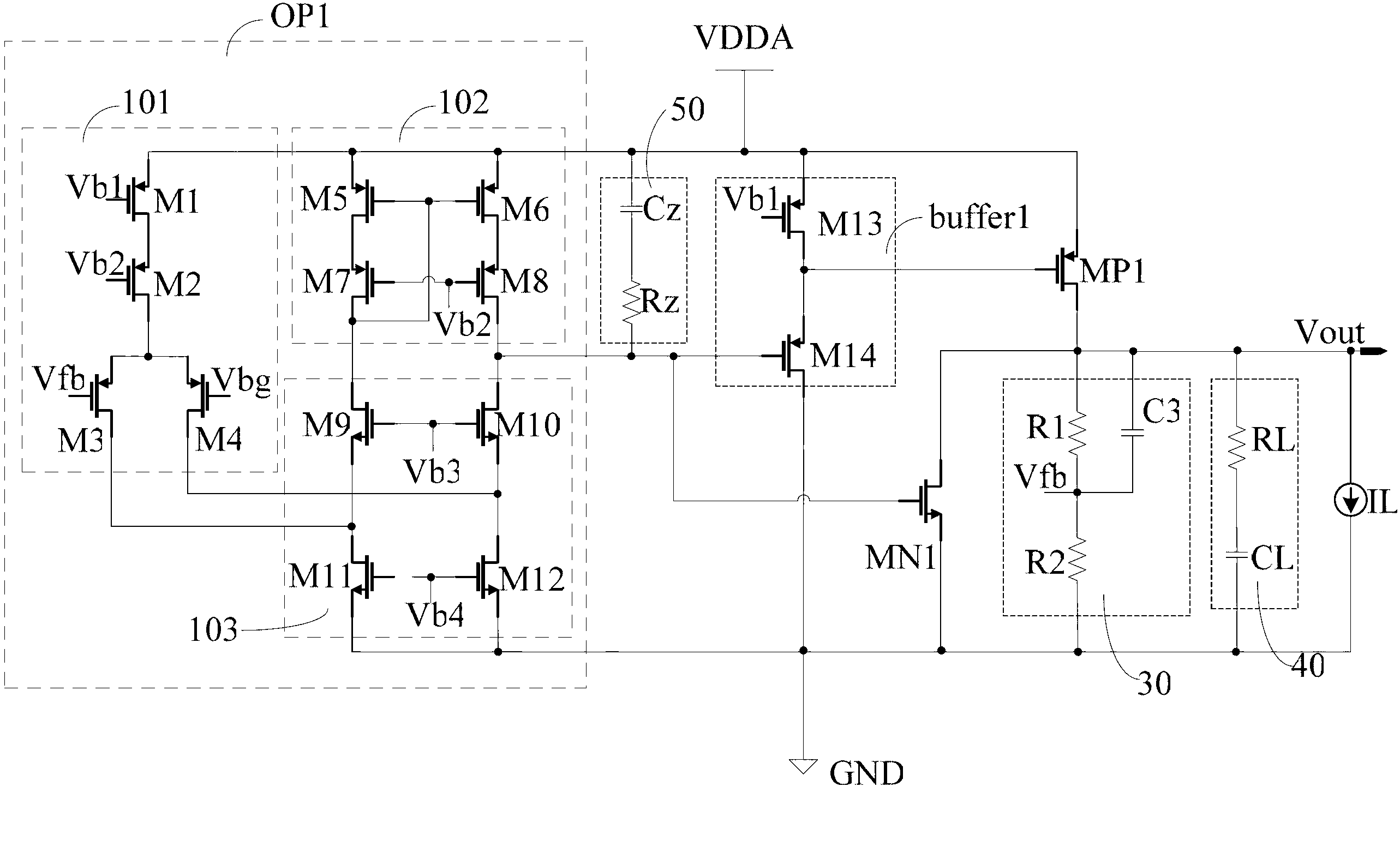

[0049] An NMOS push-pull transistor is added to the low-dropout linear regulator circuit of the technical solution of the present invention, the source of the NMOS push-pull transistor is grounded, the gate is connected to the output end of the error amplifier, and the drain is connected to the output end of the LDO circuit, that is PMOS adjusts the drain of the transistor; and the size of the NMOS push-pull transistor can be made very small, so the parasitic capacitance generated by it is very small, so that it can respond quickly, forming a fast response loop, thus making up for the large The size of the PMOS adjusts the defect of the slow response of the transistor, which greatly improves the transient response speed of the circuit.

[0050] The parasitic capacitance of the NMOS push-pull transistor is very small, so whe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More