Wafer level chip scale package (WLCSP) multiple chip stackable packaging piece based on solder paste layers and packaging method thereof

A packaging method and multi-chip technology, applied in the direction of electrical components, semiconductor devices, electric solid devices, etc., can solve the problems of high precision requirements for electroplating and photolithography, complicated WLCSP production process, and high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

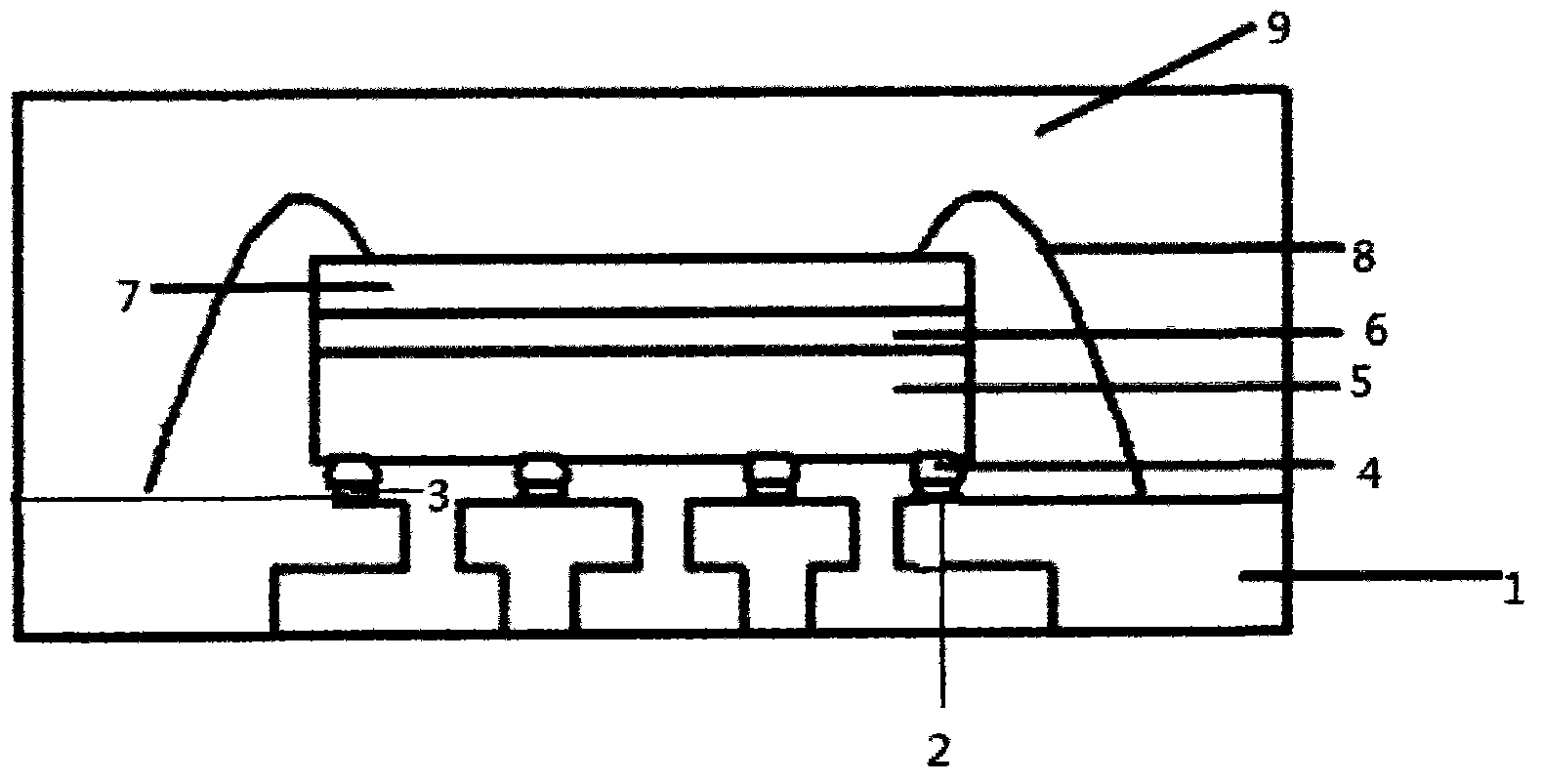

[0041] A packaging method of a WLCSP multi-chip stacked package based on a solder paste layer can be carried out according to the following steps:

[0042] The first step, wafer thinning;

[0043] The thickness of wafer thinning is 50μm, and the roughness Ra is 0.10mm;

[0044] The second step is to plate metal bumps;

[0045] Plating 2um metal bumps 4 on the surface of metal Au in the chip nip area on the entire wafer;

[0046] The third step, scribing;

[0047] For wafers with a thickness below 150 μm, use a double-knife dicing machine and its process;

[0048] The fourth step is to tin-plate the corresponding area of the frame;

[0049] A layer of 2um solder paste layer is plated on the corresponding area of PAD on pin 1 in the frame;

[0050] The fifth step, on the core

[0051] When the chip is installed, the lower IC chip 7 is turned upside down, and the bumps of the chip are welded to the frame pins by using the Flip-Chip process; the upper IC chip 5 is bonded...

Embodiment 2

[0059] A packaging method of a WLCSP multi-chip stacked package based on a solder paste layer can be carried out according to the following steps:

[0060] The first step, wafer thinning;

[0061] The thickness of wafer thinning is 130μm, and the roughness Ra is 0.20mm;

[0062] The second step is to plate metal bumps;

[0063]Plating 25um metal bumps 4 on the metal Cu surface of the chip nip area on the entire wafer;

[0064] The third step, scribing;

[0065] For wafers with a thickness below 150 μm, use a double-knife dicing machine and its process;

[0066] The fourth step is to tin-plate the corresponding area of the frame;

[0067] Plate a layer of 25um solder paste layer on the corresponding area of PAD on pin 1 in the frame;

[0068] The fifth step, on the core

[0069] When the chip is installed, the lower IC chip 7 is turned upside down, and the bumps of the chip are welded to the frame pins by using the Flip-Chip process; the upper IC chip 5 is bonded to t...

Embodiment 3

[0077] A packaging method of a WLCSP multi-chip stacked package based on a solder paste layer can be carried out according to the following steps:

[0078] The first step, wafer thinning;

[0079] The thickness of wafer thinning is 200μm, and the roughness Ra is 0.30mm;

[0080] The second step is to plate metal bumps;

[0081] Plating 50um metal bumps 4 on the surface of metal Au or Cu in the chip nip area on the entire wafer;

[0082] The third step, scribing;

[0083] Wafers above 150μm adopt ordinary dicing process;

[0084] The fourth step is to tin-plate the corresponding area of the frame;

[0085] Plate a layer of 50um solder paste layer on the corresponding area of PAD on pin 1 in the frame;

[0086] The fifth step, on the core

[0087] When the chip is installed, the lower IC chip 7 is turned upside down, and the bumps of the chip are welded to the frame pins by using the Flip-Chip process; the upper IC chip 5 is bonded to the lower chip 7 with the adhesive...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More