Multi-channel high-speed digital-to-analogue converter (DAC) synchronization method

An implementation method and multi-channel technology, applied in the field of multi-channel high-speed DAC synchronization and phase synchronization control, can solve the problems of no way to synchronize or control the timing, low clock speed, no phase control of the frequency divider, etc., to achieve timing Fully synchronized and controllable, improve work efficiency, and expand the effect of signal output bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

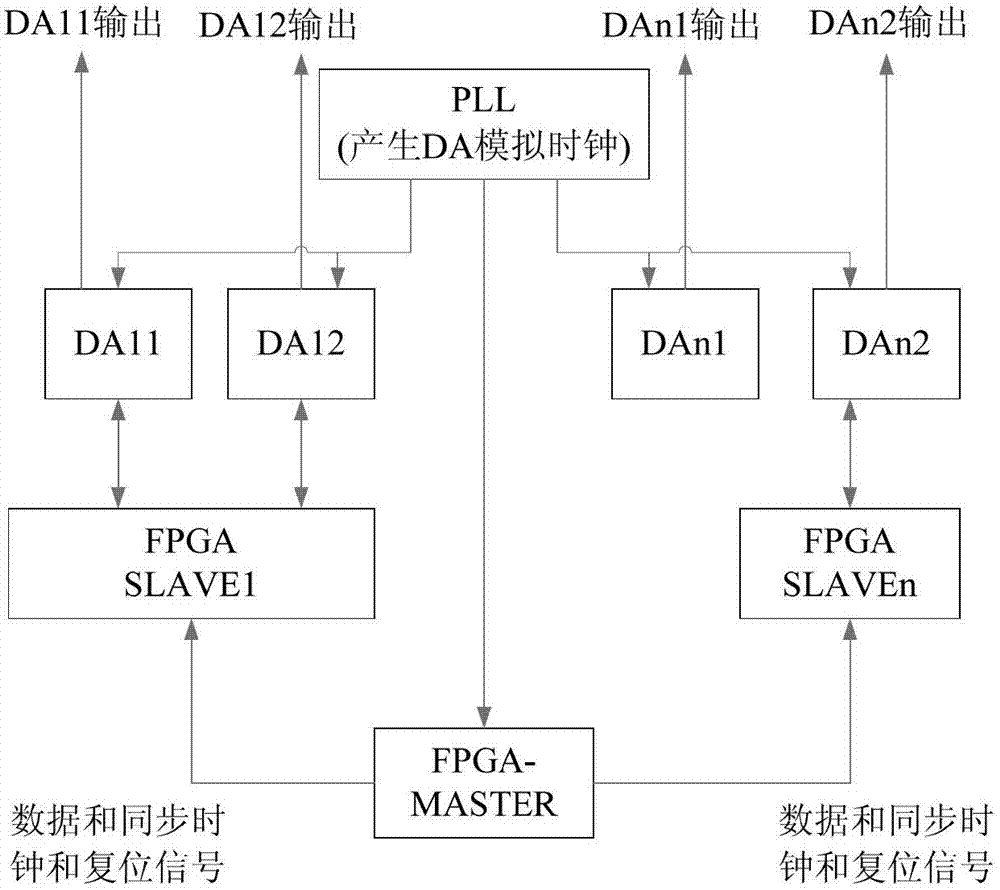

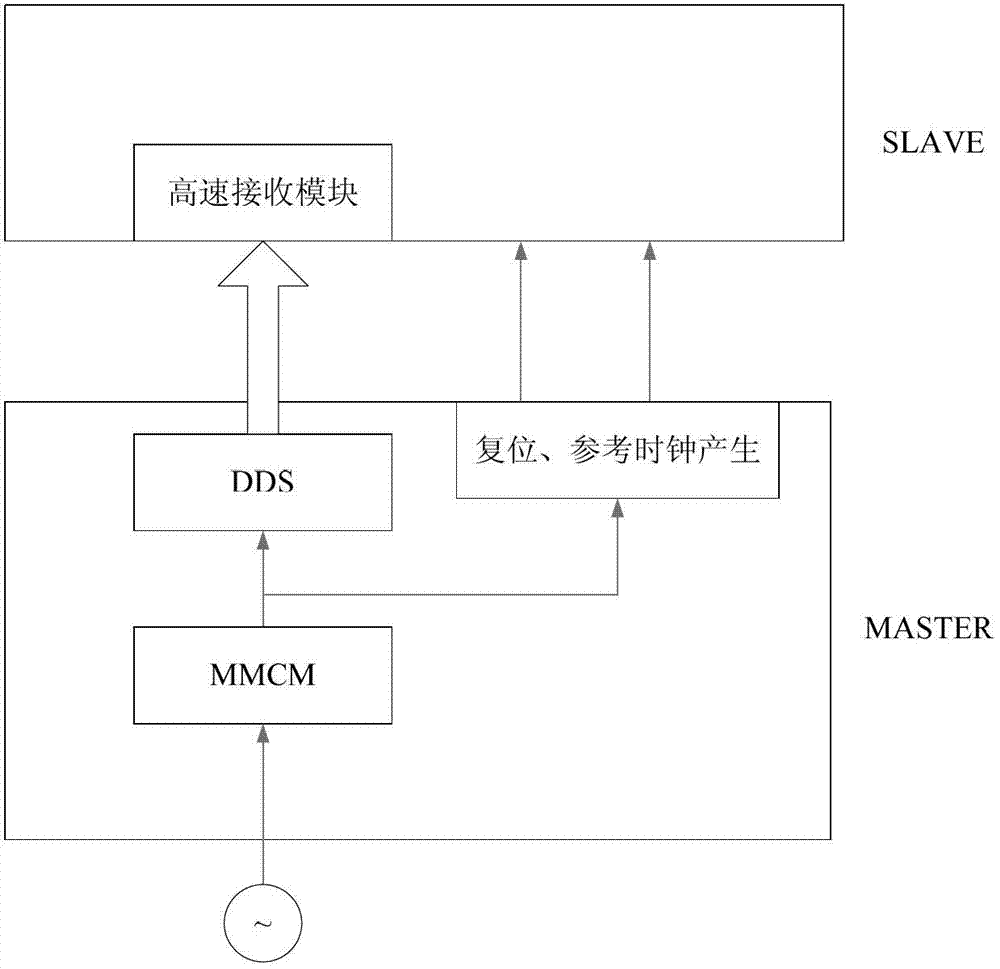

[0027] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

[0028] In the description of the present invention, unless otherwise specified and limited, it should be noted that the terms "installation", "connection" and "connection" should be understood in a broad sense, for example, it can be mechanical connection or electrical connection, or two The internal communication of each element may be directly connected or indirectly connected through an intermediary. Those skilled in the art can understand the specific meanings of the above terms according to specific situations.

[0029] The present ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More