Patents

Literature

33results about How to "Achieving Phase Synchronization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

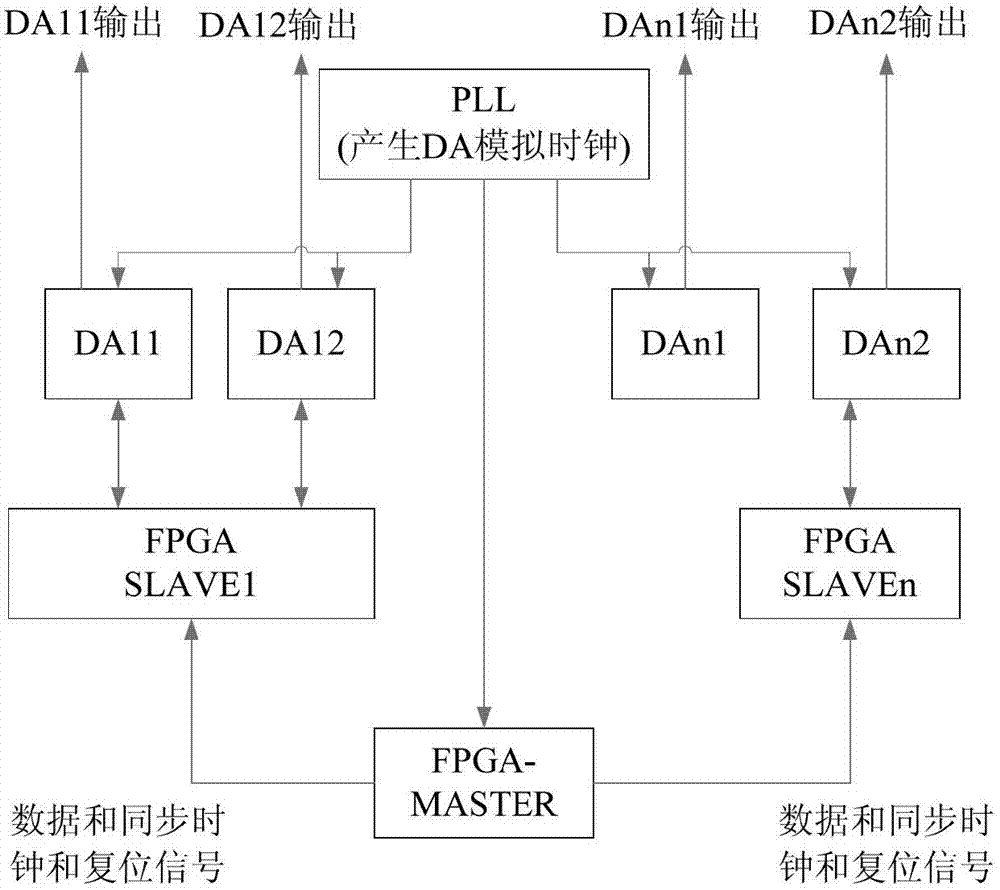

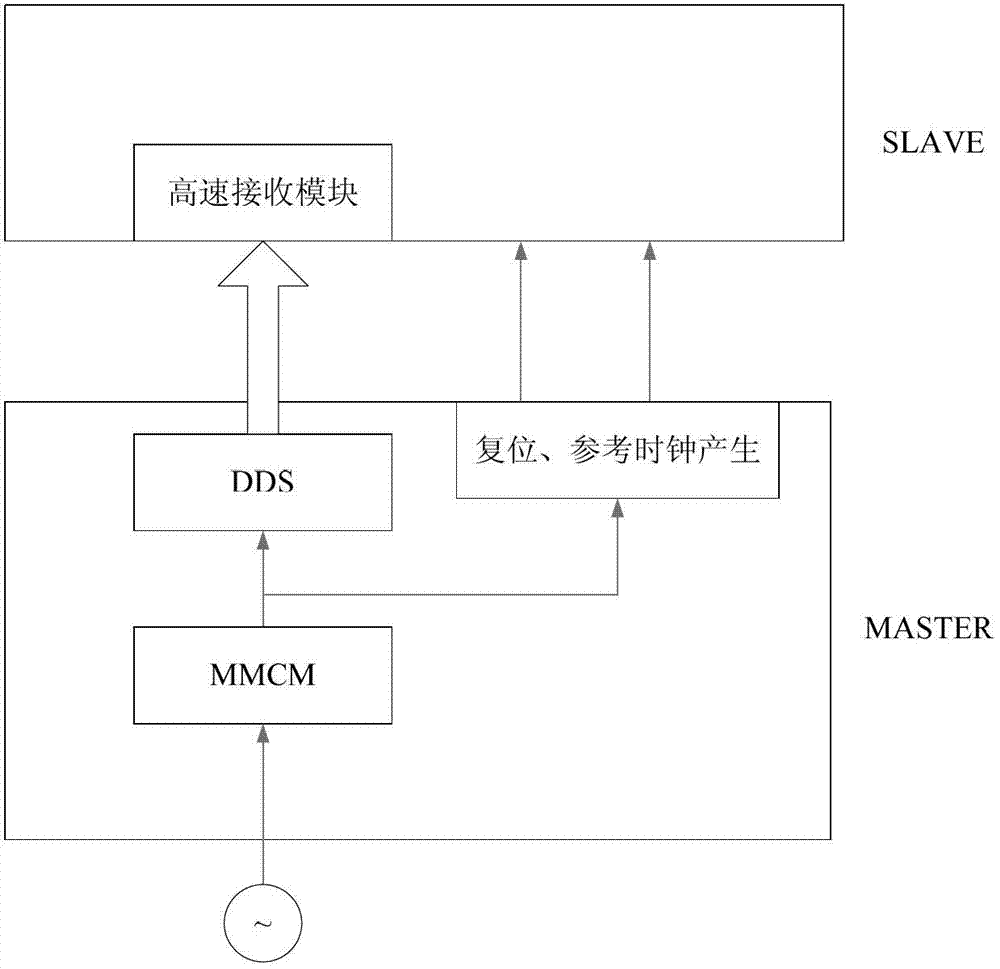

Multi-channel high-speed digital-to-analogue converter (DAC) synchronization method

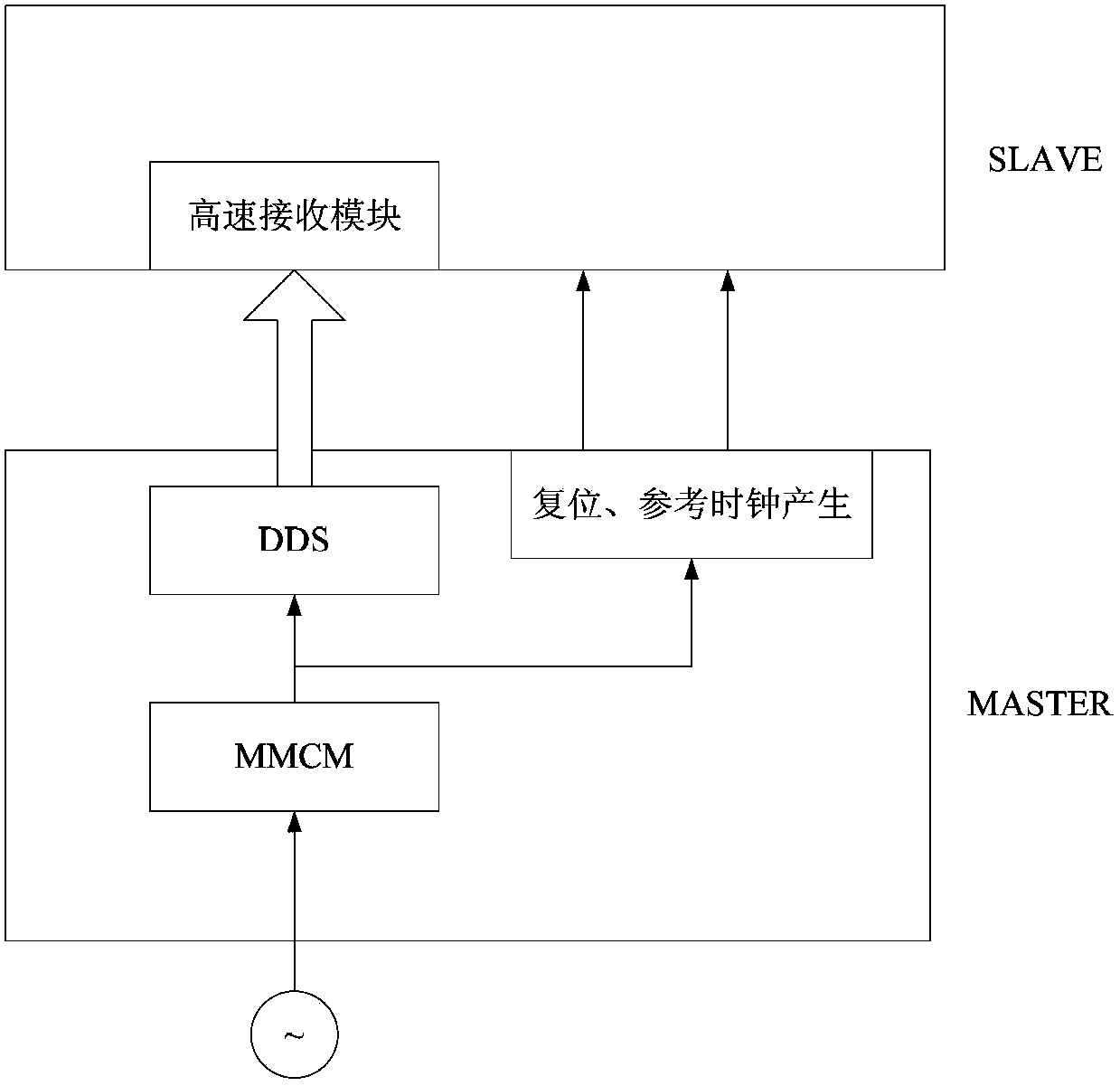

ActiveCN102882673AAchieving Phase SynchronizationExpand signal output bandwidthSynchronisation signal speed/phase controlClock phaseField-programmable gate array

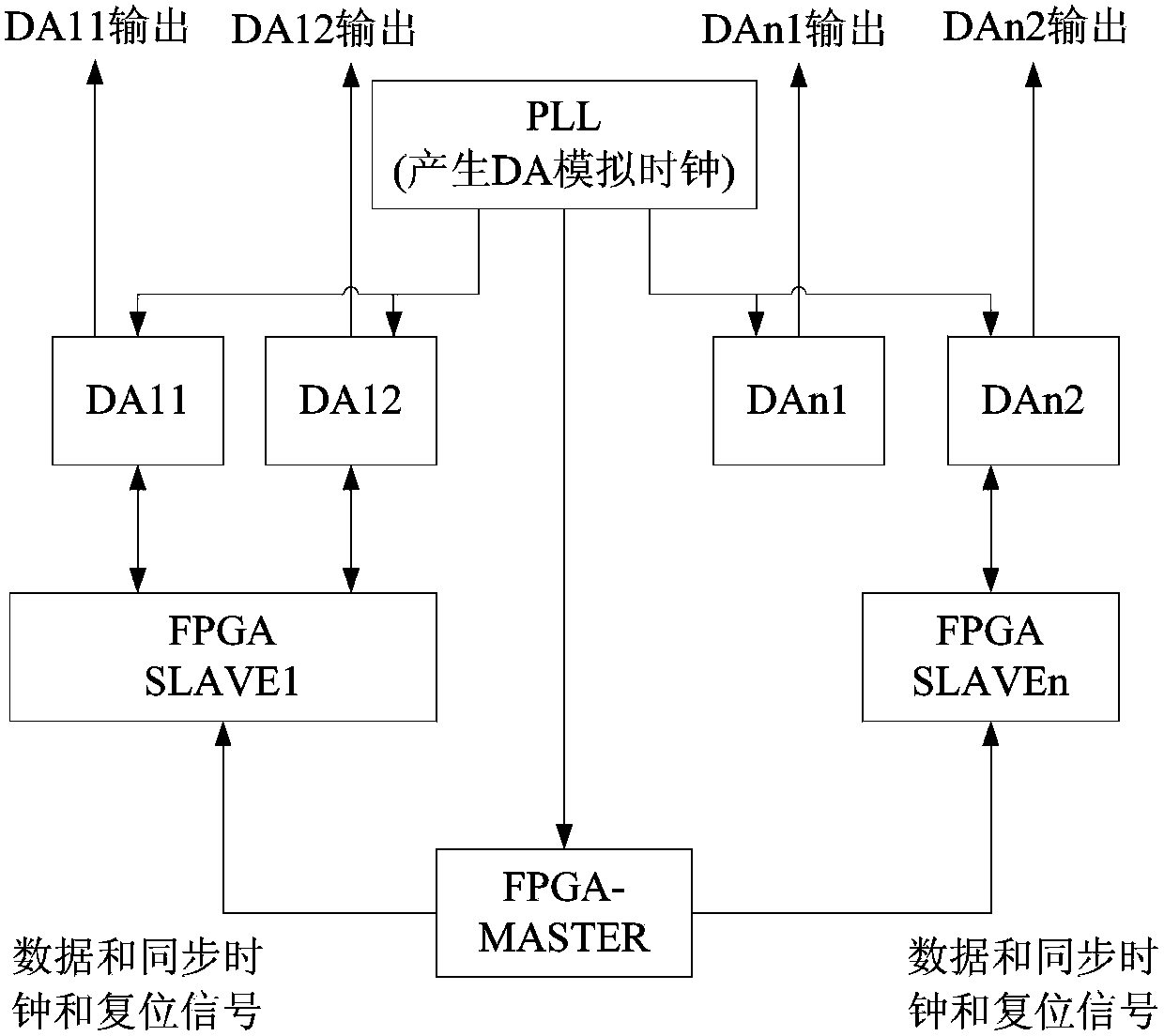

The invention discloses a multi-channel high-speed digital-to-analogue converter (DAC) synchronization method, which comprises the following steps of: first generating a digital signal source reference signal, a synchronous clock signal and a resetting signal by using a field programmable gate array-MASTER (FPGA-MASTER), simultaneously transmitting the signals to an FPGA-SLAVEP and a DACM, and roughly adjusting multi-path delay, wherein P and M are positive integers; then performing FPGA-MASTER synchronous clock phase discrimination in the FPGA-SLAVEP, and regulating a phase difference to 0 by using a fine delay module; and finally performing DACM reference clock phase discrimination in the FPGA-SLAVEP, and regulating a phase difference to 0 by using the fine delay module. Output signals can be subjected to phase synchronization, a plurality of FPGAs and a plurality of high-speed DACs can be simultaneously cascaded without the limitation of clock speed of the DACs, and FPGA-SLAVEPs are used for performing phase discrimination and phase regulation on the FPGA-MASTER and the DACs to make the phases of data of the FPGA-MASTER, the FPGA-SLAVEs and the DACs consistent, so that the time sequence of each path of DAC is completely synchronous and controllable, working efficiency is improved, and a signal output bandwidth is expanded.

Owner:TSINGHUA UNIV

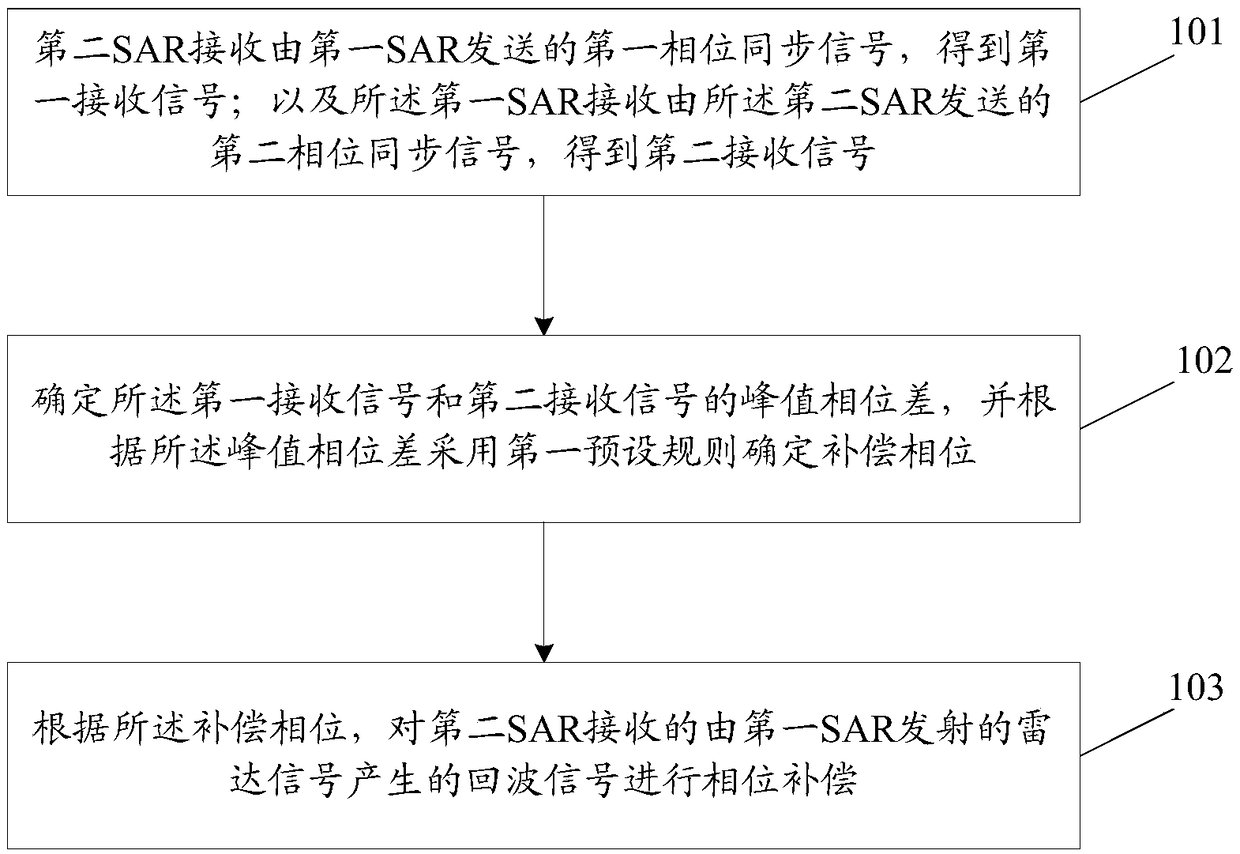

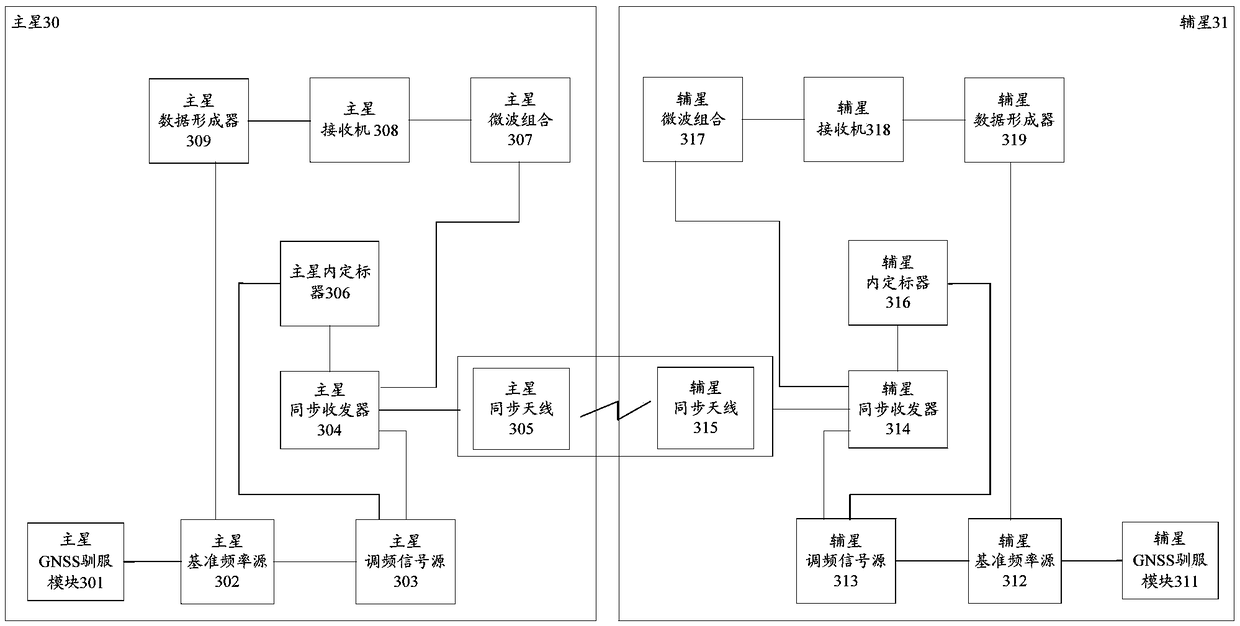

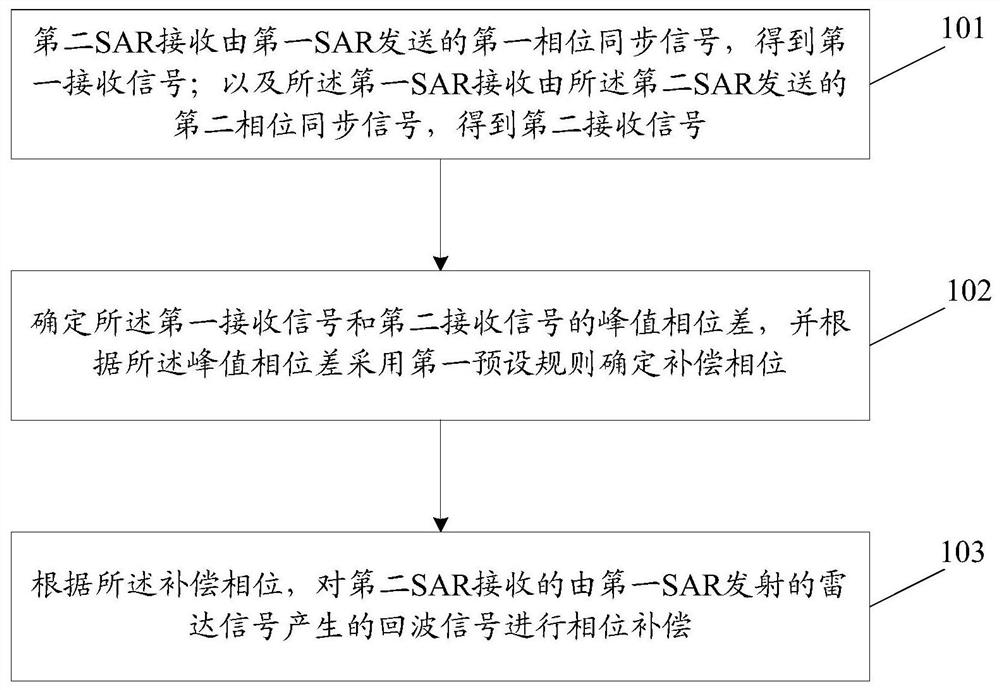

Phase synchronization method and device

ActiveCN108833071AAchieving Phase SynchronizationImprove image qualitySynchronisation arrangementTransmission monitoringInformation processingPhase difference

The invention discloses a phase synchronization method comprising that a second synthetic aperture radar (SAR) receives a first phase synchronization signal transmitted by a first SAR to obtain a first received signal; the first SAR receives a second phase synchronization signal sent by the second SAR to obtain a second received signal; a peak phase difference between the first received signal andthe second received signal is determined, and a compensation phase is determined according to the peak phase difference according to a first preset rule; phase compensation is performed on an echo signal generated by a radar signal transmitted by the first SAR and received by the second SAR according to the compensation phase. The invention also discloses a phase synchronization device, a storagemedium and an information processing device.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

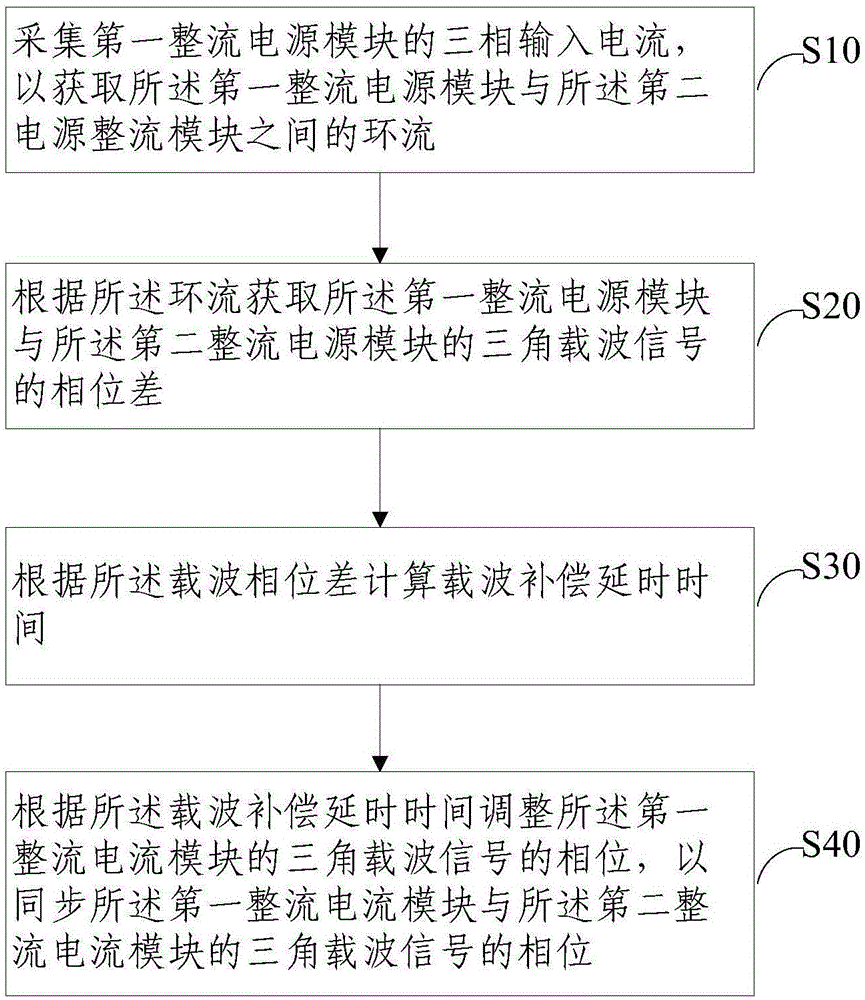

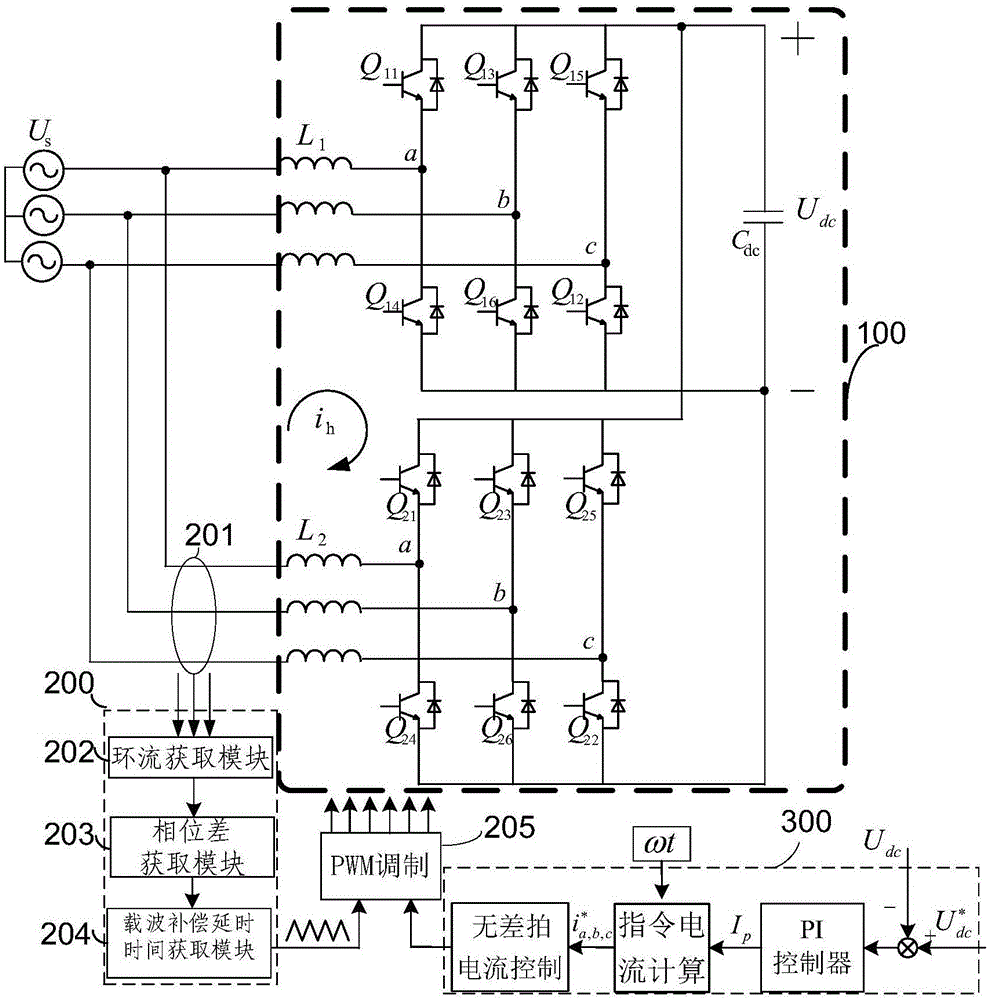

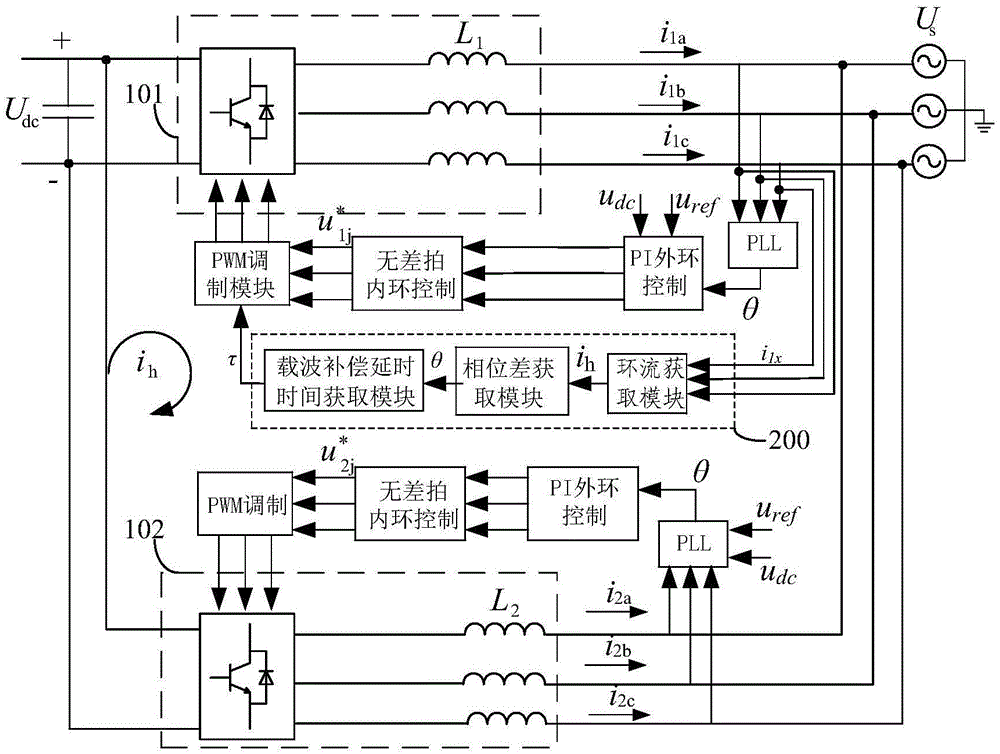

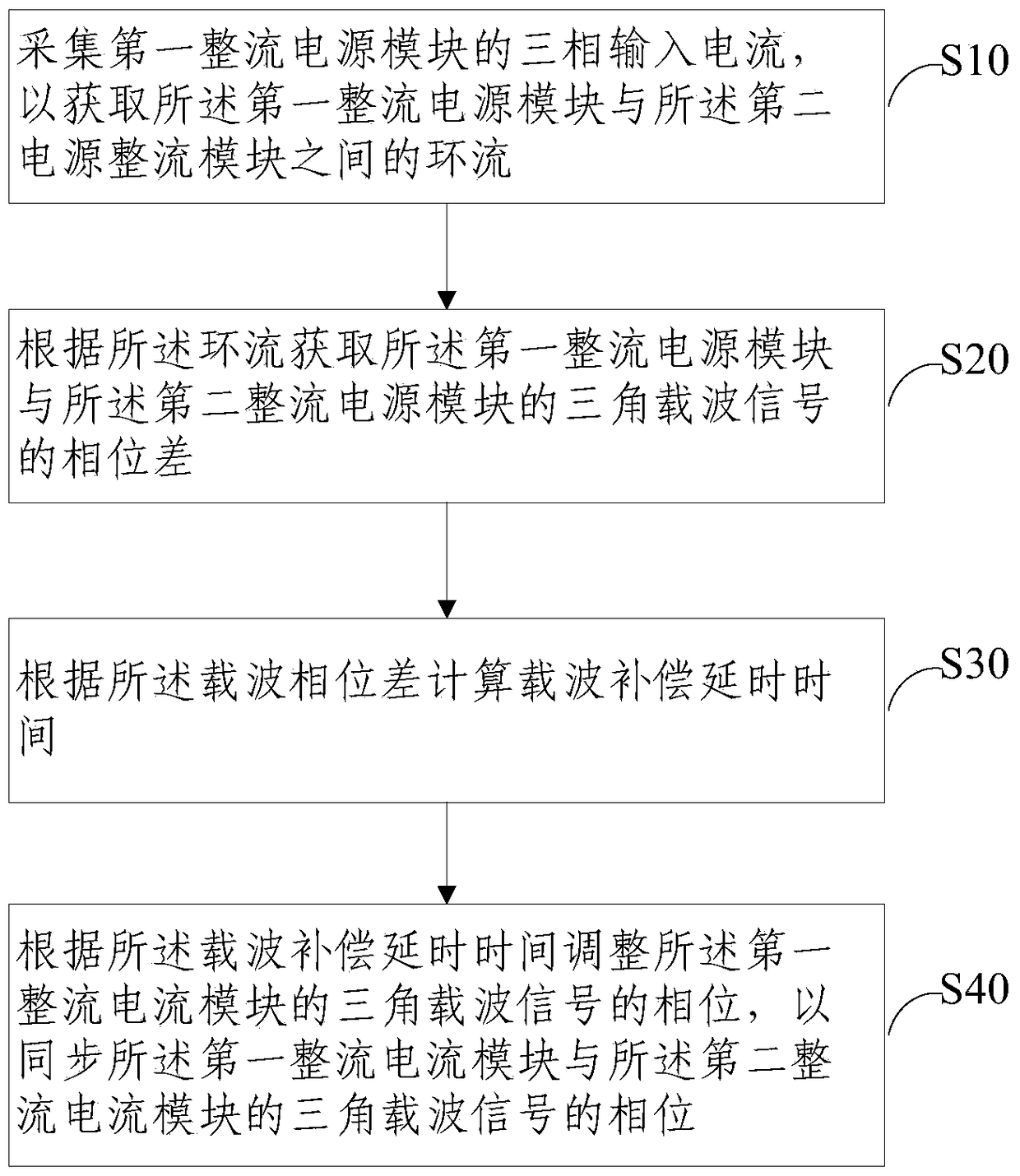

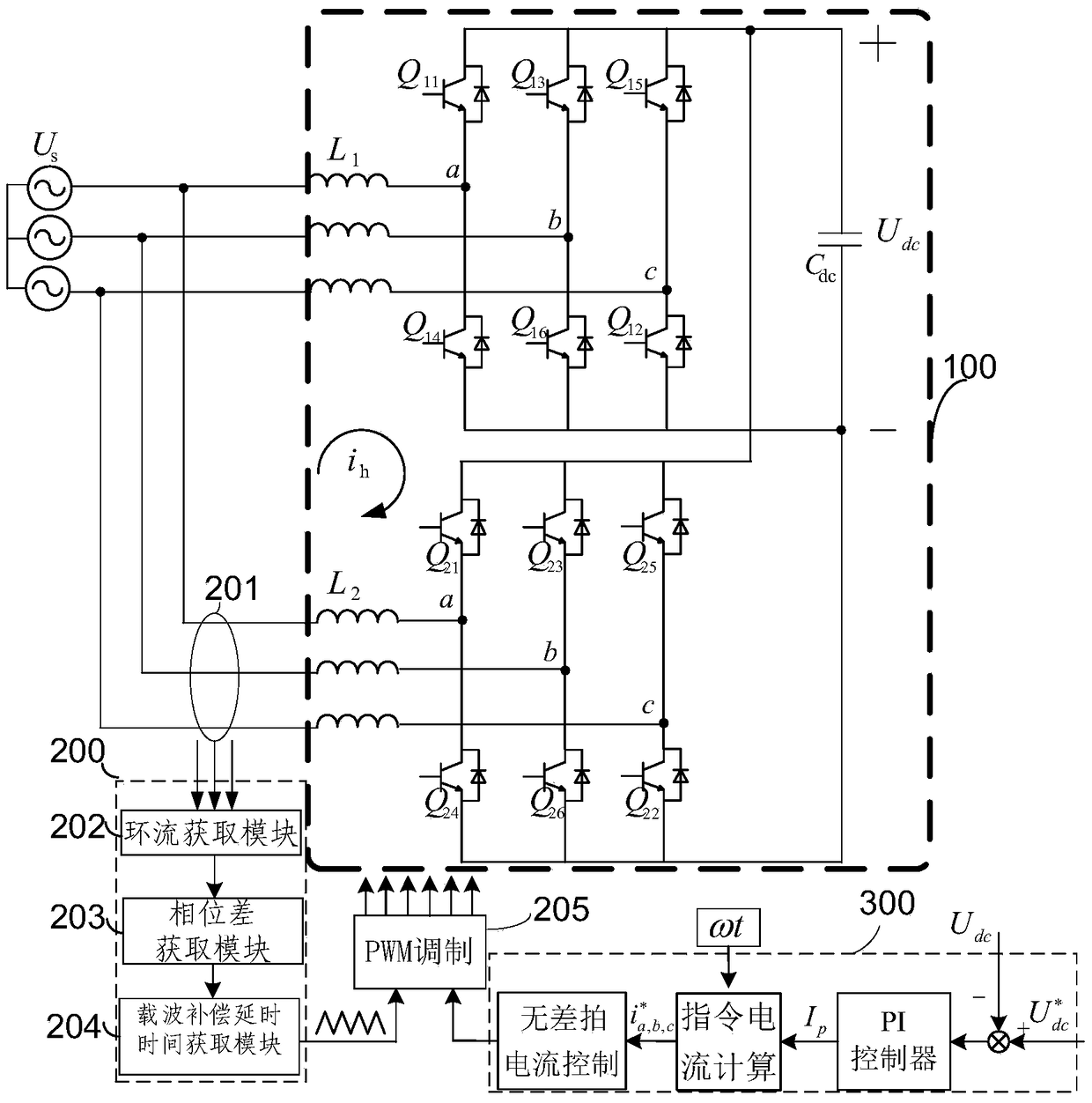

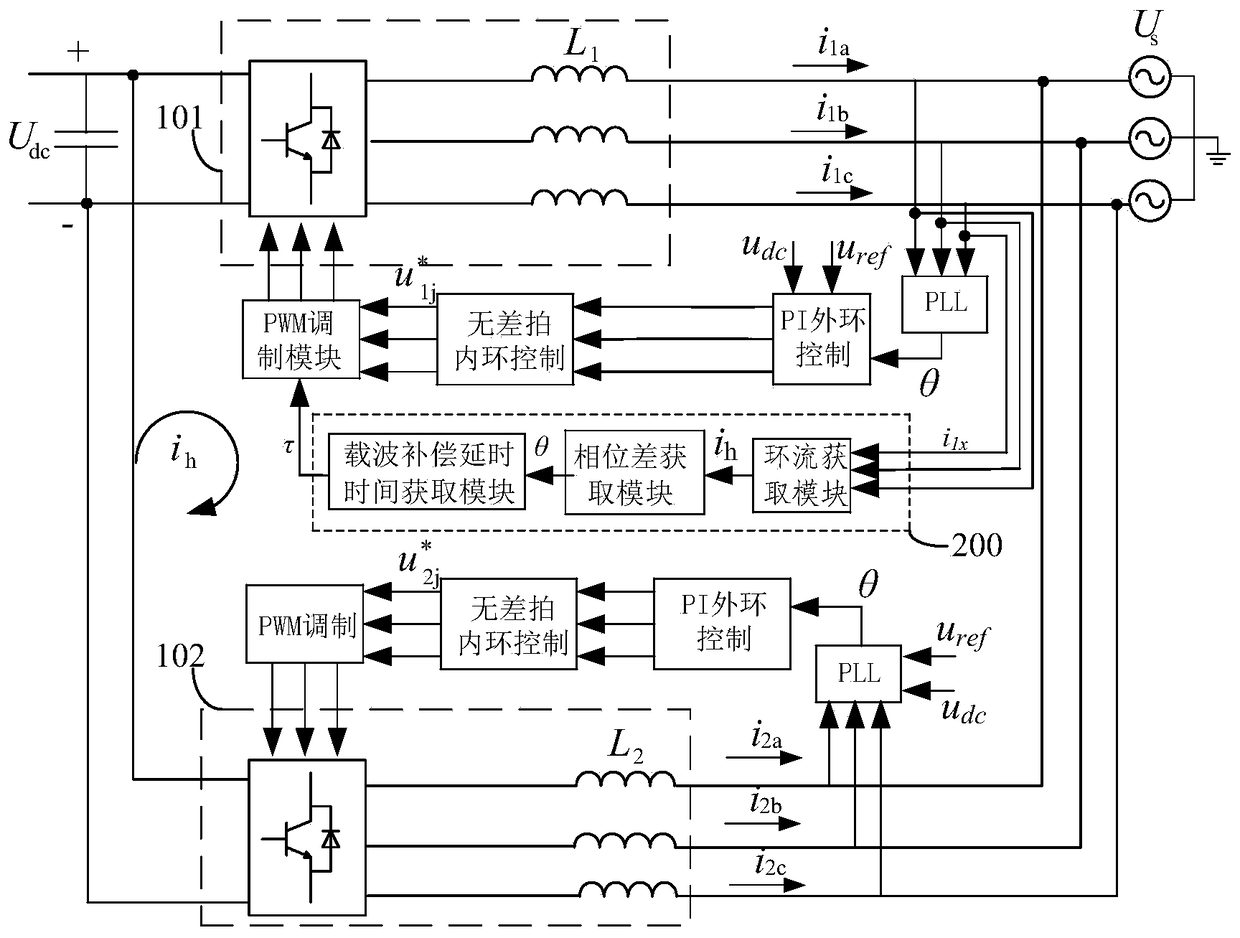

Method, device and system for inhibiting ring current between large power PWM (Pulse-Width Modulation) rectification power supply modules

ActiveCN105048829ASuppressed circulationBalance loadAc-dc conversion without reversalCarrier signalEngineering

The invention relates to a method, a device and a system for inhibiting ring current between large power PWM (Pulse-Width Modulation) rectification power supply modules. The method comprises steps of collecting three phase input current of a first rectification power supply module to obtain ring current between the first rectification power supply module and a second rectification power supply module; obtaining a phase difference of triangular carrier signals of the first rectification power supply module and the second rectification power supply module according to the ring current; calculating a carrier compensation delay time according to the carrier phase difference; and adjusting a phase of the triangular carrier signal of the first rectification power supply module according to the carrier compensation delay time so as to synchronize phases of the triangular carrier signals of the first rectification power supply module and the second rectification power supply module. The invention can effectively inhibit ring current between two rectification power supply modules, balances loads of the two rectification power supply modules, and improves safety and stability of a power distribution network.

Owner:HUNAN UNIV +1

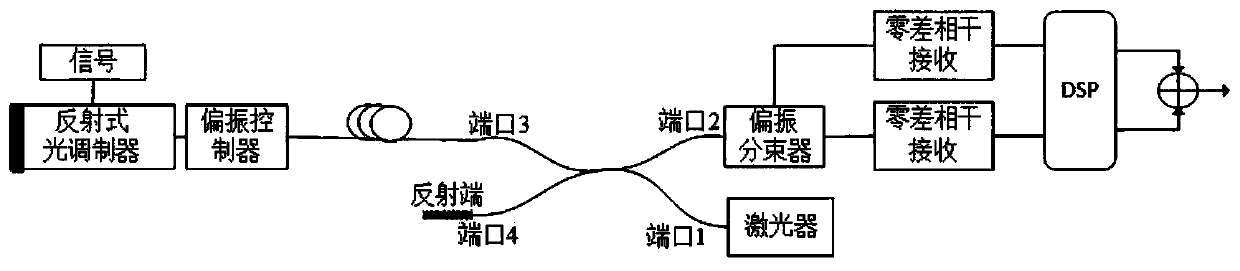

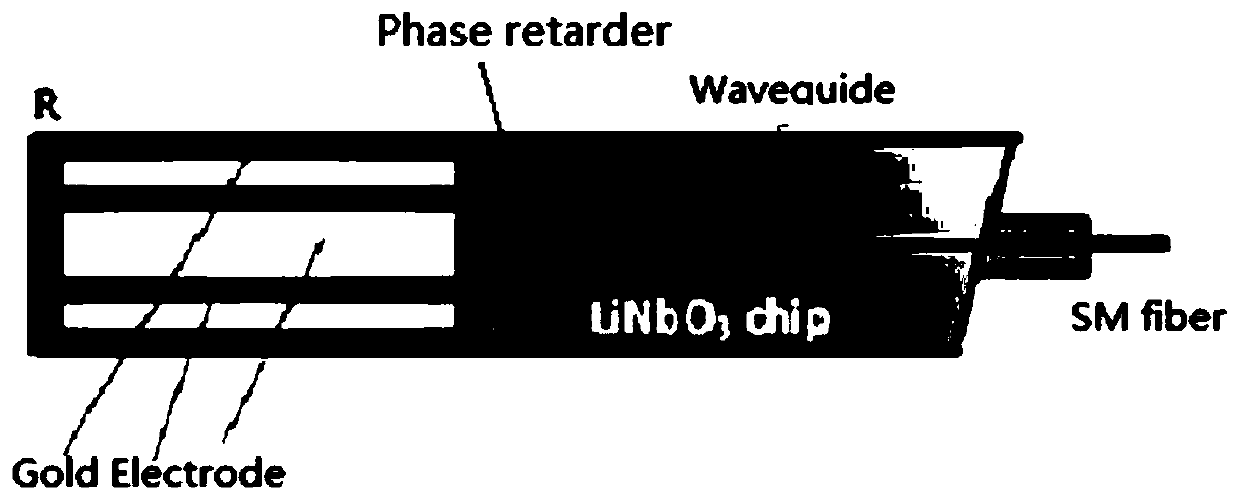

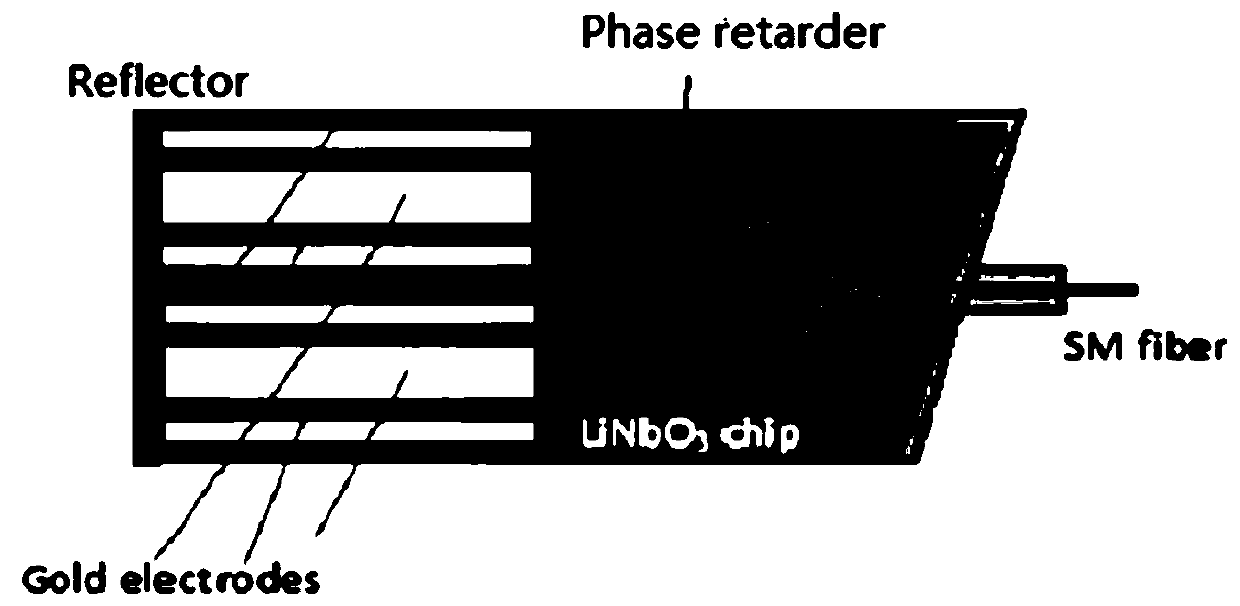

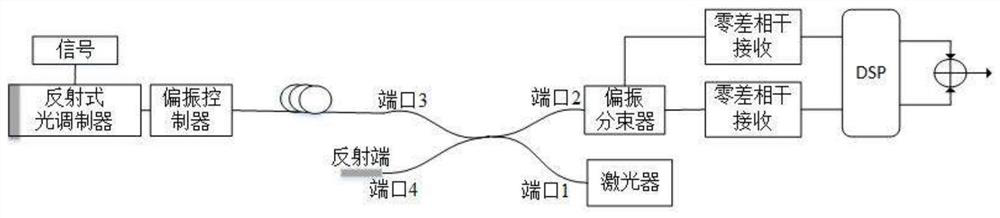

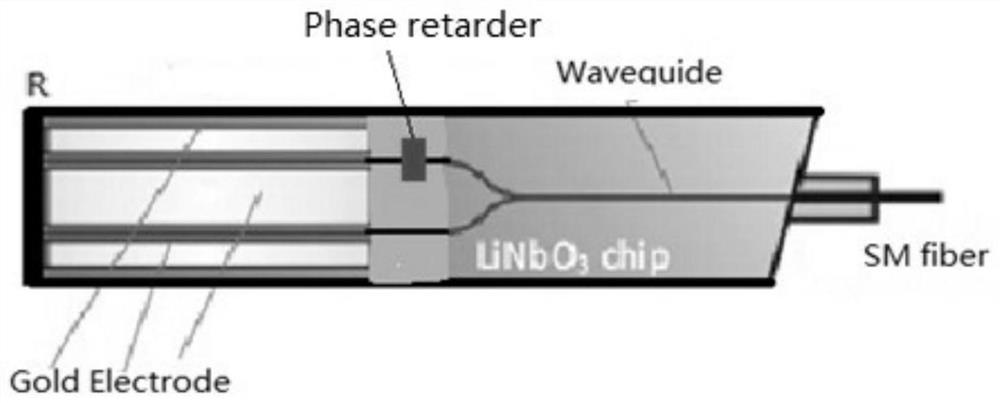

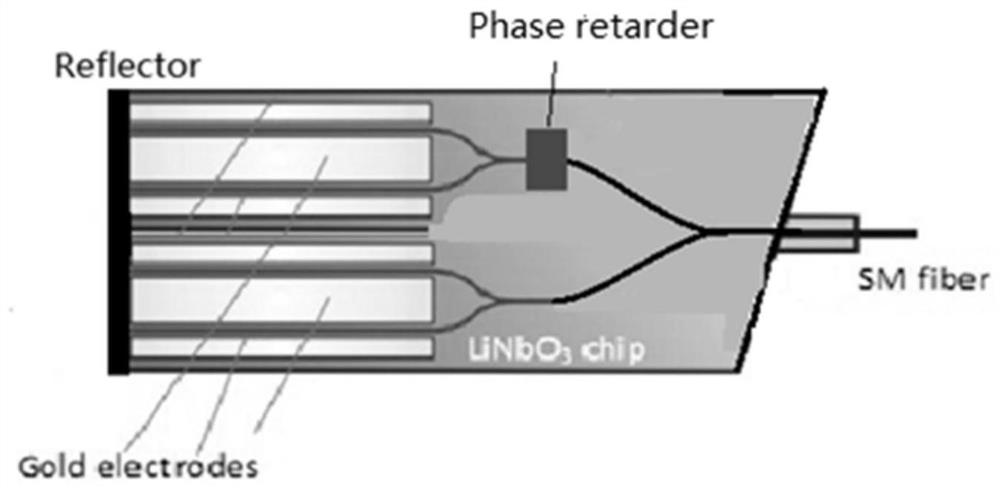

Four-phase reflection type coherent optical communication system

ActiveCN109981182AAchieving Phase SynchronizationImprove confidentialityElectromagnetic receiversDigital signal processingCommunications system

The invention discloses a four-phase reflection type coherent optical communication system, and belongs to the technical field of optical communication systems. The optical communication system comprises a laser, a reflective optical modulator, a polarization controller, a 3dB coupler, a polarization beam splitter, a homodyne coherent receiver, a digital signal processing module and an adder. According to the reflection type coherent optical communication system provided by the invention, the self-coherent demodulation technology is adopted, the signal light and the local oscillation light arefrom the same light source, the wavelength tracking of the local oscillation laser is realized without closed-loop feedback in a traditional coherent optical communication system, and the receiving part is relatively simple.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

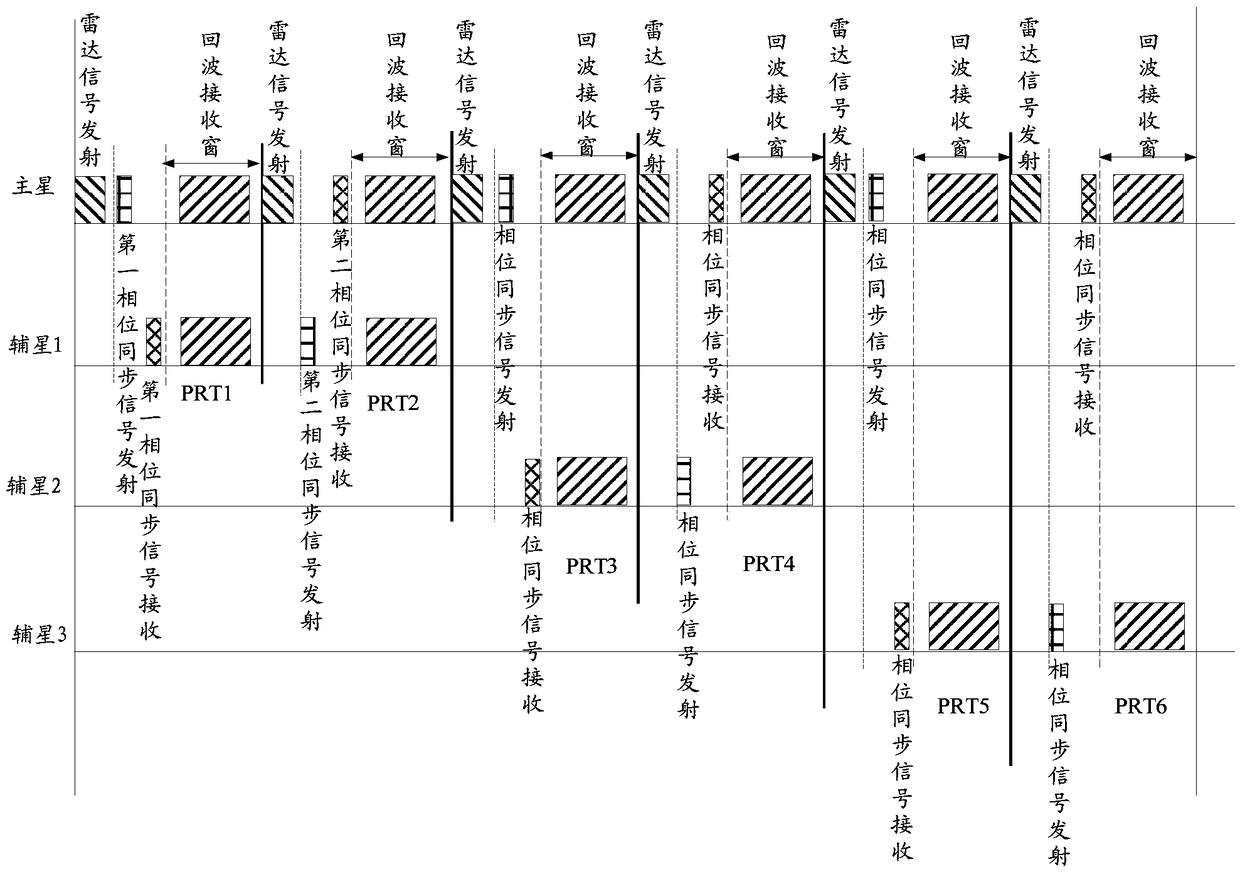

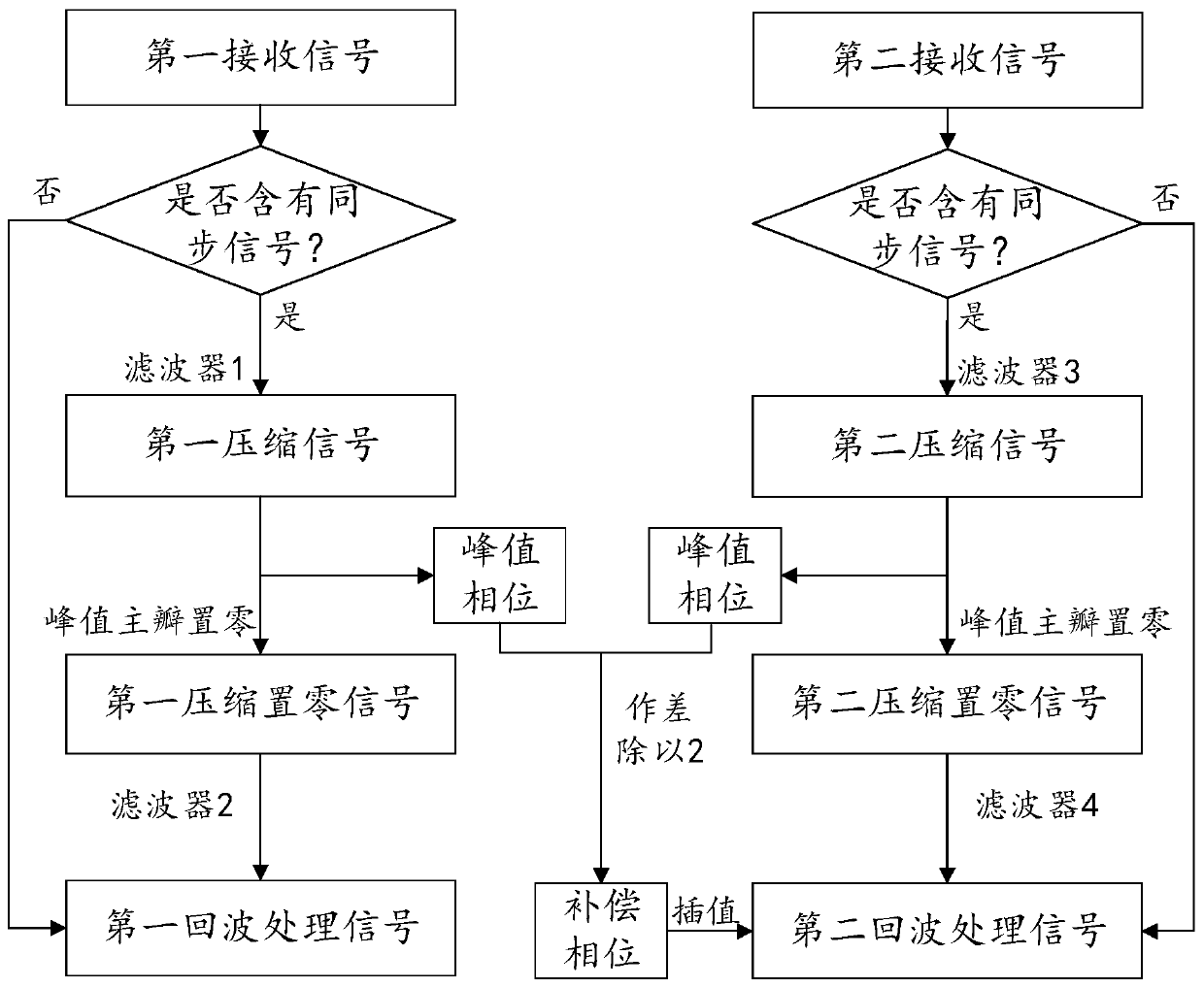

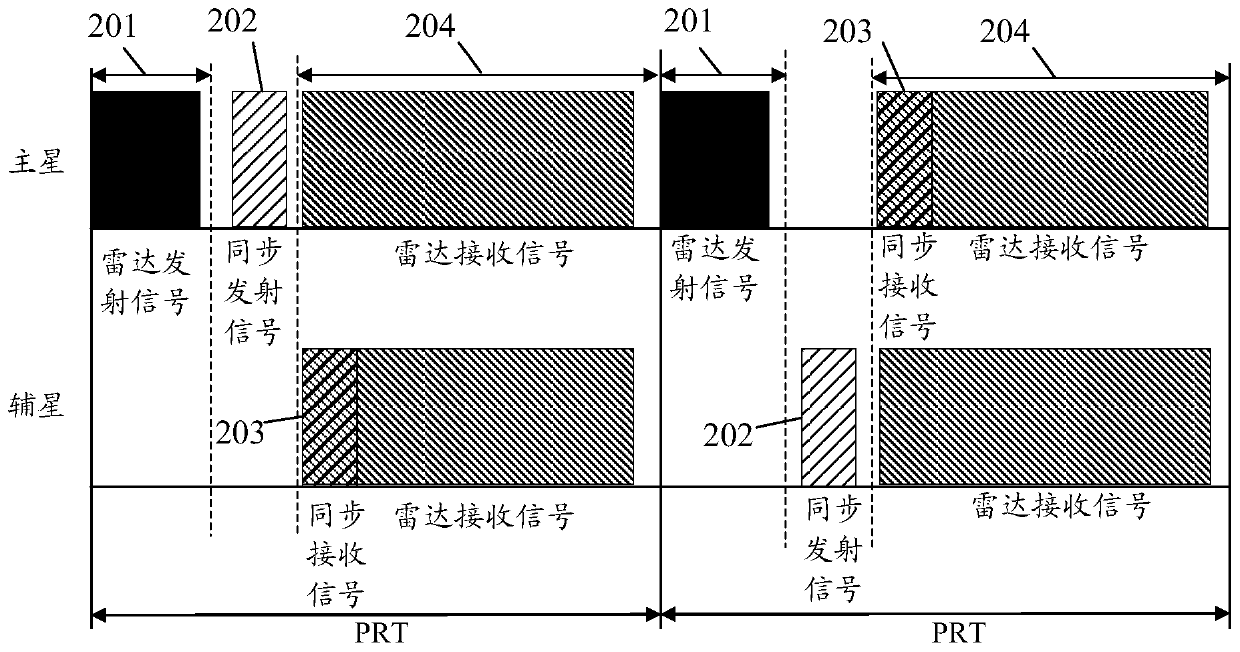

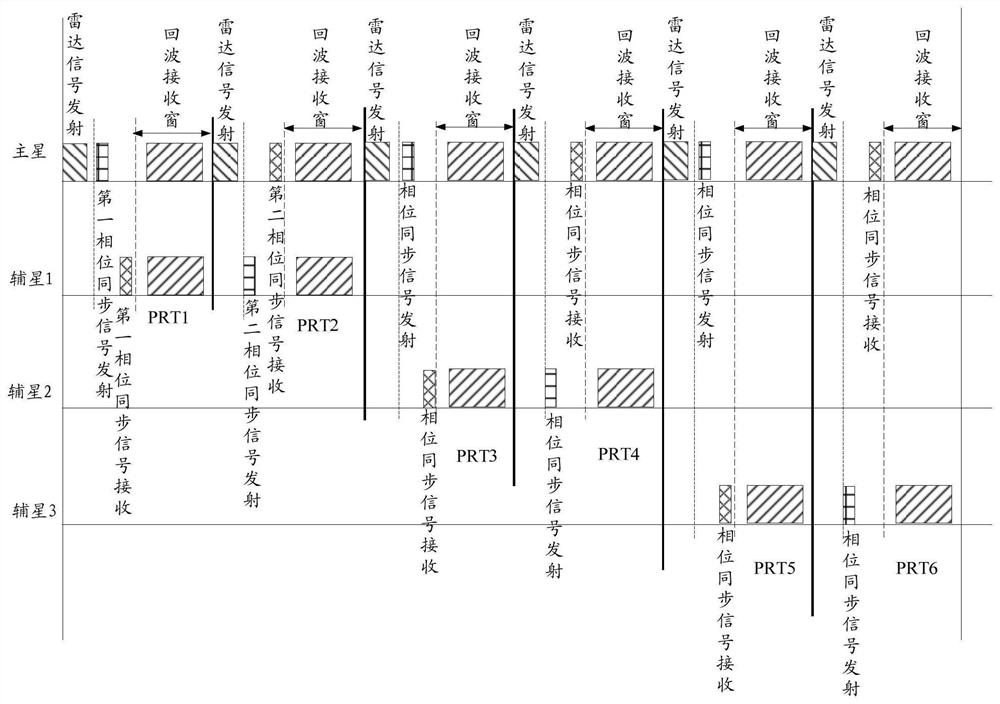

Non-interrupted bistatic SAR phase synchronization signal processing method based on coded signal

ActiveCN110488285AAchieving Phase SynchronizationImprove image qualityRadio wave reradiation/reflectionImaging processingComputer science

The embodiment of the invention discloses a non-interrupted bistatic SAR phase synchronization signal processing method based on a coded signal. The method comprises the steps of: when a first receiving signal of a first SAR only contains a first synchronization receiving signal, directly taking the first receiving signal as a first echo processing signal; when the first synchronization receivingsignal is contained in the first receiving signal, extracting the peak phase of the synchronous signal, and separating the synchronous signal to obtain a first echo processing signal; when a second synchronous receiving signal is not contained in the second receiving signal of a second SAR, directly taking the second receiving signal as a second echo processing signal; and when a second echo receiving signal is contained in the second receiving signal, extracting the peak phase of the synchronous signal, and separating the synchronous signal to obtain a second echo processing signal. The consumption phase is calculated according to the peak phase, and is compensated in the second echo processing signal after interpolation, and the obtained first and second echo processing signals are subjected to normal imaging processing.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

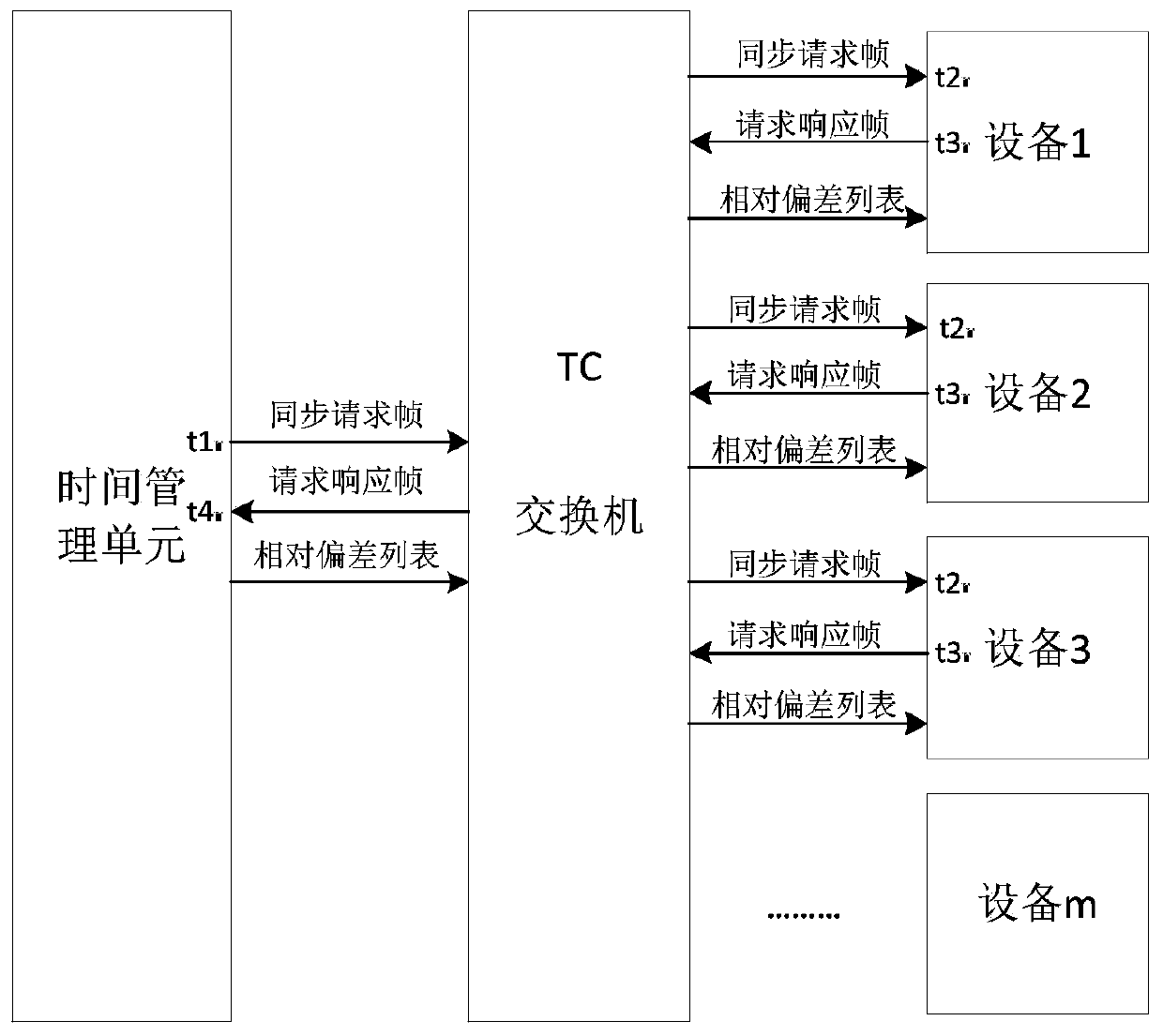

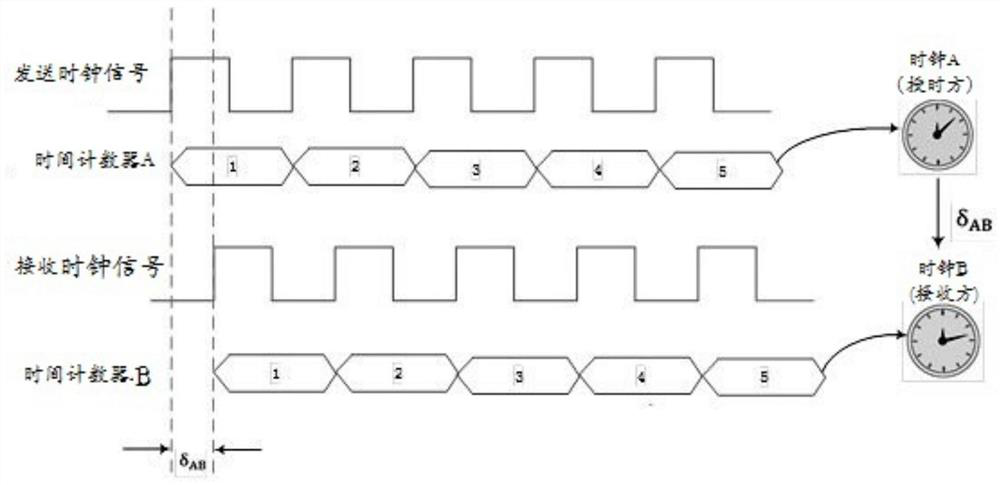

Clock synchronization method for equipment in local area network

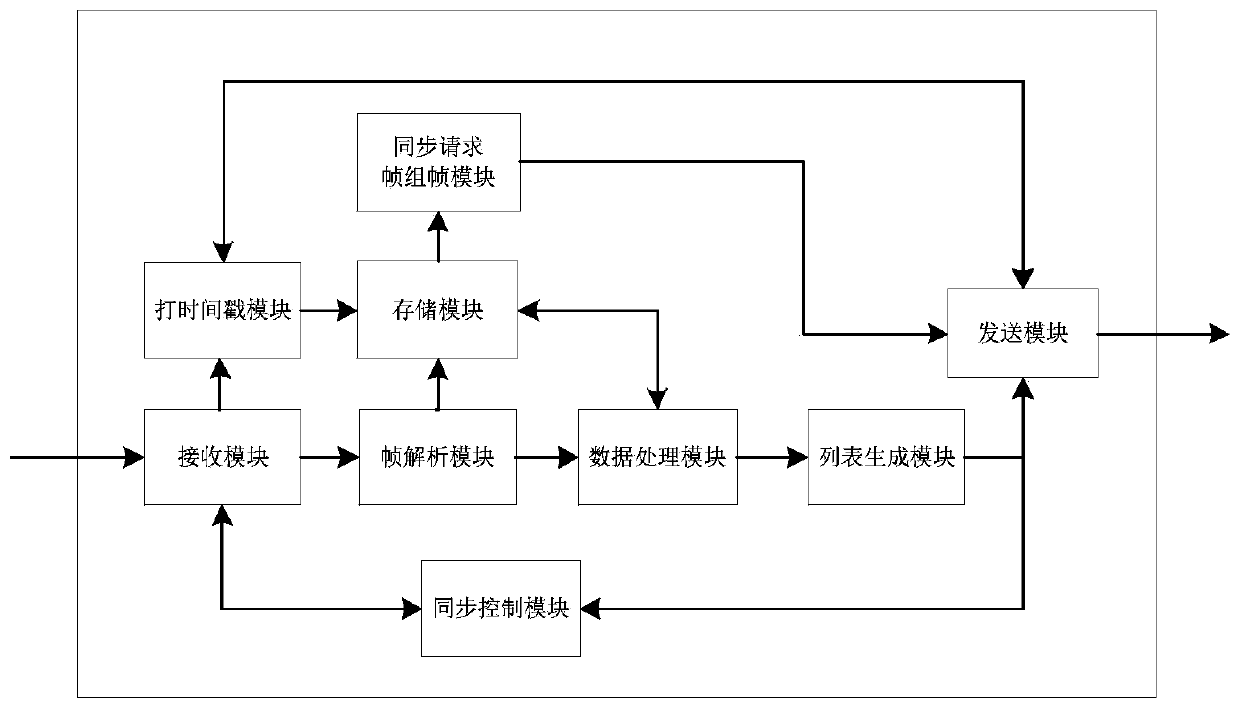

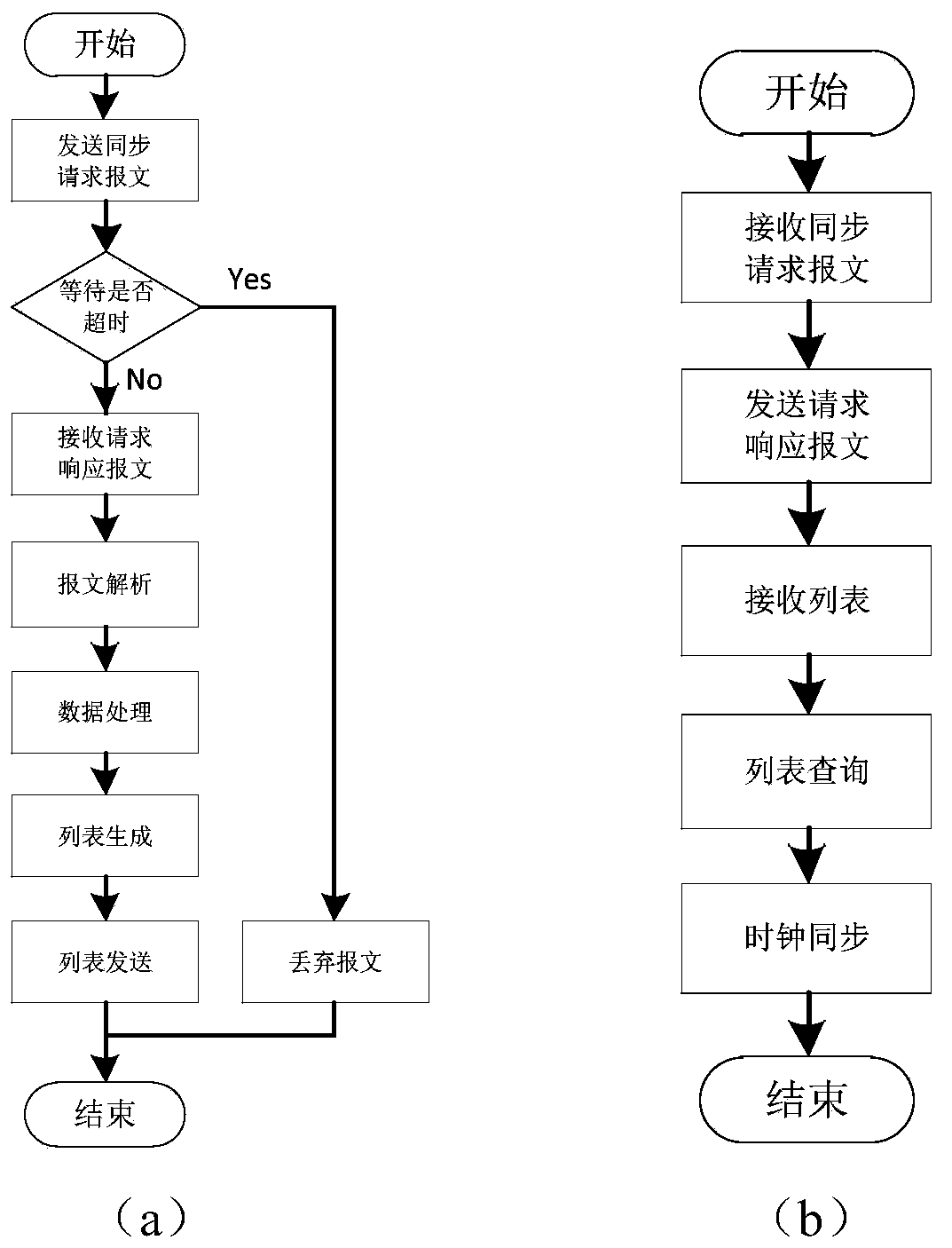

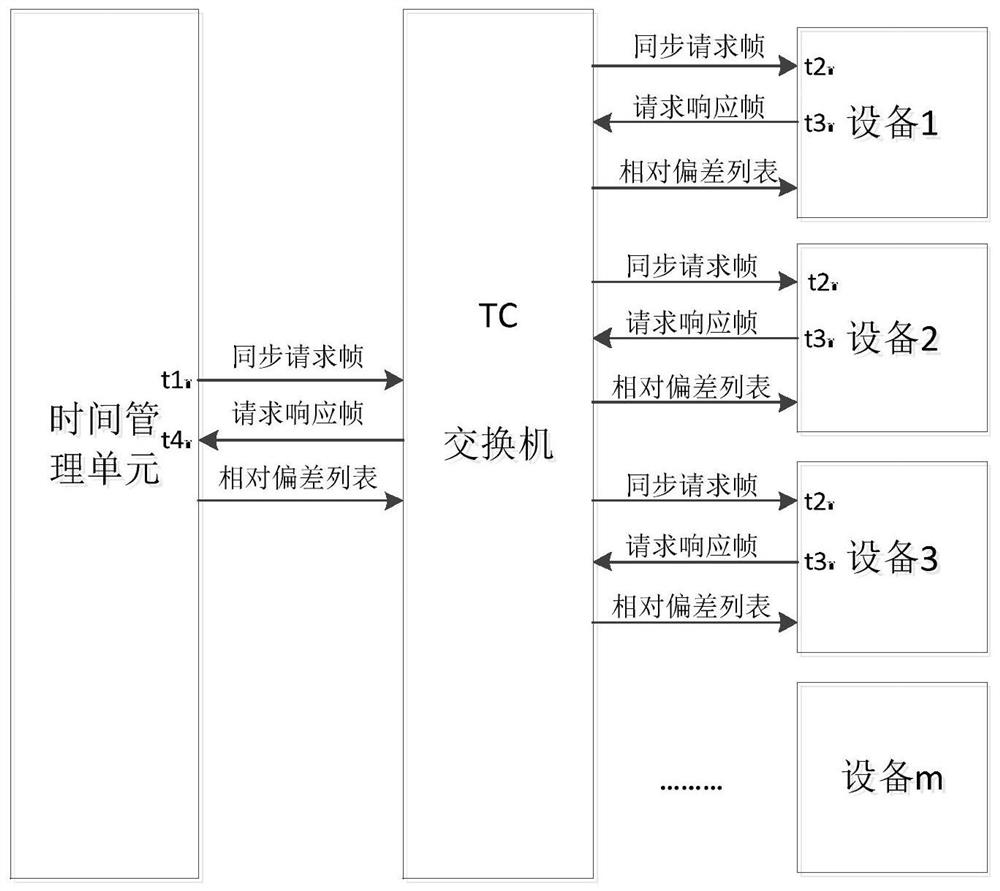

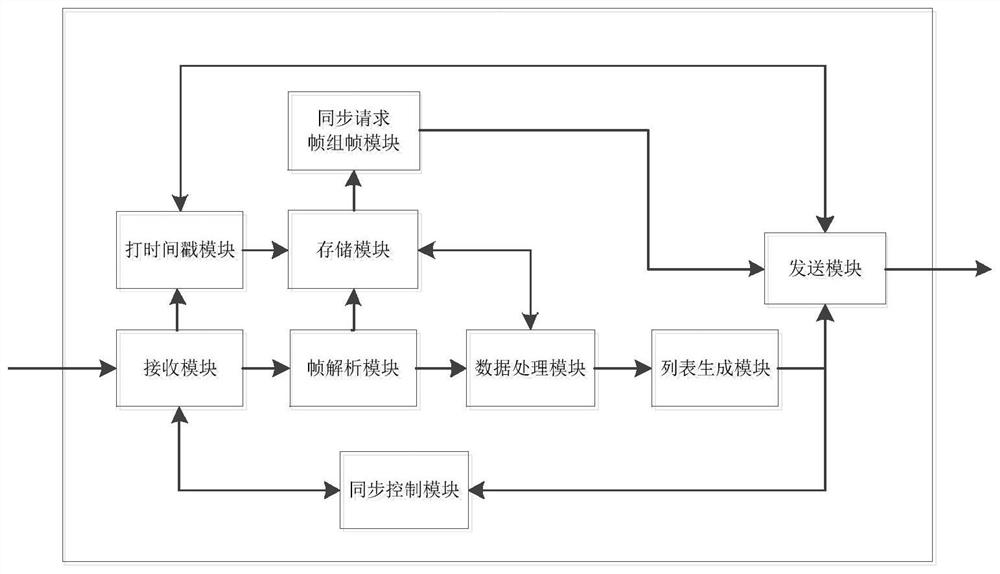

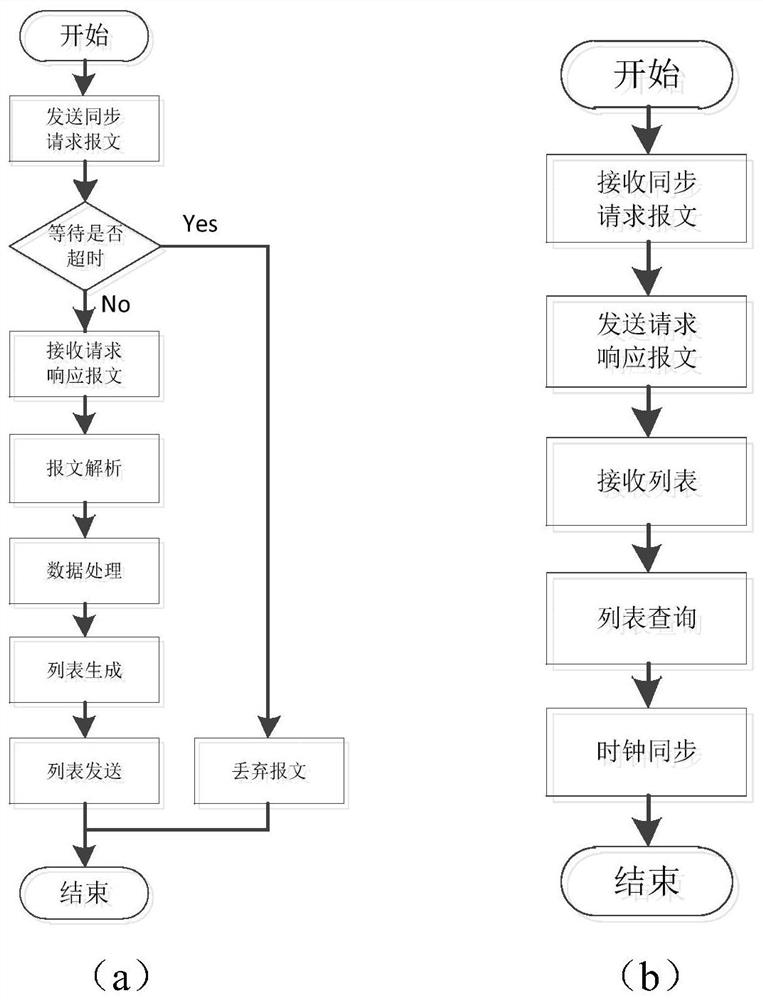

ActiveCN110808807AAchieving Phase SynchronizationImplement fixesTime-division multiplexTime deviationProtocol design

The invention discloses a clock synchronization method for equipment in a local area network. The method comprises the following steps: based on an IEEE 1588 protocol design idea, concentrating clockinformation of each device in a time management unit through a reciprocating message; calculating according to the time of each device and the time management unit information to obtain a phase deviation and a frequency correction coefficient of the device; associating the phase deviation with the frequency correction coefficient and the equipment number to generate a relative time deviation list,and sending the relative time deviation list to each piece of equipment needing to be synchronized; and enabling the equipment to inquire the relative deviation time list according to the equipment number and the target equipment number to obtain the frequency correction coefficient of the equipment and the relative time deviation of the equipment and the target equipment, so that clock phase synchronization and frequency correction can be realized. According to the clock frequency synchronization method based on the list, the problems that in the IEEE 1588 protocol synchronization process, the load is large, and the clock synchronization execution period is possibly long are solved, and in the time synchronization process, the clock frequency synchronization method based on the list is provided.

Owner:CIVIL AVIATION UNIV OF CHINA

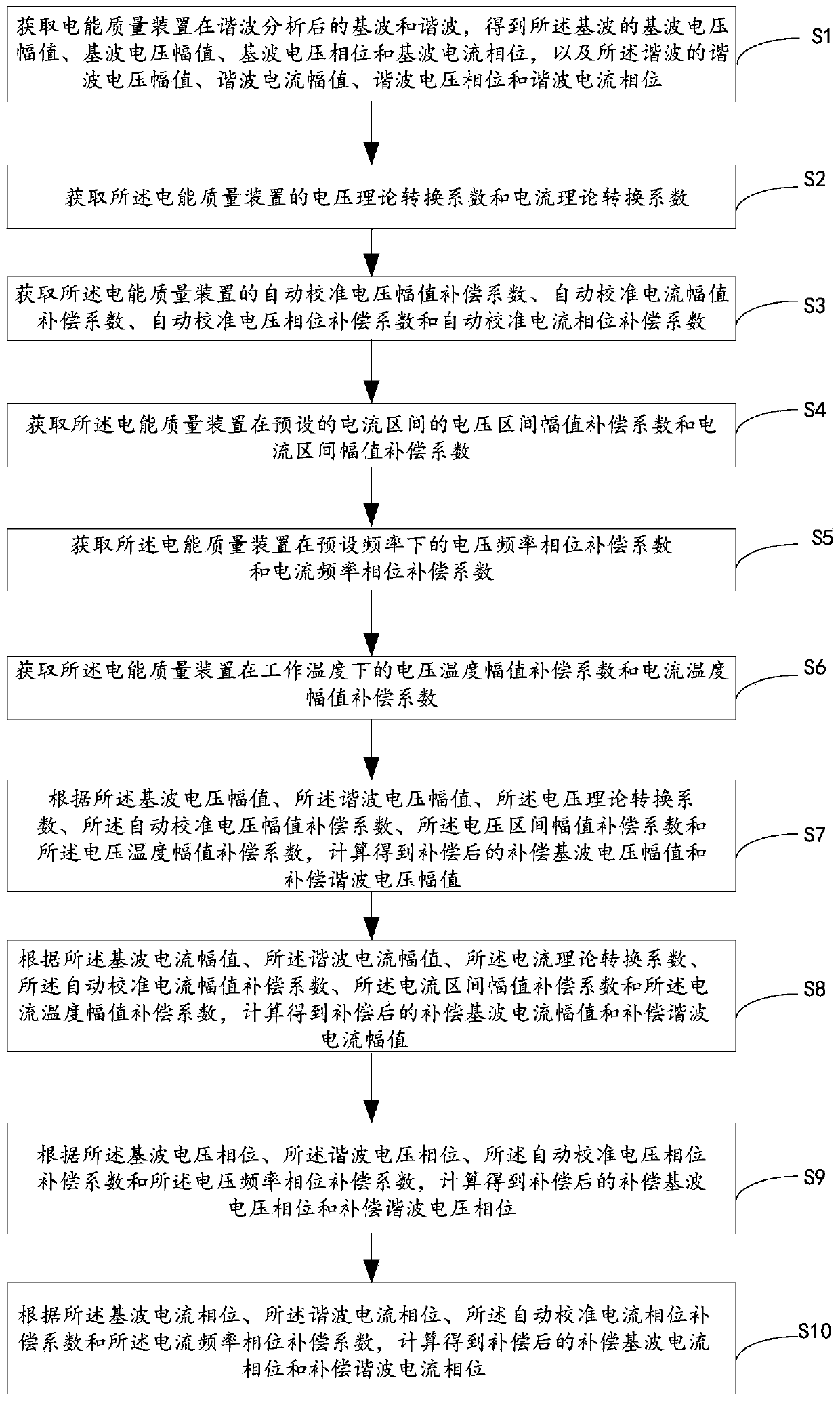

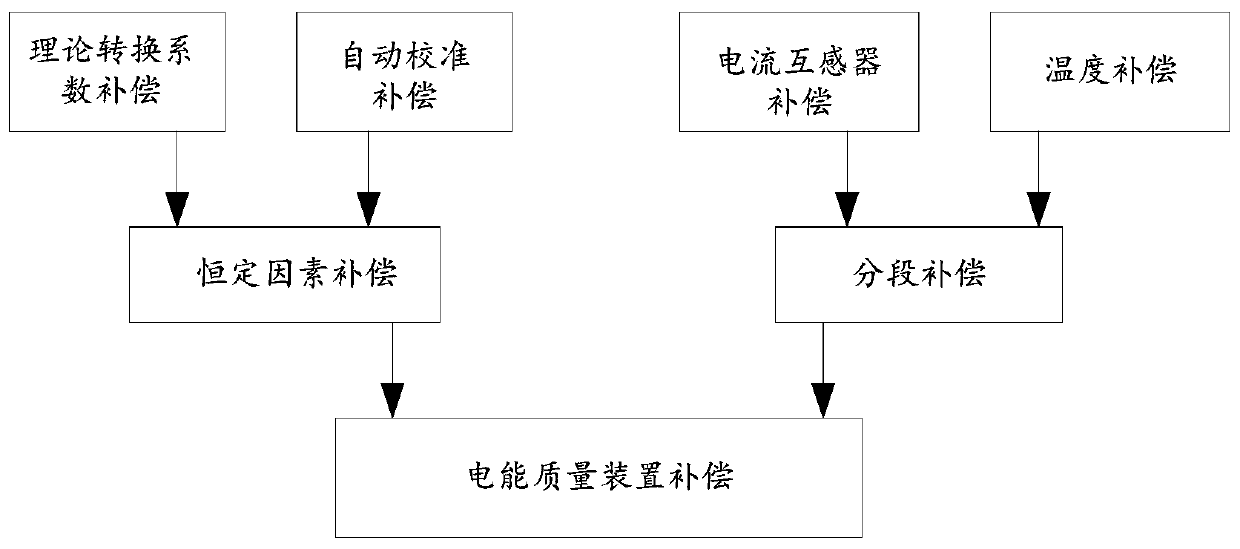

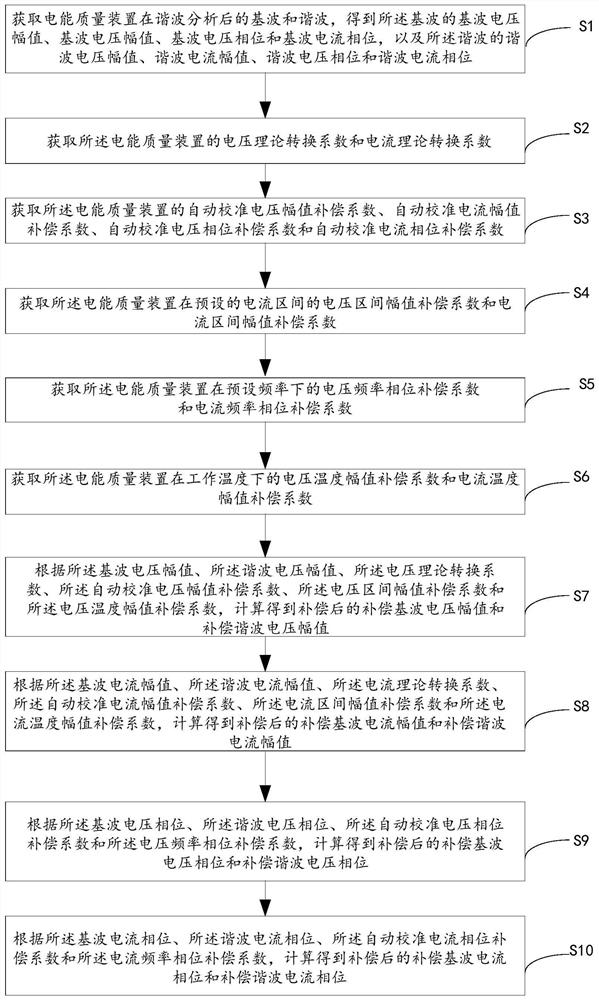

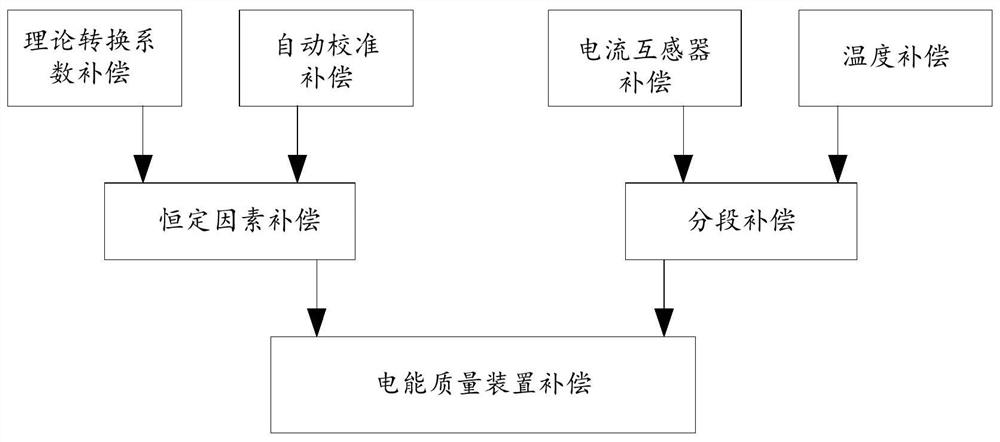

Method for measuring compensation of power quality device

ActiveCN110488092AAchieving Phase SynchronizationHigh measurement accuracySpectral/fourier analysisVoltage-current phase angleVoltage amplitudePower quality

The invention discloses a method for measuring compensation of a power quality device. The method includes the steps: acquiring a fundamental wave and a harmonic wave of a power quality device after harmonic analysis; acquiring a voltage theoretical conversion coefficient and a current theoretical conversion coefficient; acquiring an automatic calibration voltage amplitude compensation coefficient, an automatic calibration current amplitude compensation coefficient, an automatic calibration voltage phase compensation coefficient and an automatic calibration current phase compensation coefficient; acquiring a voltage interval amplitude compensation coefficient and a current interval amplitude compensation coefficient; acquiring a voltage frequency phase compensation coefficient and a current frequency phase compensation coefficient; acquiring a voltage temperature amplitude compensation coefficient and a current temperature amplitude compensation coefficient; and calculating the amplitude and phase of the compensated fundamental wave voltage, the amplitude and phase of the compensated fundamental wave current, the amplitude and phase of the compensated harmonic voltage, and the amplitude and phase of the compensated harmonic current. Therefore, the phase synchronization of the power quality device is realized and the measurement accuracy of the power quality device is improved effectively.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD +1

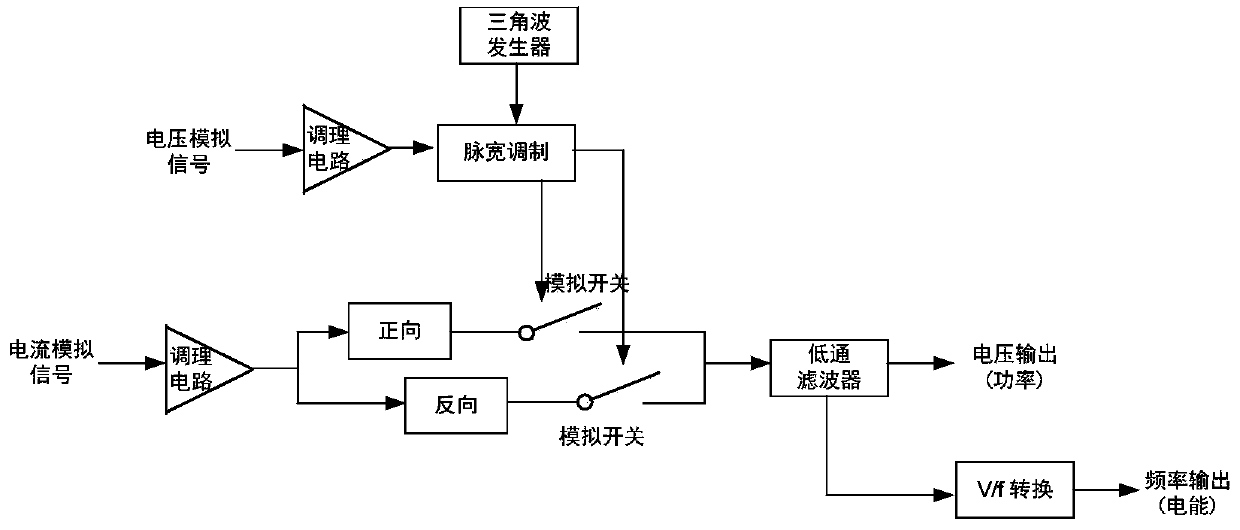

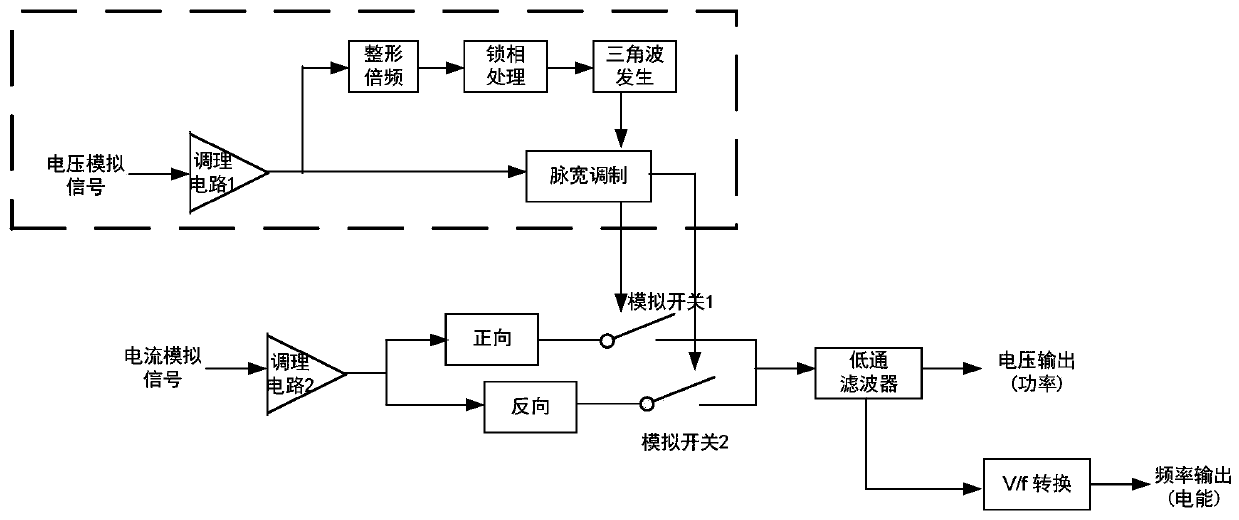

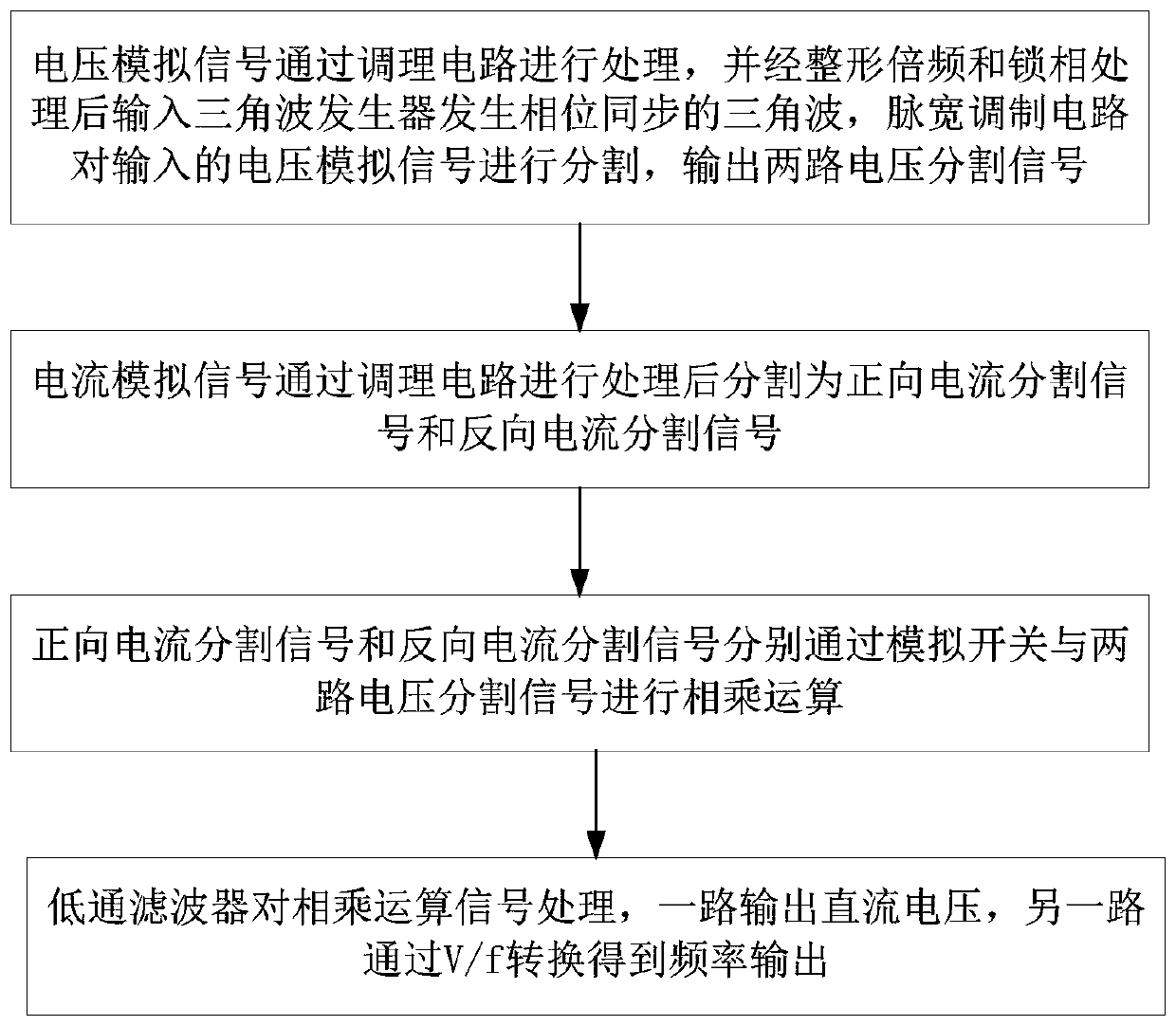

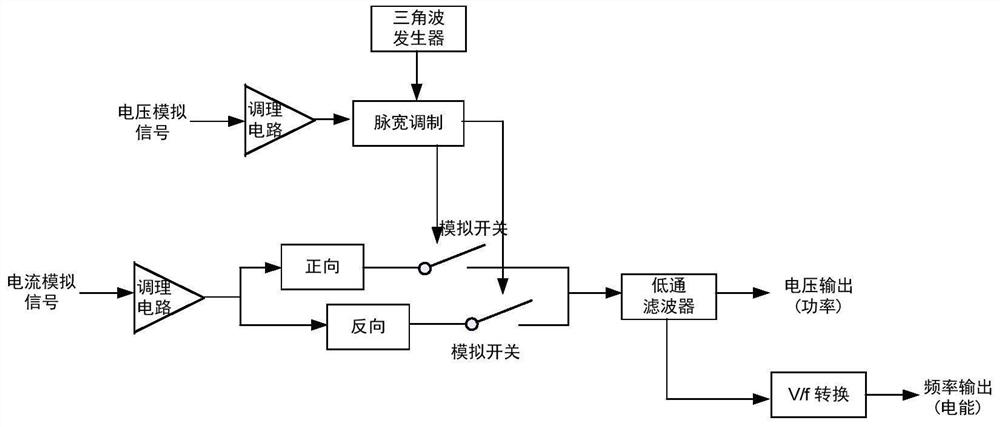

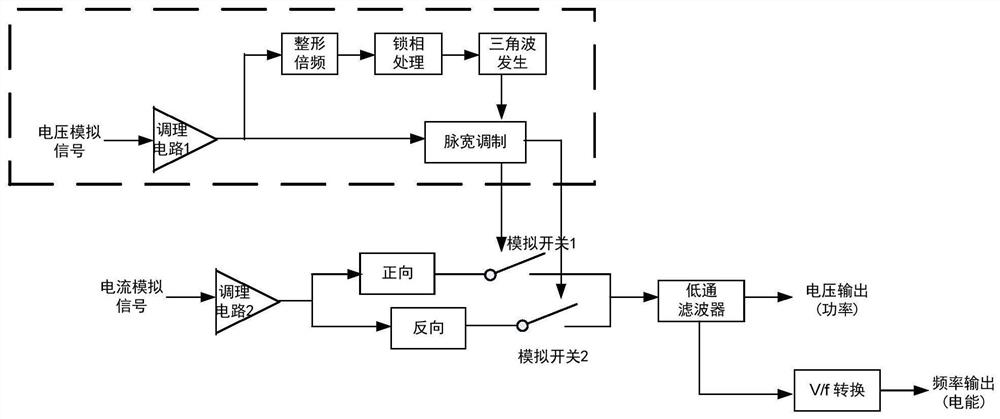

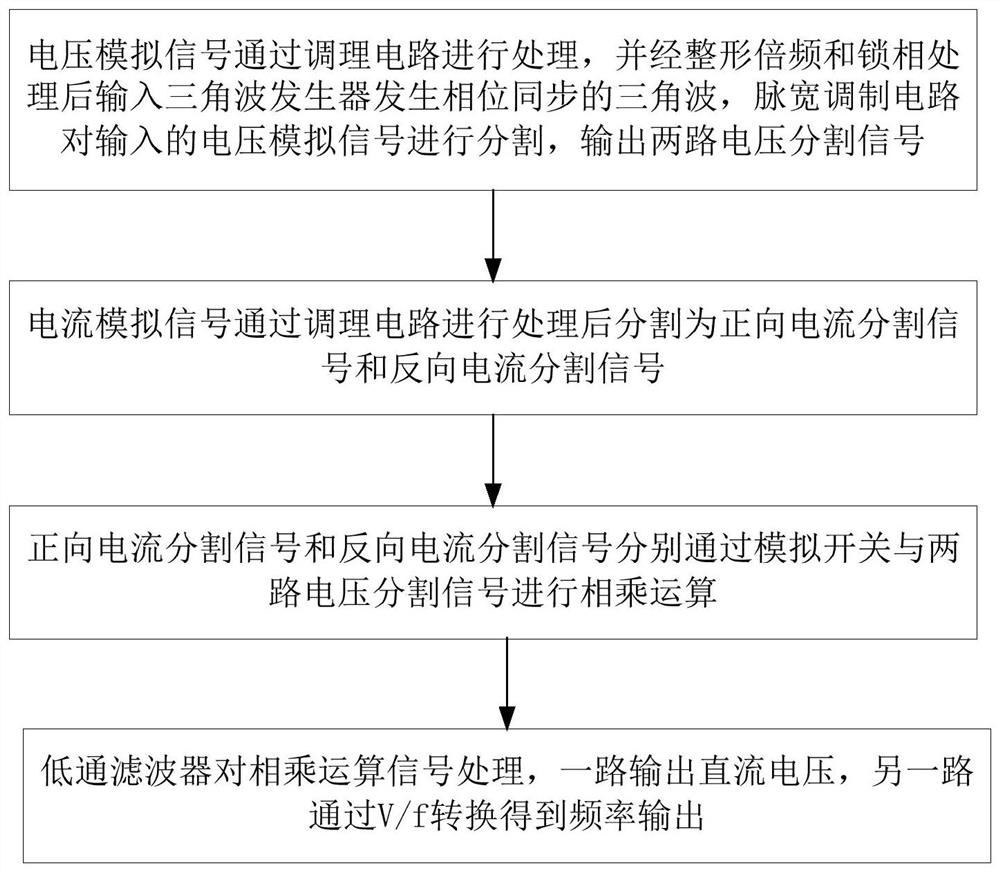

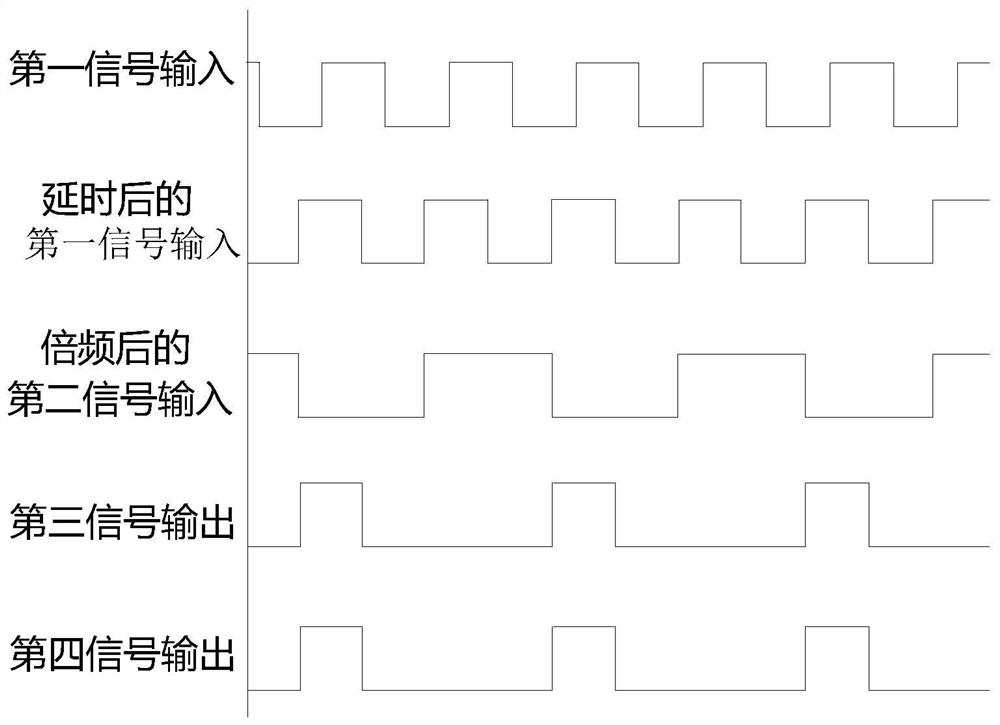

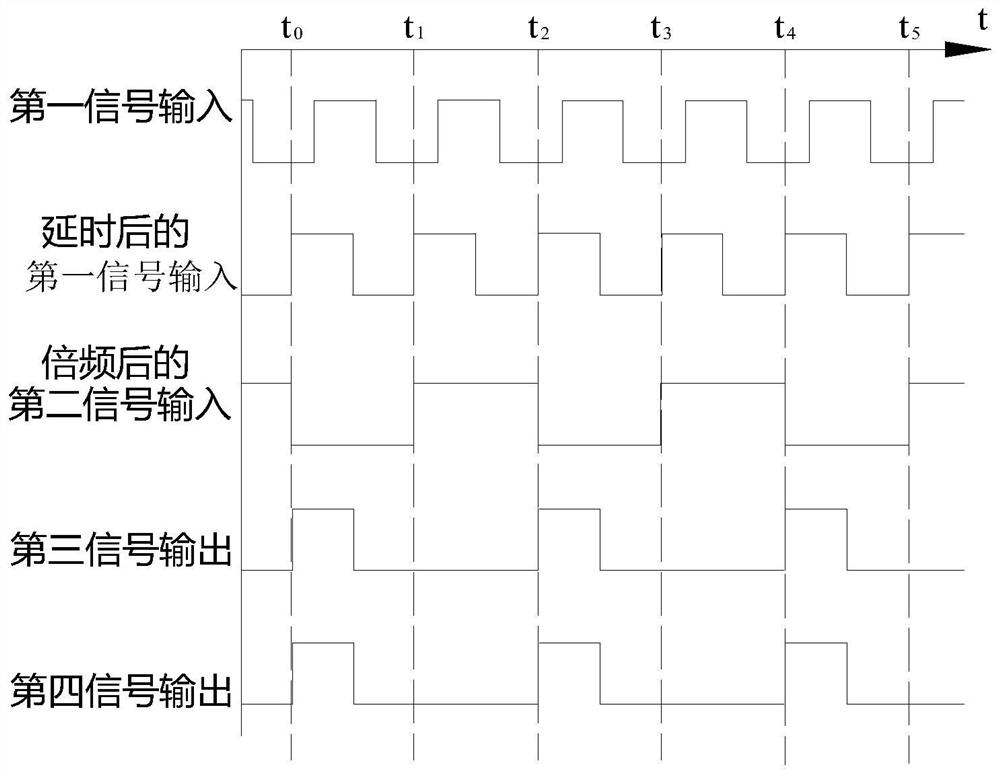

Time division power multiplier and implementation method thereof

ActiveCN111398884ASmall phase differenceImprove accuracyElectrical measurementsConvertersHemt circuits

The invention discloses a time division power multiplier and an implementation method thereof. The time division power multiplier comprises a voltage processing circuit, a current processing circuit,an analog switch, a filter and a V / f converter. The voltage processing circuit comprises a conditioning circuit 1, a phase synchronization circuit, a triangular wave generator and a pulse width modulation circuit. According to the invention, using signal conversion and phase locking technologies, a measured signal and a triangular wave generator of a time division multiplier are subjected to related processing, the triangular wave generator of the time division power multiplier is synchronized with the whole period of a measured signal, and the phase difference in conversion of the product oftwo measured alternating current quantities is reduced, so that the accuracy of a power / electric energy measurement result is improved, and the accuracy of the measurement technology of the time division power multiplier is improved to meet most active power / electric energy measurement requirements.

Owner:国网山东省电力公司营销服务中心(计量中心) +4

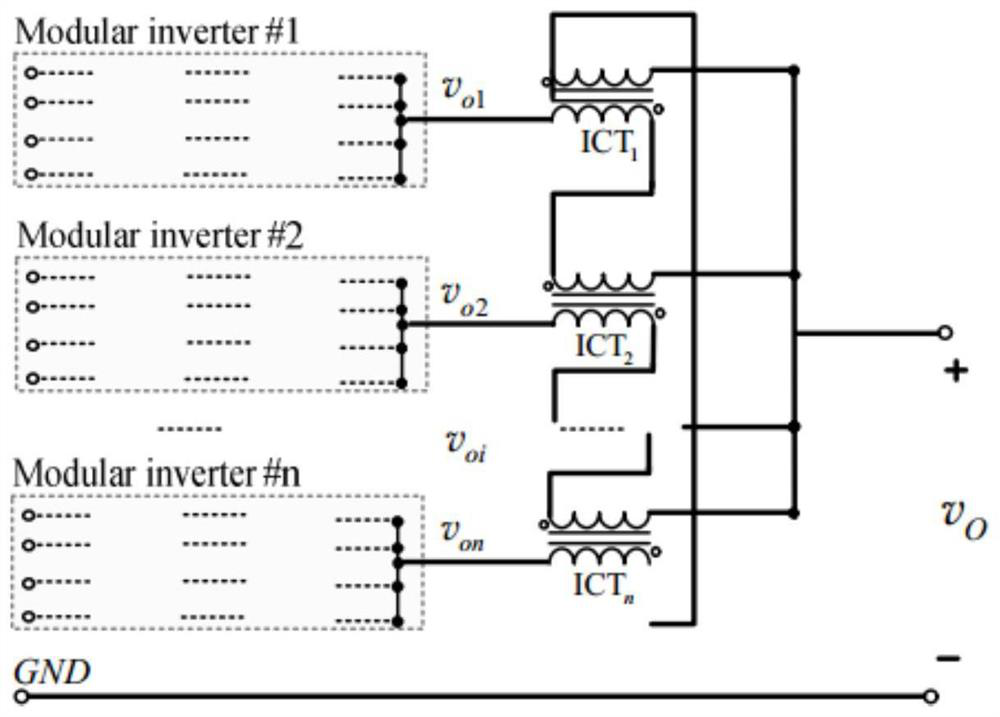

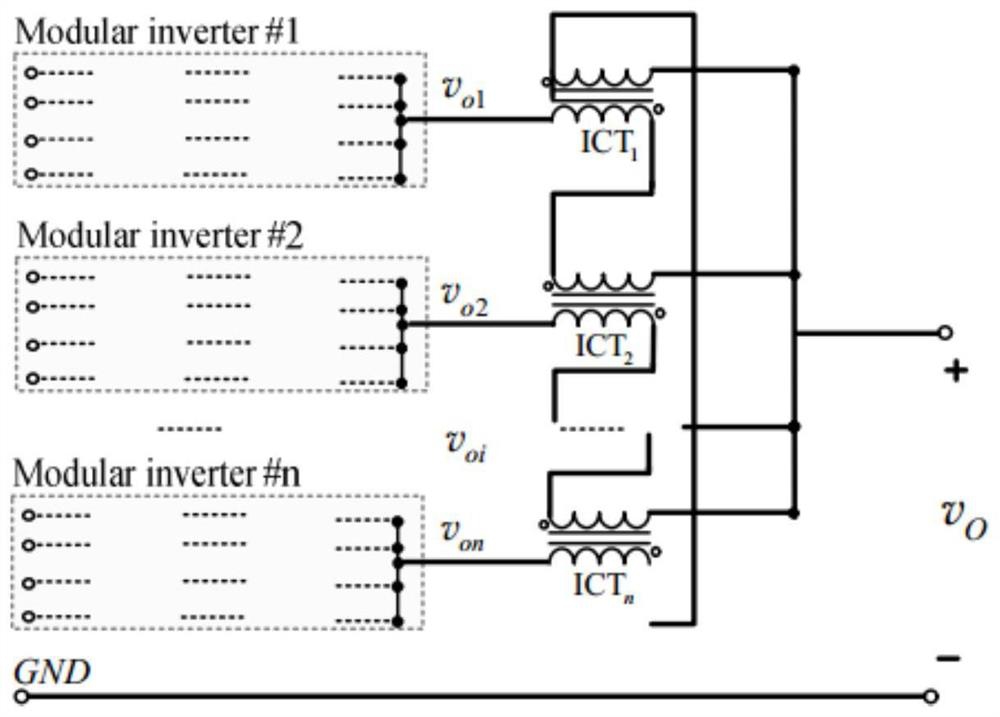

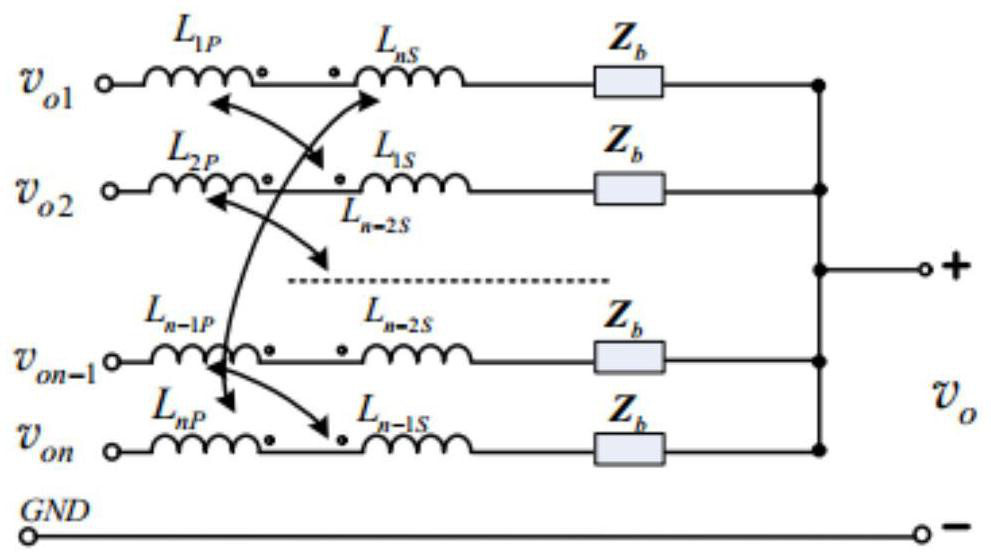

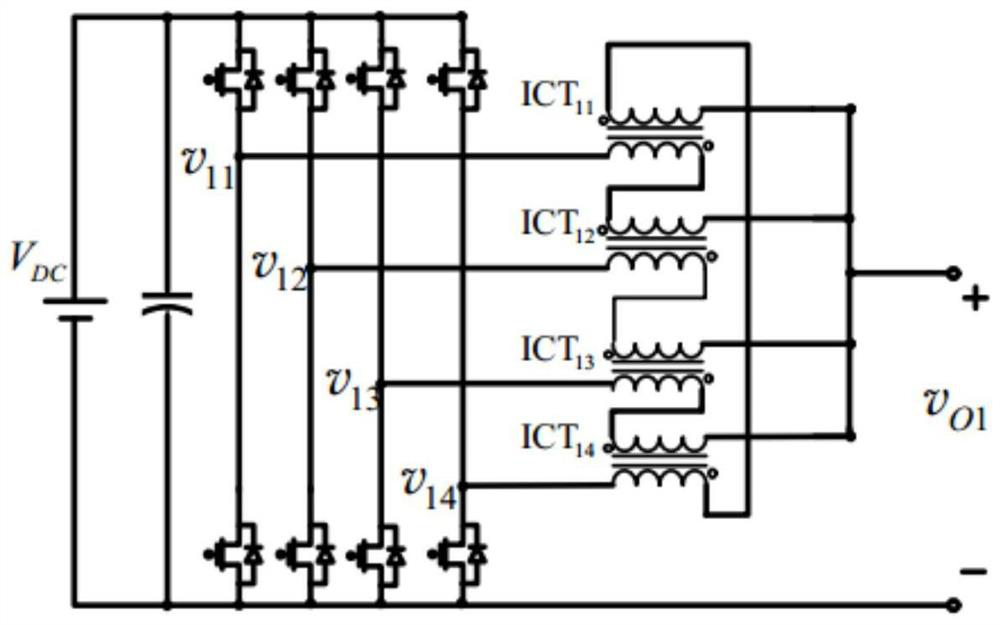

Phase synchronization detection method and device based on IPT parallel multiple inverters

ActiveCN112072941AAchieving Phase SynchronizationAc-dc conversionVoltage-current phase angleInverterHemt circuits

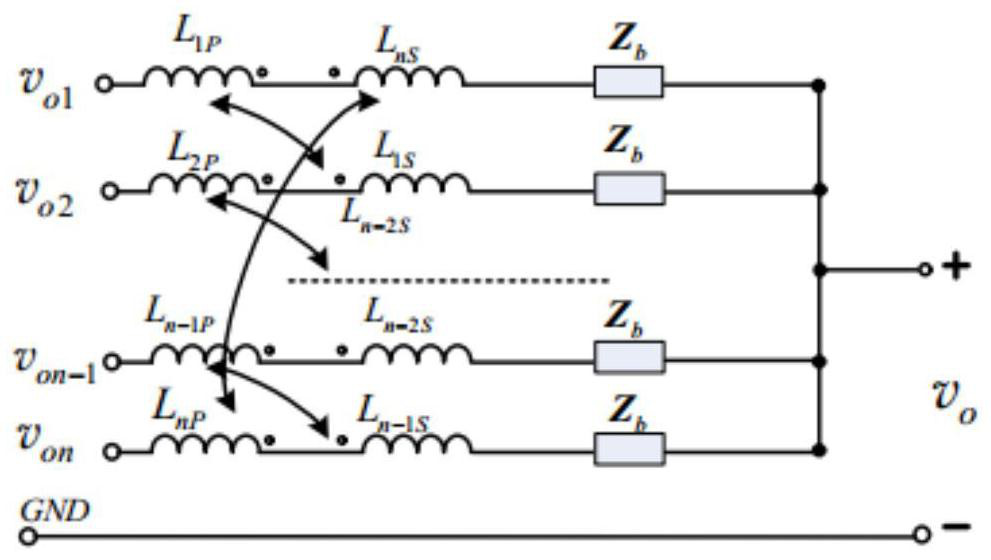

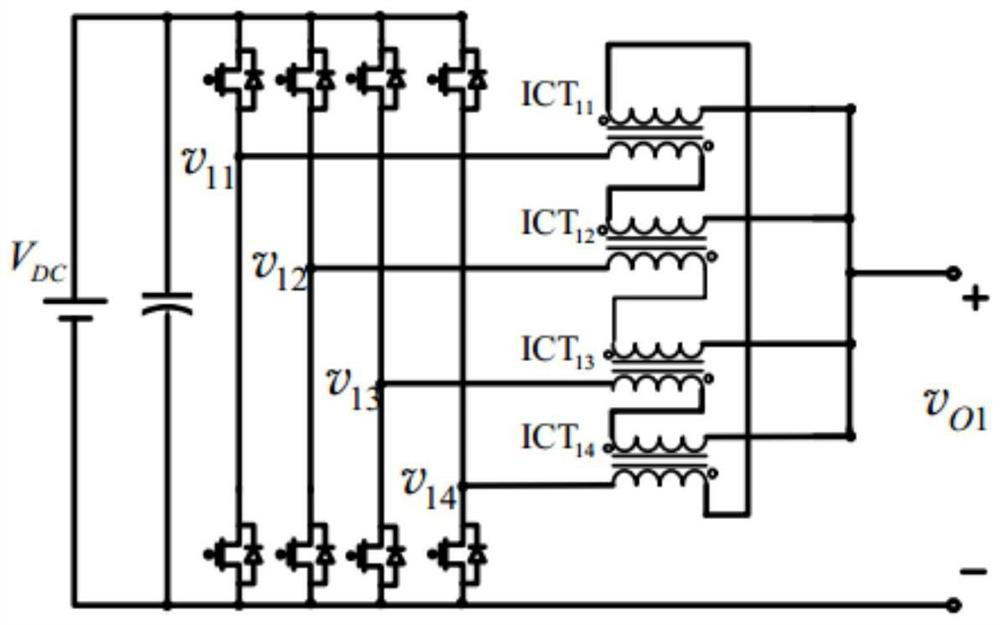

The invention provides a phase synchronization detection method and device based on IPT parallel multiple inverters. The device comprises: n inverter modules, wherein one inverter module is a main inverter module, and the other n-1 inverter modules are slave inverter modules; and n driving circuits which are respectively connected with n external coupling inductors ICTi in parallel, wherein i is greater than or equal to 1 and less than or equal to n, each drive circuit comprises four half-bridge switch arms, the four half-bridge switch arms are connected with four coupling inductors ICTij in parallel respectively, and j is larger than or equal to 1 and smaller than or equal to 4. The synchronization state of the inverter voltage phase is reflected according to the error between the inverter output phase and the average value of all the output phases, the output voltage phase is adjusted, phase synchronization of the multiple parallel inverters is achieved, and the function of correctlymeasuring the voltage phase of the multiple parallel inverters is achieved.

Owner:WUHAN UNIV

Multi-channel high-speed digital-to-analogue converter (DAC) synchronization method

ActiveCN102882673BAchieving Phase SynchronizationExpand signal output bandwidthSynchronisation signal speed/phase controlPhase differenceClock phase

The invention discloses a multi-channel high-speed digital-to-analogue converter (DAC) synchronization method, which comprises the following steps of: first generating a digital signal source reference signal, a synchronous clock signal and a resetting signal by using a field programmable gate array-MASTER (FPGA-MASTER), simultaneously transmitting the signals to an FPGA-SLAVEP and a DACM, and roughly adjusting multi-path delay, wherein P and M are positive integers; then performing FPGA-MASTER synchronous clock phase discrimination in the FPGA-SLAVEP, and regulating a phase difference to 0 by using a fine delay module; and finally performing DACM reference clock phase discrimination in the FPGA-SLAVEP, and regulating a phase difference to 0 by using the fine delay module. Output signals can be subjected to phase synchronization, a plurality of FPGAs and a plurality of high-speed DACs can be simultaneously cascaded without the limitation of clock speed of the DACs, and FPGA-SLAVEPs are used for performing phase discrimination and phase regulation on the FPGA-MASTER and the DACs to make the phases of data of the FPGA-MASTER, the FPGA-SLAVEs and the DACs consistent, so that the time sequence of each path of DAC is completely synchronous and controllable, working efficiency is improved, and a signal output bandwidth is expanded.

Owner:TSINGHUA UNIV

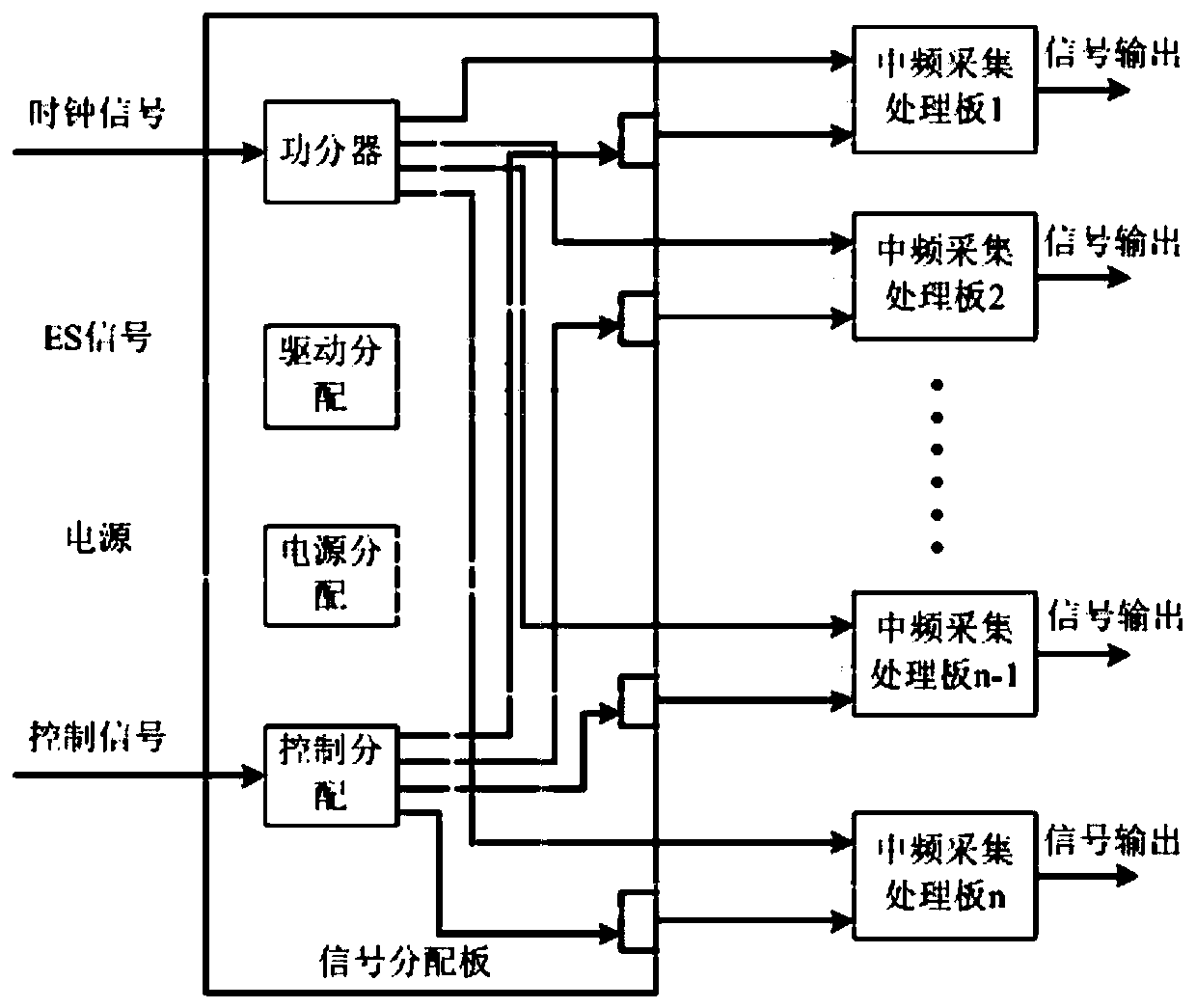

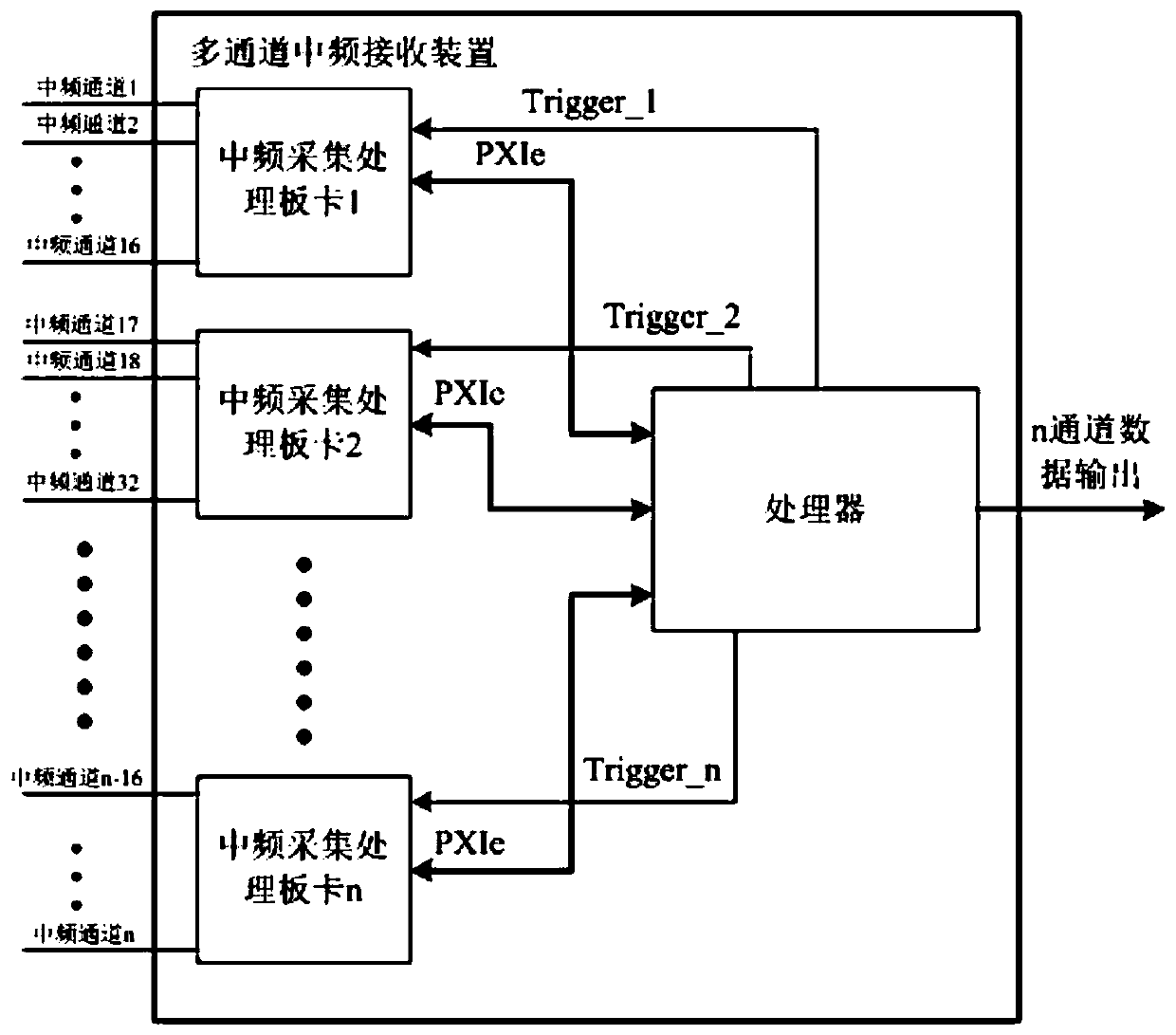

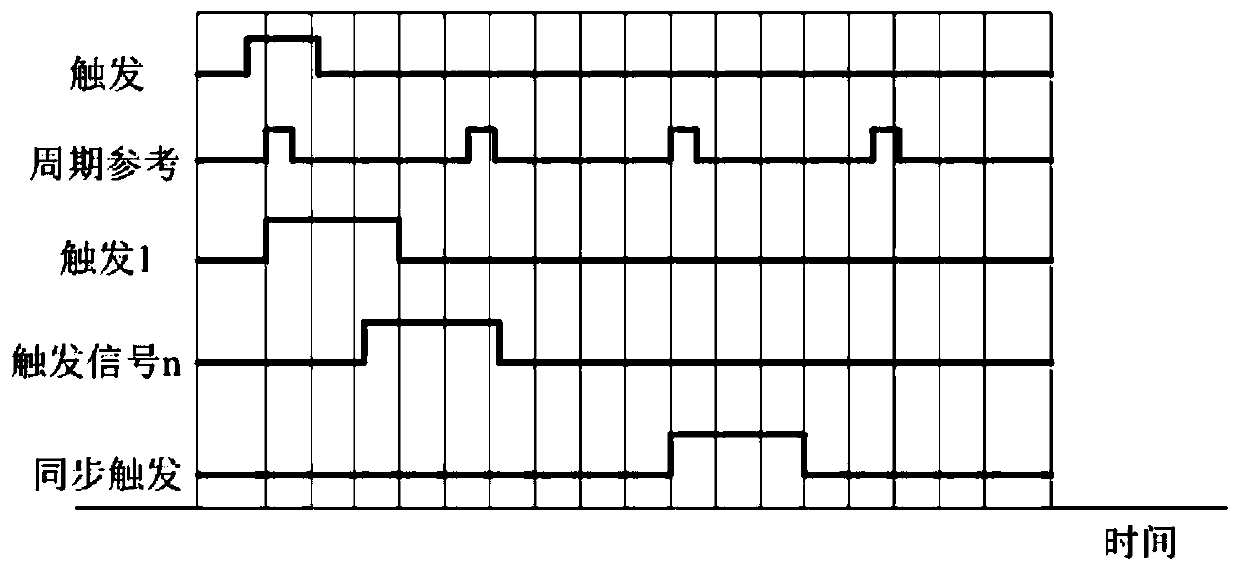

Multi-channel intermediate-frequency data synchronization processing method and system for array imaging

InactiveCN110426706AAchieving Phase SynchronizationImprove test efficiencyTransmissionRadio wave reradiation/reflectionTest efficiencyData synchronization

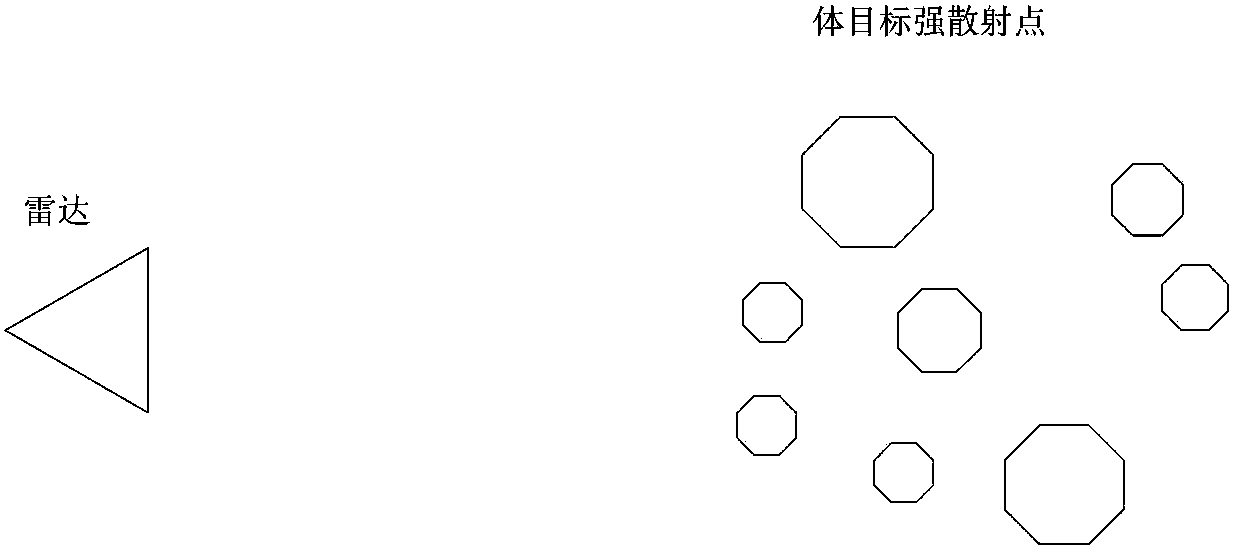

The disclosure provides a multi-channel intermediate-frequency data synchronization processing method and system for array imaging. A processor is connected to each intermediate-frequency acquisitionboard card through an acquisition trigger connecting wire; and the intermediate-frequency acquisition board cards connected with the processed by buses are used for interaction of multi-channel intermediate-frequency data. The processor receives trigger signals for sampling the intermediate-frequency data and sends the trigger signals to the intermediate-frequency acquisition board cards. After the intermediate-frequency acquisition board cards receive the trigger signals synchronously, ADC sampling is performed; and the processor processes the multi-channel data rapidly and synchronously. Compared with the existing multi-channel intermediate-frequency acquisition and digital processing method, the multi-channel intermediate-frequency data synchronization processing method and system havethe following beneficial effects: phase synchronization of multi-channel intermediate-frequency signal acquisition in array imaging is realized; rapid array imaging is realized by fast synchronous digital processing of acquired multi-channel data; and the imaging test efficiency is improved.

Owner:CHINA ELECTRONIS TECH INSTR CO LTD

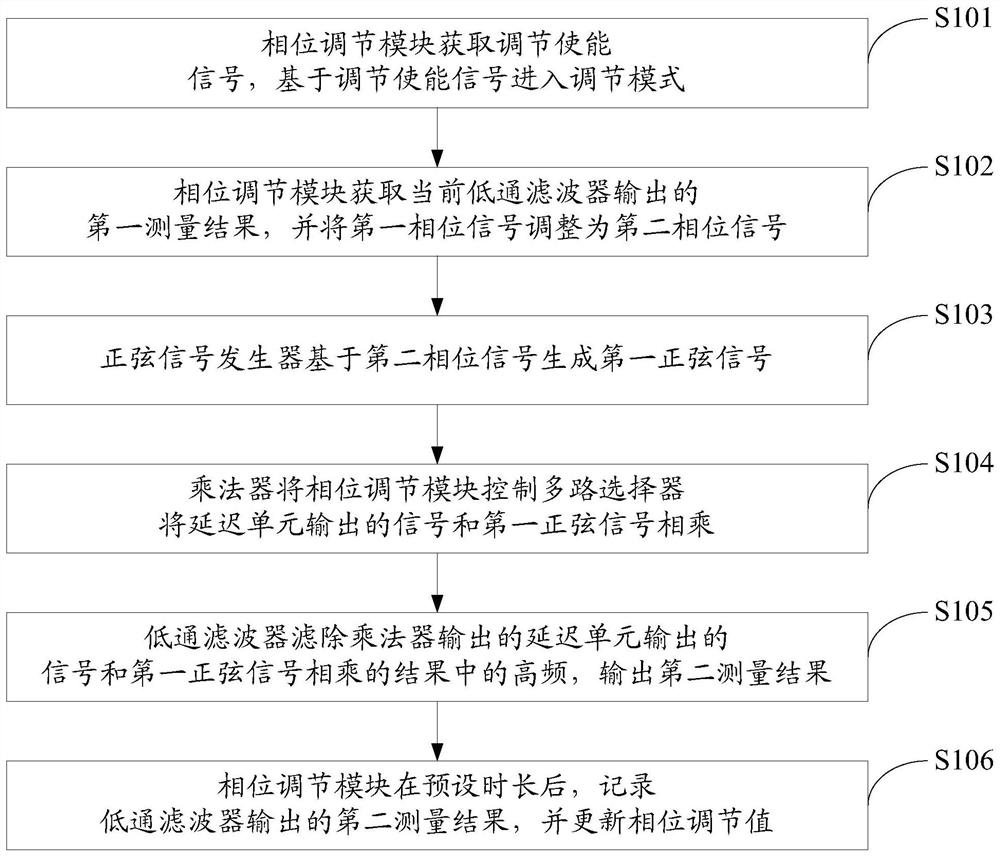

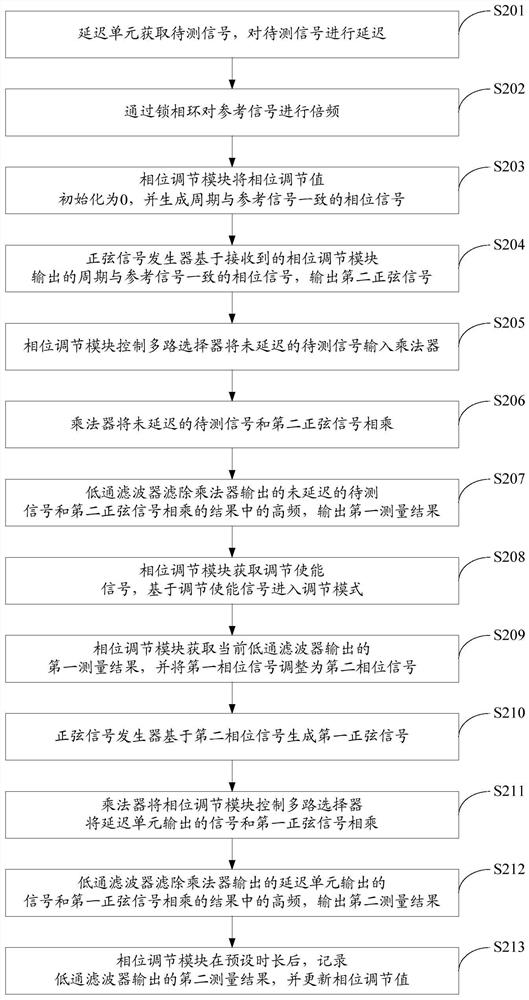

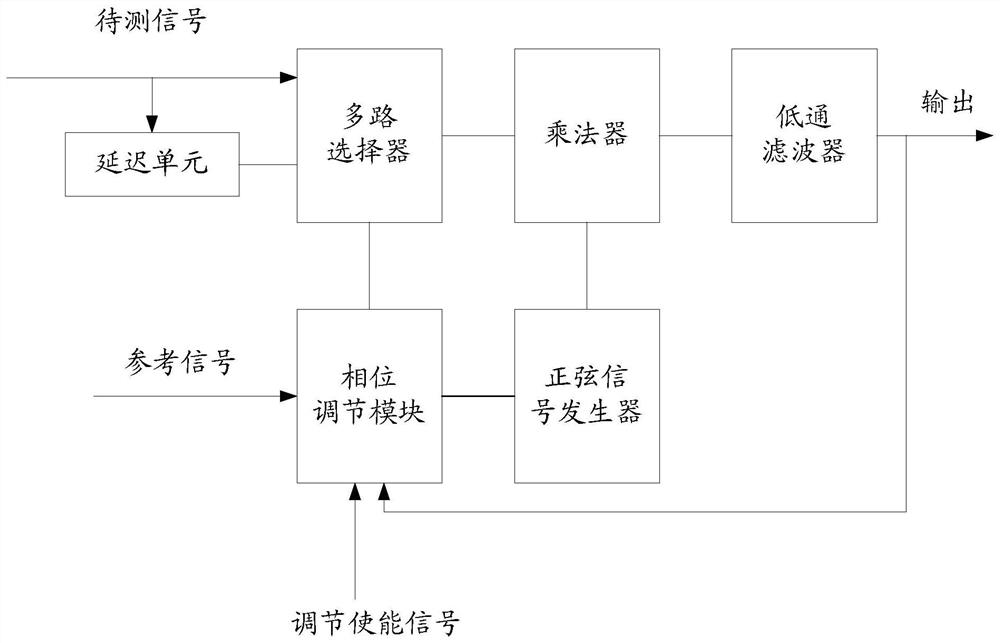

A digital lock-in amplifier phase synchronization method and system

ActiveCN110830037BAchieving Phase SynchronizationReduce power consumptionPulse automatic controlBinary multiplierLow-pass filter

The application discloses a method and system for phase synchronization of a digital lock-in amplifier. The method includes: the phase adjustment module obtains an adjustment enable signal, and enters an adjustment mode based on the adjustment enable signal; Measure the result, and adjust the first phase signal to the second phase signal; the sinusoidal signal generator generates the first sinusoidal signal based on the second phase signal; A sinusoidal signal is multiplied; the low-pass filter filters out the high frequency in the result of multiplying the signal output by the delay unit output by the multiplier and the first sinusoidal signal, and outputs the second measurement result; after a preset period of time, the phase adjustment module, A second measurement of the output of the low pass filter is recorded and the phase adjustment value is updated. The present application can effectively realize the phase synchronization of the digital lock-in amplifier and reduce resource consumption.

Owner:UNIV OF SCI & TECH OF CHINA

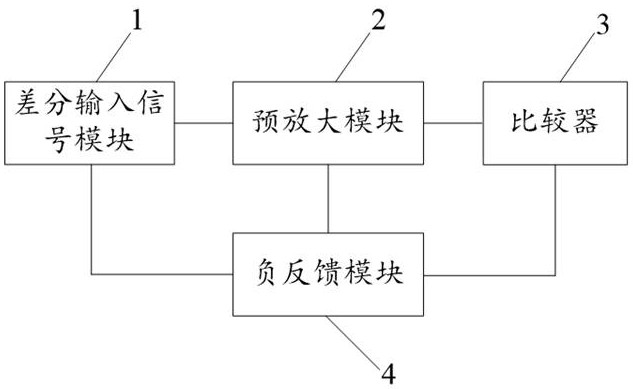

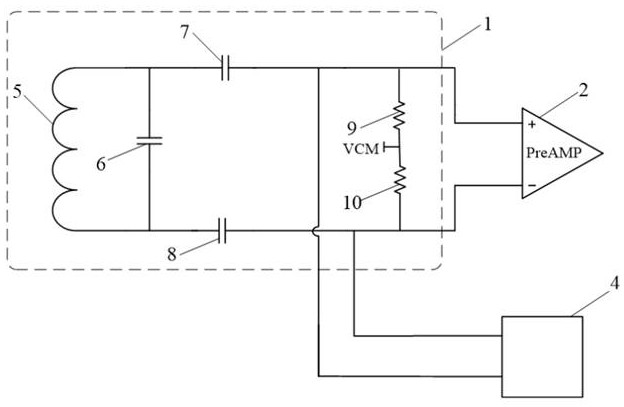

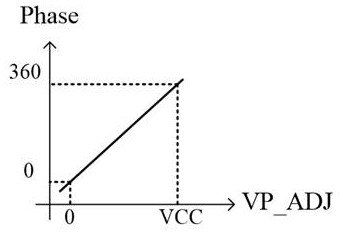

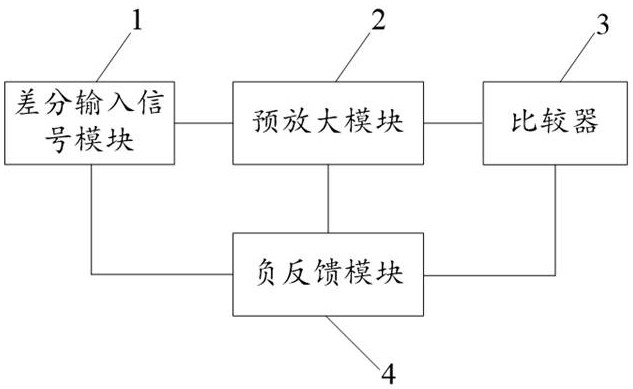

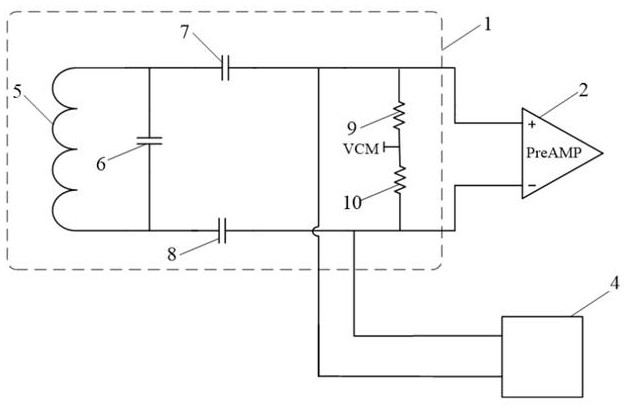

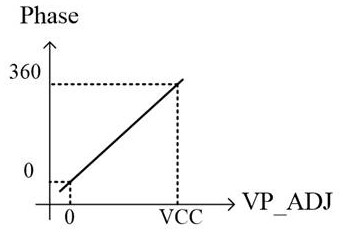

Device and method for clock signal recovery and NFC chip

ActiveCN113810893AAchieve recoveryAchieving Phase SynchronizationSynchronisation arrangementShort range communication serviceNegative feedbackElectrical connection

The invention relates to the technical field of wireless communication, and discloses a device for clock signal recovery. The device includes: a differential input signal module which is used for acquiring antenna voltage and generating a differential input signal according to the antenna voltage; a pre-amplification module, wherein the first end of the pre-amplification module is electrically connected with one end of the differential input signal module, and the pre-amplification module is used for amplifying the differential input signal; a comparator, wherein one end of the comparator is electrically connected with the second end of the pre-amplification module, and the comparator is used for comparing the amplified differential input signals to obtain clock signals; and a negative feedback module, wherein the first end of the negative feedback module is electrically connected with the other end of the differential input signal module, the second end of the negative feedback module is electrically connected with the third end of the pre-amplification module, the third end of the negative feedback module is electrically connected with the other end of the comparator, and the negative feedback module is used for adjusting an amplification parameter of the differential input signal according to the clock signal so as to recover the clock signal. The invention also discloses a method for clock signal recovery.and an NFC chip.

Owner:北京紫光青藤微系统有限公司

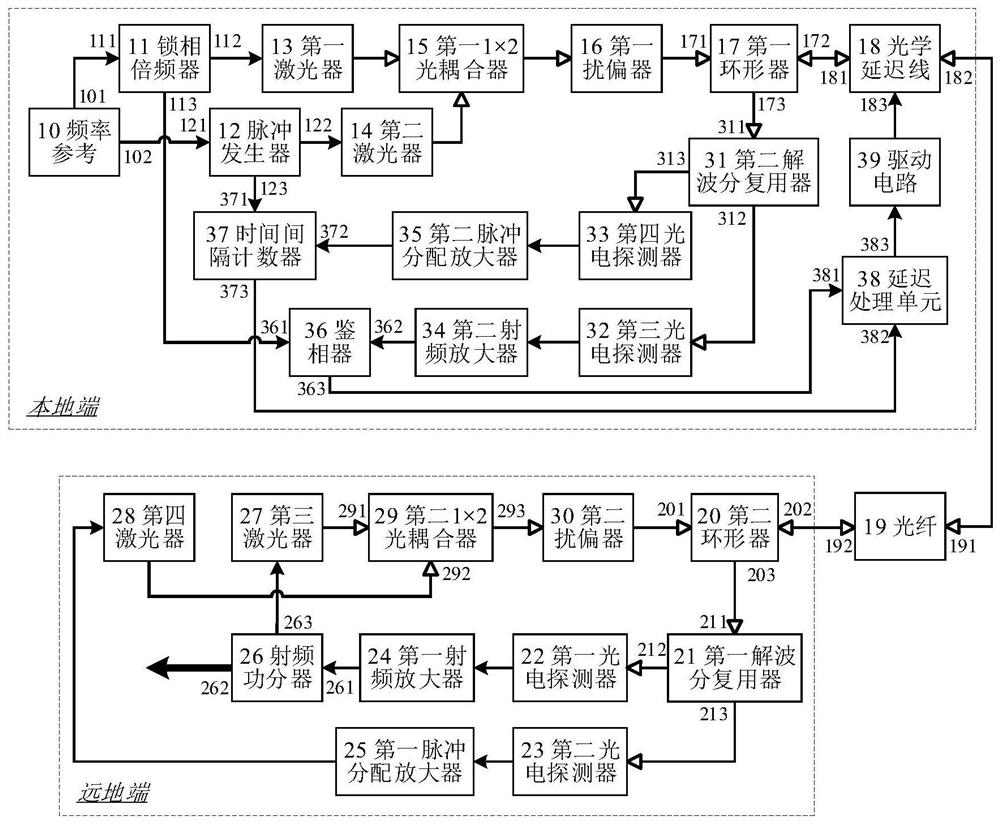

Optical Fiber Phase Synchronization System Based on Optical Active Compensation

ActiveCN113098623BPhase coincidenceImprove time-frequency transfer coherenceFibre transmissionElectromagnetic receiversPhotodetectorSoftware engineering

The invention discloses an optical fiber phase synchronization system based on optical active compensation, comprising: a frequency reference, a phase-locked frequency multiplier, a pulse generator, a laser, a 1×2 optical coupler, a polarization scrambler, a circulator, and an optical delay line , optical fiber, demultiplexer, photodetector, radio frequency amplifier, pulse distribution amplifier, radio frequency power divider, phase detector, time interval counter, delay processing unit, drive circuit. The present invention can ensure that the frequency signal phases are consistent under operations such as shutdown and restart or optical fiber routing change, and realize phase synchronization, thereby improving the coherence of time-frequency transmission and meeting the requirements of coherent detection applications such as distributed radar arrays.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

A clock synchronization method for devices in a local area network

ActiveCN110808807BAchieving Phase SynchronizationImplement fixesTime-division multiplexTime deviationProtocol design

A clock synchronization method for devices in a local area network. Based on the design idea of IEEE 1588 protocol, it collects the clock information of each device in the time management unit through the round-trip message; calculates the phase deviation and the frequency correction coefficient of the device according to the time of each device and the information of the time management unit; The frequency correction coefficient is associated with the device number to generate a relative time deviation list, which is sent to each device that needs to be synchronized; the device queries the relative deviation time list according to its own device number and the destination device number to obtain the frequency correction coefficient of the device and the time difference between the device and the destination device. The relative time deviation can realize the synchronization of the clock phase and the correction of the frequency. The invention not only optimizes the problem of heavy load caused by the IEEE 1588 protocol synchronization process and the possible long clock synchronization execution period, but also proposes a list-based clock frequency synchronization method during the time synchronization process.

Owner:CIVIL AVIATION UNIV OF CHINA

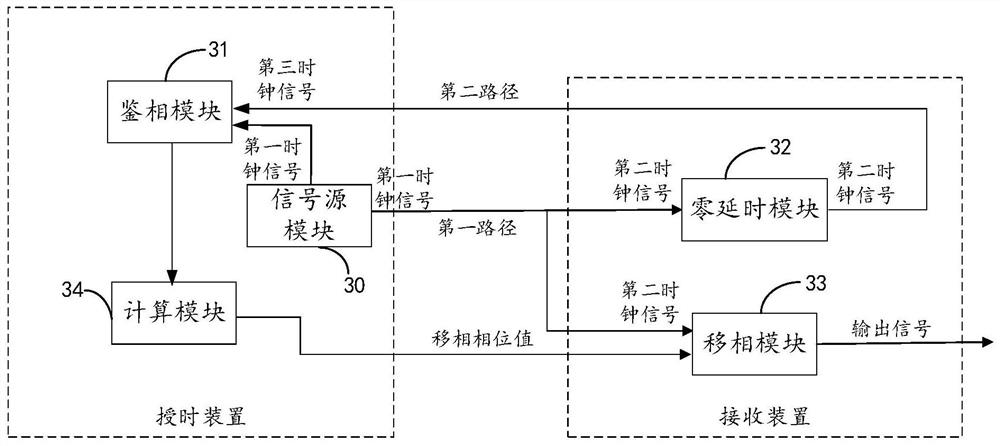

Phase synchronization method, device and terminal

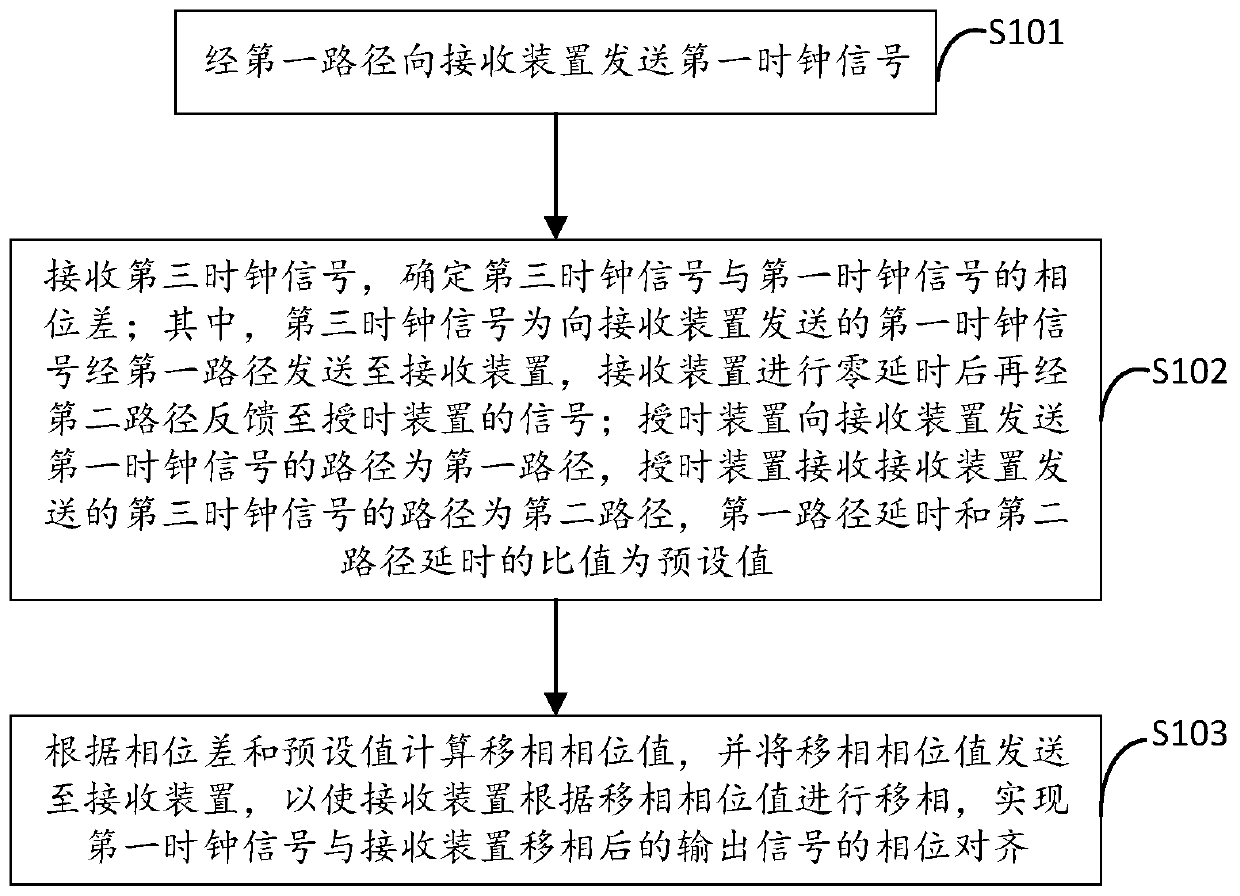

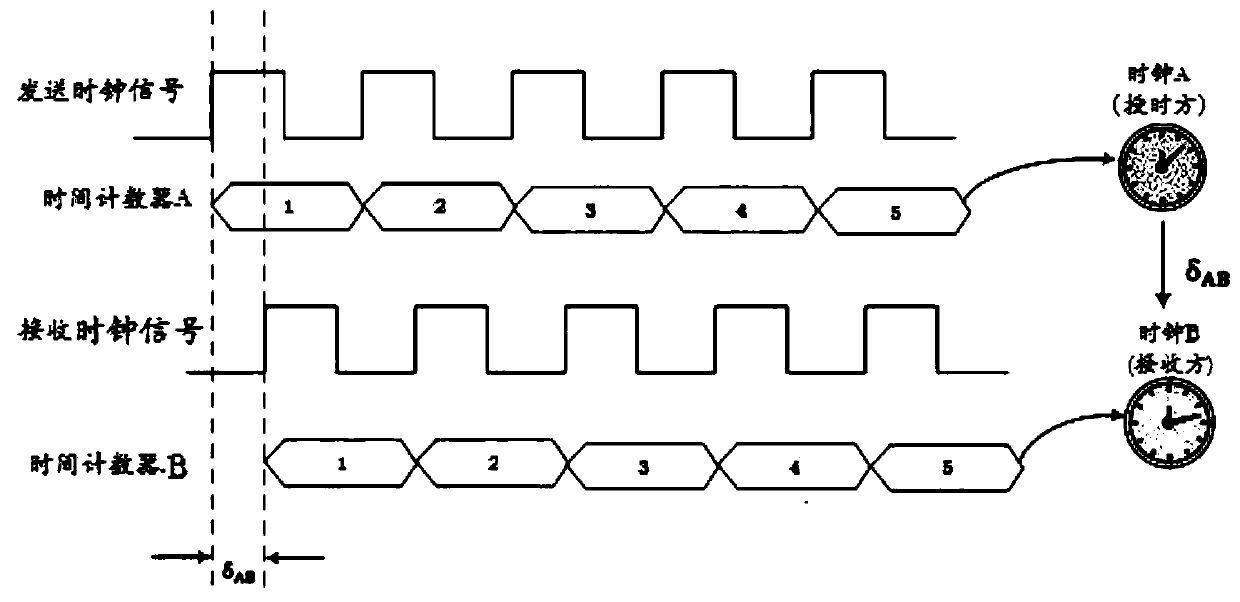

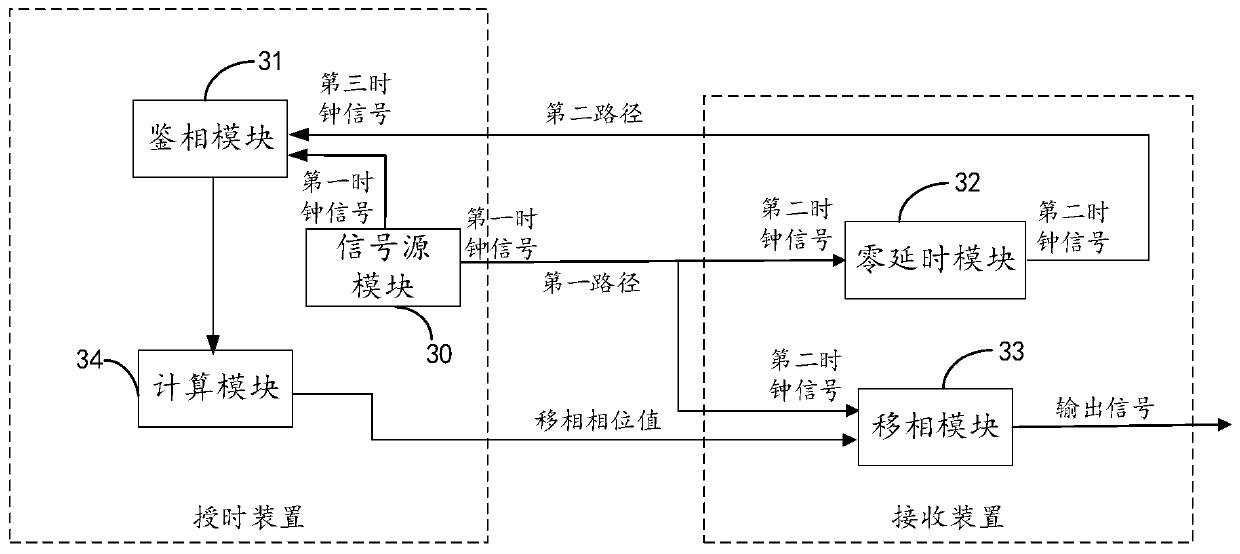

ActiveCN110611950AAchieving Phase SynchronizationAchieving Phase AlignmentSynchronisation arrangementPhase shiftedPath delay

The invention provides a phase synchronization method, a device and a terminal, and relates to the technical field of time service, the phase synchronization method comprises the following steps: sending a first clock signal to a receiving device; detecting a phase difference between the first clock signal and a third clock signal sent by a zero delay module; performing feedback of the second clock signal to the time service device through zero delay of the second clock signal; setting the ratio of the first path delay to the second path delay as a preset value, and obtaining a phase shift value according to the preset value and the phase difference; realizing phase shift of the second clock signal according to the phase shift value so as to realize phase alignment of the first clock signal and the output signal; phase synchronization of the output signal of the time service device and the output signal of the receiving device can be realized, errors caused by phase introduction are reduced, and the time service precision is improved.

Owner:UTSTARCOM TELECOM CO LTD

A time-division power multiplier and its realization method

ActiveCN111398884BSmall phase differenceImprove accuracyElectrical measurementsConvertersHemt circuits

Owner:国网山东省电力公司营销服务中心(计量中心) +4

Phase synchronization method, device and terminal

ActiveCN110611950BAchieving Phase SynchronizationAchieving Phase AlignmentSynchronisation arrangementPathPingComputer science

The present invention provides a phase synchronization method, device and terminal, which relate to the technical field of time service. The phase synchronization method includes: sending a first clock signal to a receiving device; detecting the first clock signal and the third clock sent by a zero-delay module The phase difference of the signal; through the zero delay of the second clock signal, and the second clock signal is fed back to the timing device; the ratio of the first path delay and the second path delay is also set as a preset value, according to the preset Set the value and the phase difference to obtain the phase-shifting phase value; realize the phase-shifting of the second clock signal according to the phase-shifting phase value, thereby realizing the phase alignment of the first clock signal and the output signal; the present invention can realize the output signal of the timing device and the output of the receiving device The phase synchronization of the signal reduces the error introduced by the phase and improves the timing accuracy.

Owner:UTSTARCOM TELECOM CO LTD

Device and method for clock signal recovery, nfc chip

ActiveCN113810893BAchieve recoveryAchieving Phase SynchronizationSynchronisation arrangementShort range communication serviceNegative feedbackElectrical connection

The present application relates to the technical field of wireless communication, and discloses a device for recovering a clock signal. Including: a differential input signal module, which is used to obtain the antenna voltage and generate a differential input signal according to the antenna voltage; a pre-amplification module, the first end of which is electrically connected to one end of the differential input signal module; the pre-amplification module is used to amplify the differential input signal; A comparator, one end is electrically connected to the second end of the pre-amplification module, the comparator is used to compare the amplified differential input signal to obtain a clock signal; the negative feedback module, the first end is electrically connected to the other end of the differential input signal module, The second end of the negative feedback module is electrically connected to the third end of the pre-amplification module, and the third end of the negative feedback module is electrically connected to the other end of the comparator; the negative feedback module is used to perform the amplification parameter of the differential input signal according to the clock signal adjustment to achieve recovery of the clock signal. The application also discloses a method for recovering a clock signal and an NFC chip.

Owner:北京紫光青藤微系统有限公司

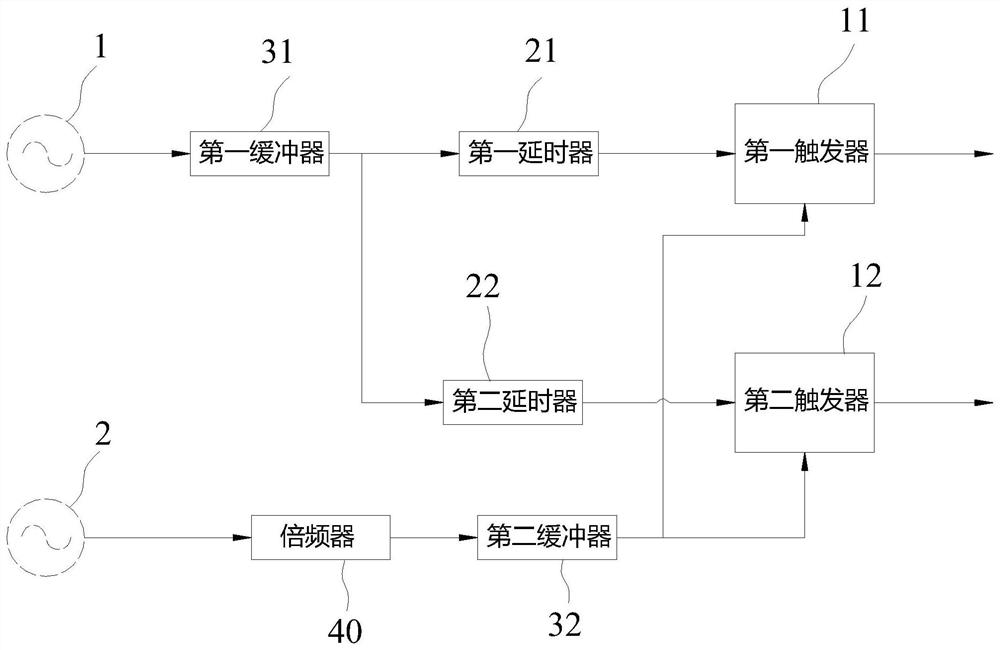

Phase synchronization device and method

PendingCN112202446AAchieving Phase SynchronizationReduce purchasesPulse automatic controlHigh level techniquesSynchronizerFilter (signal processing)

The invention discloses a phase synchronization device and method. The phase synchronization device comprises a first trigger and a second trigger, wherein a receiving end of the first trigger is connected with a first signal source, a clock signal end of the first trigger is connected with a second signal source, a receiving end of the second trigger is connected with the first signal source, anda clock signal end of the second trigger is connected with the second signal source. Therefore, on one hand, the situation that the system performance is reduced due to different phases of two signals is avoided, and the working performance of the system is guaranteed; on the other hand, a crystal oscillator, a filter and other components do not need to be arranged to additionally generate squarewaves to serve as clock control signals, purchase of the components is reduced, and the signal processing cost is reduced.

Owner:北京三中科技有限公司

A method for measuring and compensating a power quality device

ActiveCN110488092BAchieving Phase SynchronizationHigh measurement accuracySpectral/fourier analysisVoltage-current phase angleVoltage amplitudePower quality

The invention discloses a method for measuring and compensating a power quality device. The method comprises the steps of: obtaining the fundamental wave and harmonics of the power quality device after harmonic analysis; obtaining the theoretical conversion coefficient of voltage and the theoretical conversion coefficient of current; obtaining the automatic Calibrate the voltage amplitude compensation coefficient, automatically calibrate the current amplitude compensation coefficient, automatically calibrate the voltage phase compensation coefficient and automatically calibrate the current phase compensation coefficient; obtain the voltage interval amplitude compensation coefficient and the current interval amplitude compensation coefficient; obtain the voltage frequency phase compensation coefficient and current frequency phase compensation coefficient; obtain the voltage temperature amplitude compensation coefficient and current temperature amplitude compensation coefficient; calculate the amplitude and phase of the compensated fundamental wave voltage, the amplitude and phase of the compensated fundamental wave current, and the compensated harmonic The amplitude and phase of the voltage, the amplitude and phase of the compensated harmonic current. The invention can realize the phase synchronization of the power quality device and effectively improve the measurement accuracy of the power quality device.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD +1

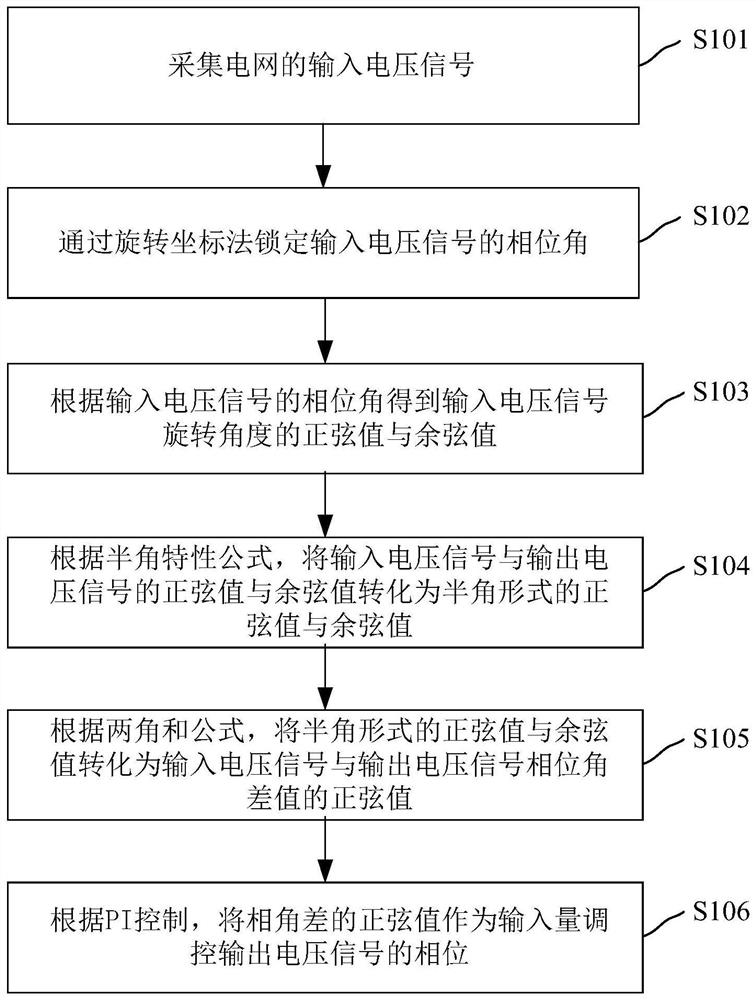

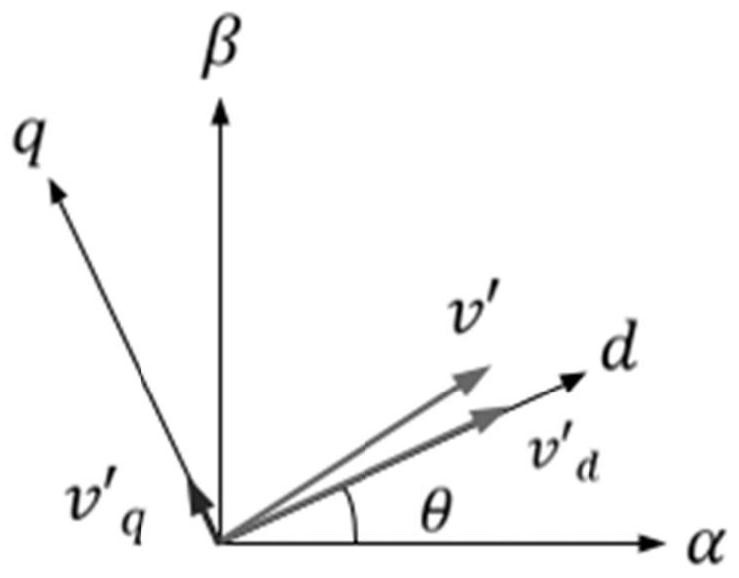

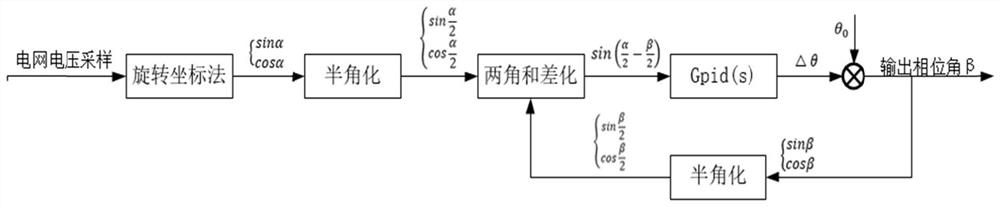

Energy storage inverter phase synchronization method based on half-angle characteristic

PendingCN114865710AGuaranteed stabilitySmall phase differenceSingle network parallel feeding arrangementsPhotovoltaic energy generationInverterPower grid

The invention discloses an energy storage inverter phase synchronization method based on a half-angle characteristic, and the method comprises the steps: collecting an input voltage signal of a power grid, locking a phase angle of the input voltage signal through a rotation coordinate method, and obtaining a sine value and a cosine value of a rotation angle of the input voltage signal according to the phase angle of the input voltage signal; according to a half-angle characteristic formula, sine values and cosine values of the input voltage signal and the output voltage signal are converted into sine values and cosine values in a half-angle form; converting the sine value and the cosine value in the half-angle form into a sine value of a phase angle difference value of the input voltage signal and the output voltage signal according to a two-angle sum formula; and according to PI control, taking the sine value of the phase angle difference as an input quantity to regulate and control the phase of the output voltage signal. According to the invention, phase synchronization of the power grid before grid connection of the inverter is realized, the phase difference between the inverter synchronization signal and the power grid signal is reduced, the current generated due to the voltage difference during grid connection is reduced, and the stability of the inverter is improved.

Owner:GUANGZHOU SANJING ELETRIC

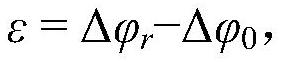

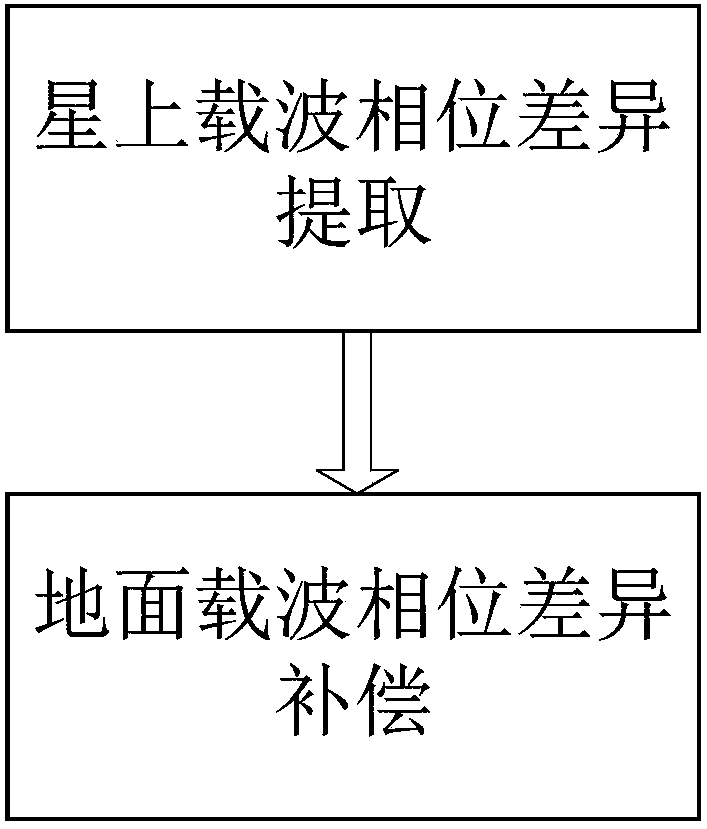

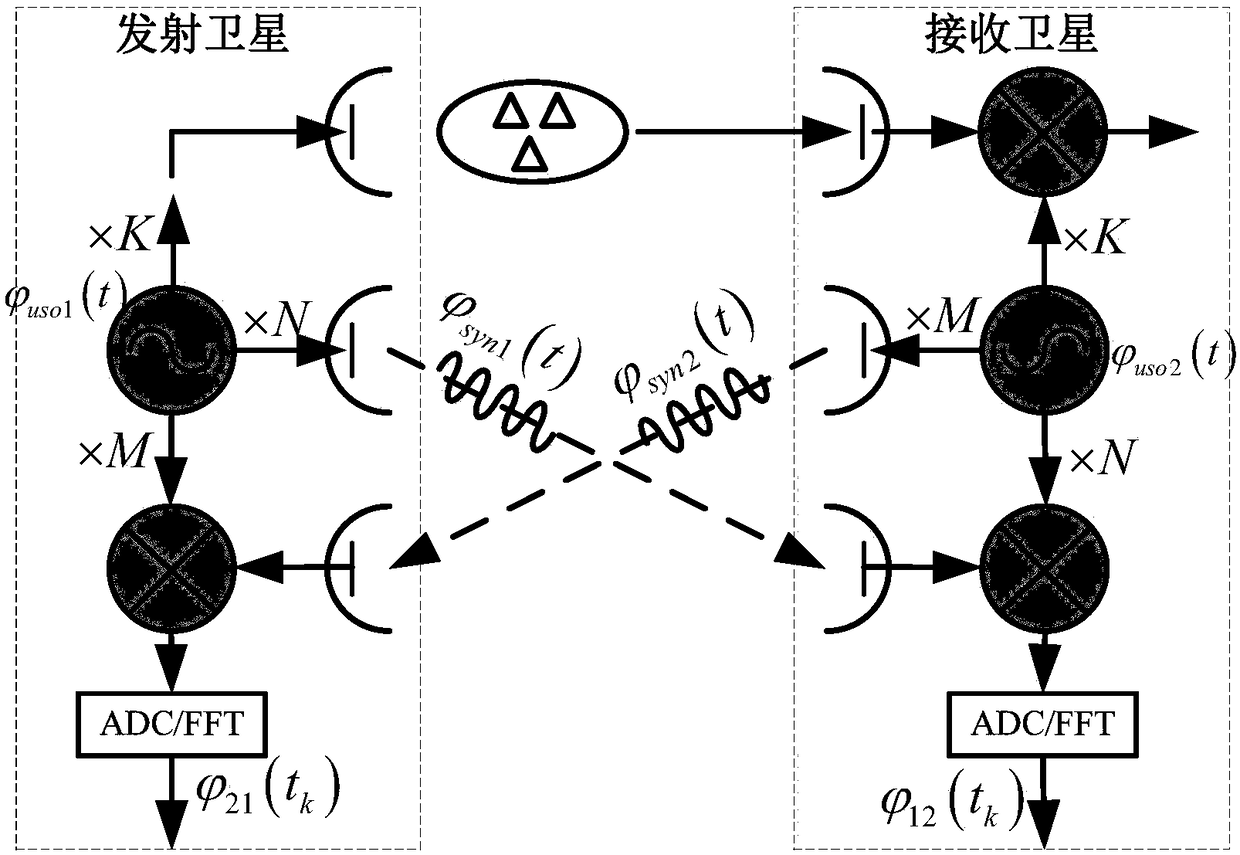

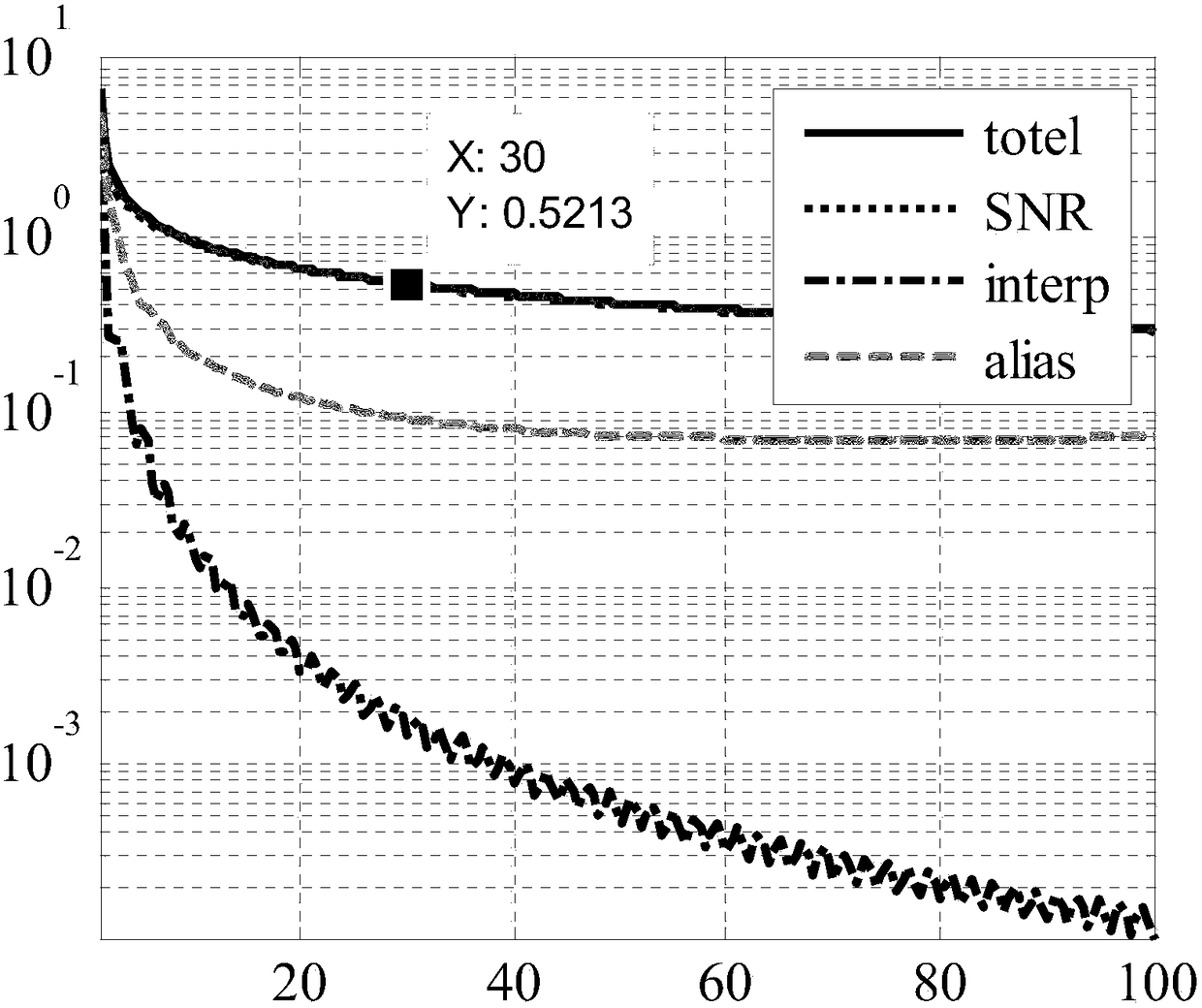

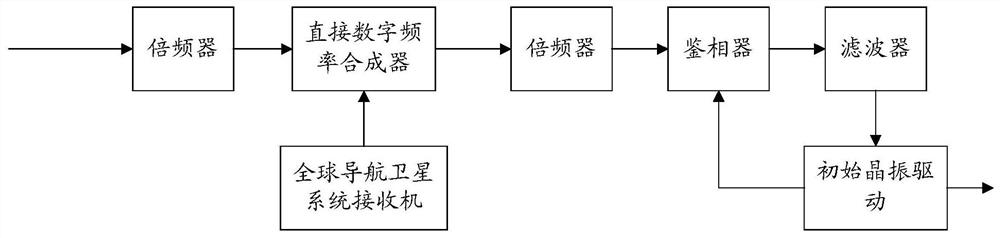

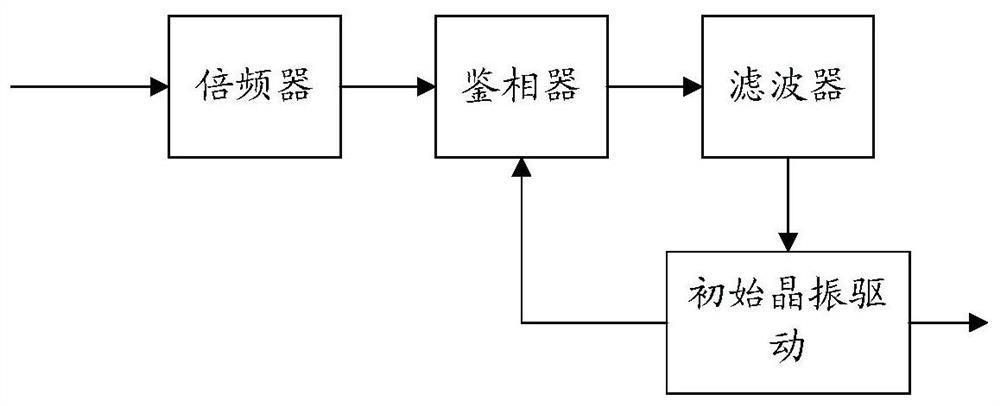

A phase synchronization method for fmcw SAR based on distributed satellites

ActiveCN106019278BHigh measurement frequencyImprove Phase Synchronization AccuracyRadio wave reradiation/reflectionFrequency spectrumPhase difference

The invention provides an FMCW SAR phase synchronization method based on distributed satellites. The method comprises the following steps: at any time t, emission satellite output signals are emitted after being respectively subjected to K frequency multiplication and N frequency multiplication; and then frequency mixing with carrier frequency signals is carried out after M frequency multiplication, and emission-end carrier wave phase differences are obtained through frequency spectrum peak extraction. One path of receiving satellite output signals are subjected to frequency mixing with echo signals after K frequency multiplication, and thus dual-station echo signals are obtained; one path of the receiving satellite output signals are emitted after M frequency multiplication; and one path of the receiving satellite output signals are subjected to frequency mixing with the received emission signals after N frequency multiplication, and receiving-end carrier wave phase differences are obtained through frequency spectrum peak extraction. According to the invention, the emission-end carrier wave phase differences and the receiving-end carrier wave phase differences at any time t can be obtained by use of such a process, and compensation phases of the dual-station echo signals are obtained after difference processing is performed on the emission-end carrier wave phase differences and the receiving-end carrier wave phase differences. According to the invention, the measurement frequency of the carrier wave phase differences can be improved, and the phase synchronization precision is improved.

Owner:NAT UNIV OF DEFENSE TECH

A phase synchronization method and device

ActiveCN108833071BAchieving Phase SynchronizationImprove image qualitySynchronisation arrangementRadio transmissionInformation processingTelecommunications

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

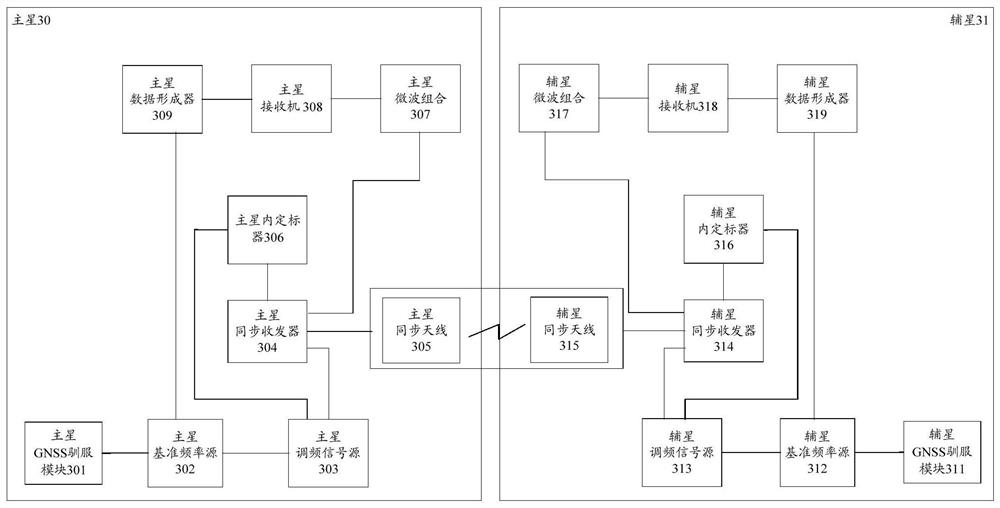

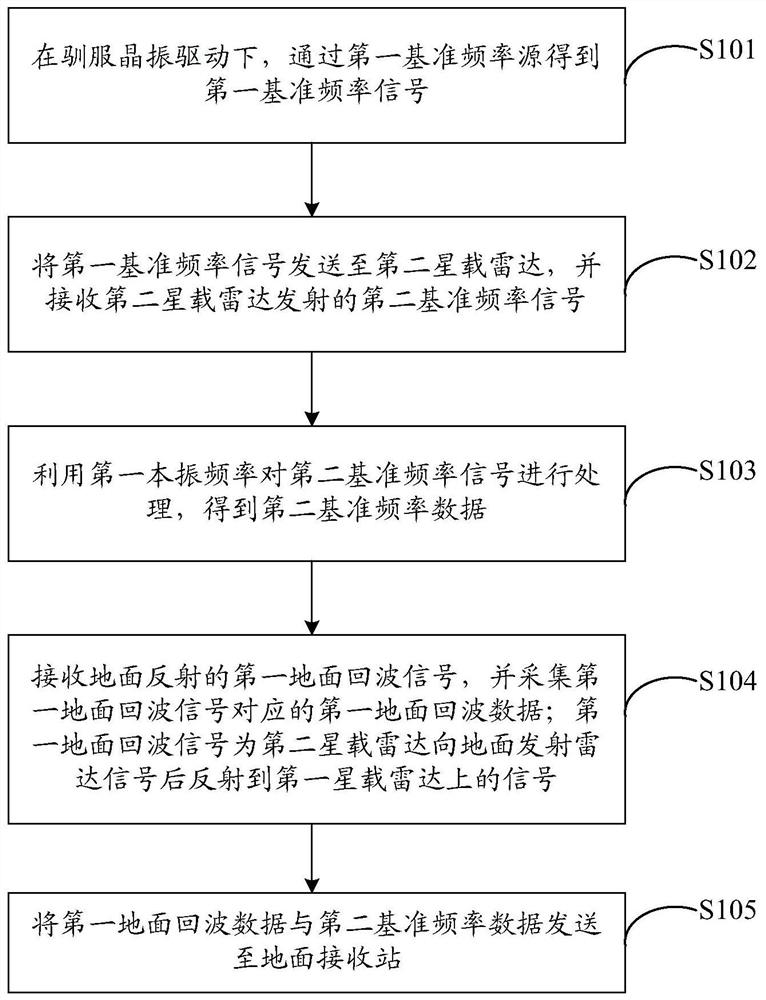

Phase synchronization method, spaceborne radar and ground receiving station

PendingCN113406621AAchieving Phase SynchronizationReduce frequency deviationRadio wave reradiation/reflectionICT adaptationTelecommunicationsRadar signals

The embodiment of the invention provides a signal synchronization method, a spaceborne radar and a ground receiving station, and is applied to a first spaceborne radar, and the method comprises the steps: obtaining a first reference frequency signal through a first reference frequency source under the drive of a taming crystal oscillator; sending the first reference frequency signal to a second spaceborne radar, and receiving a second reference frequency signal transmitted by the second spaceborne radar; processing the second reference frequency signal by using the first local frequency to obtain second reference frequency data; receiving a first ground echo signal reflected by the ground, and collecting first ground echo data corresponding to the first ground echo signal, wherein the first ground echo signal is a signal reflected to the first spaceborne radar after the second spaceborne radar transmits a radar signal to the ground; and sending the first ground echo data and the second reference frequency data to a ground receiving station.

Owner:AEROSPACE INFORMATION RES INST CAS

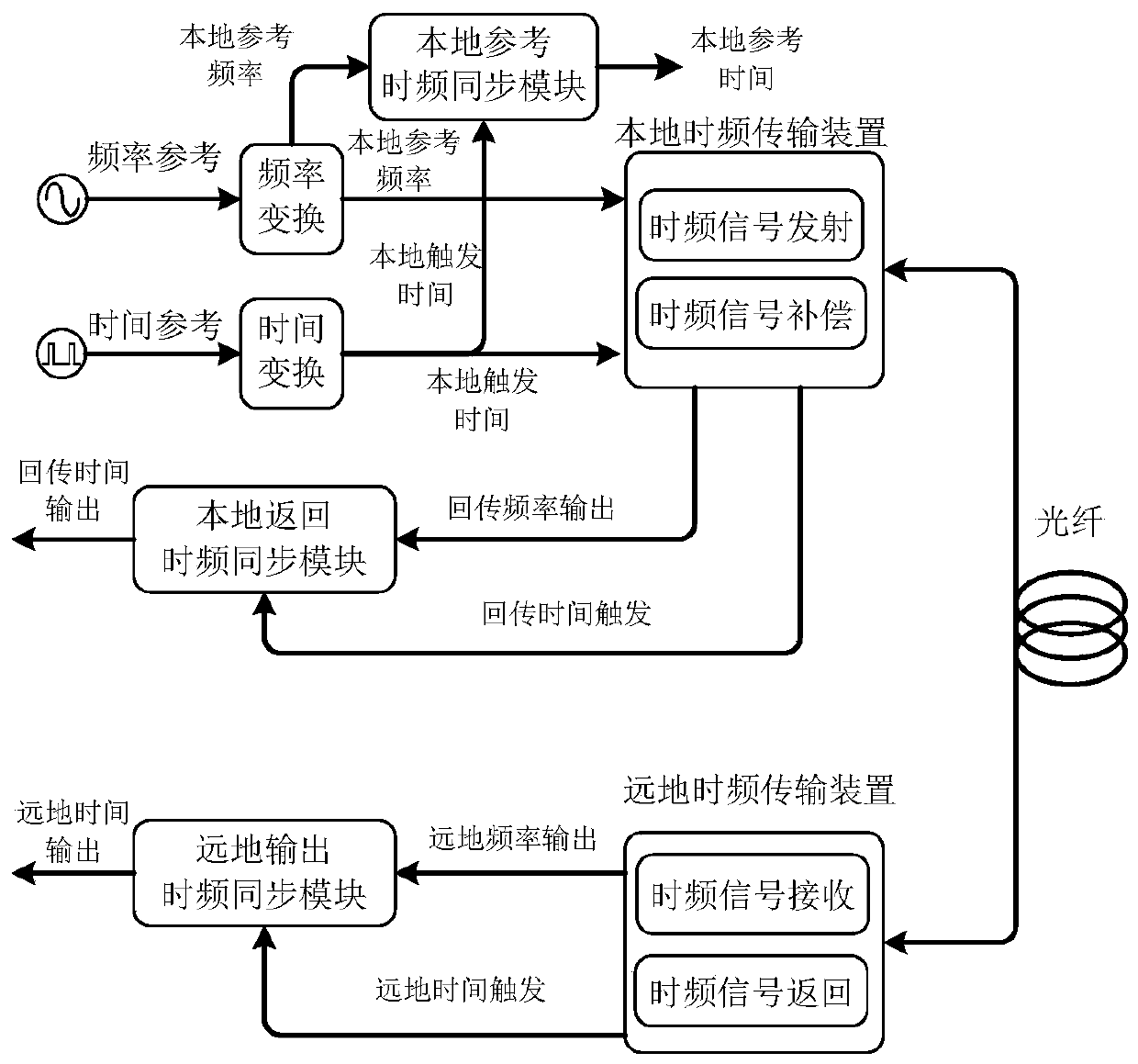

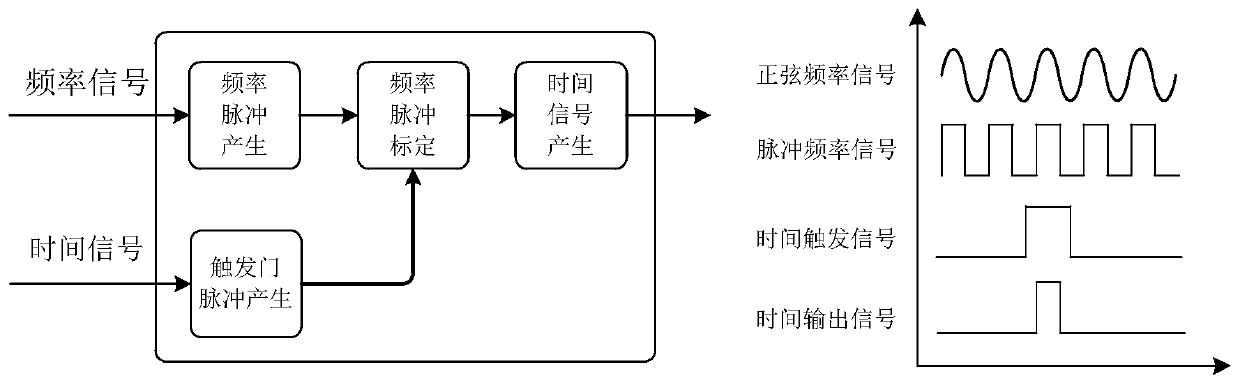

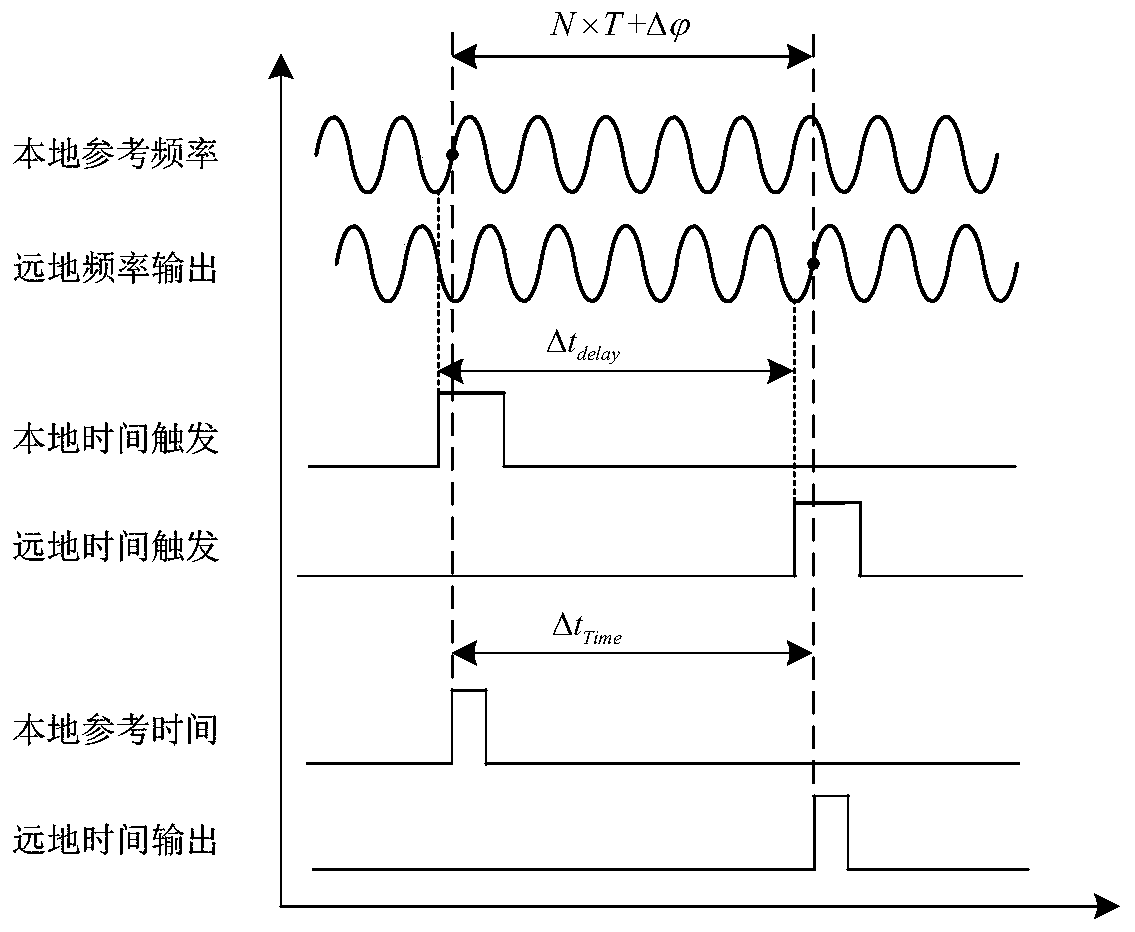

High-precision optical fiber time transfer system and method

ActiveCN110224776BAvoid time jitterHigh transfer accuracyTime-division multiplexFibre transmissionLow jitterTime transfer

The invention discloses a high-precision optical fiber time transmission system which comprises a local reference frequency signal generation module, a local trigger time signal generation module, a local high-precision time frequency synchronization module, a local time frequency transmission device, a local return time frequency synchronization module, a far-earth time frequency transmission device and a far-earth high-precision time frequency synchronization module. The system is based on a high-precision time signal generation and transmission technology of time frequency signal phase synchronization. Phase locking of the demodulated and recovered time signal and the demodulated and recovered frequency signal is achieved through the high-precision time-frequency synchronization module,a low-jitter time signal synchronous with the phase of the frequency signal in real time is generated, and transmission of the high-precision time signal is achieved while the time signal is output.Meanwhile, the invention provides a high-precision optical fiber time transmission method. According to the invention, the phase locking of the rising edge of the time signal and the sine frequency signal is realized, and the high-stability frequency signal is utilized to generate the low-jitter time signal synchronous with the phase of the high-stability frequency signal, so that the high-precision transmission of the time signal is realized.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

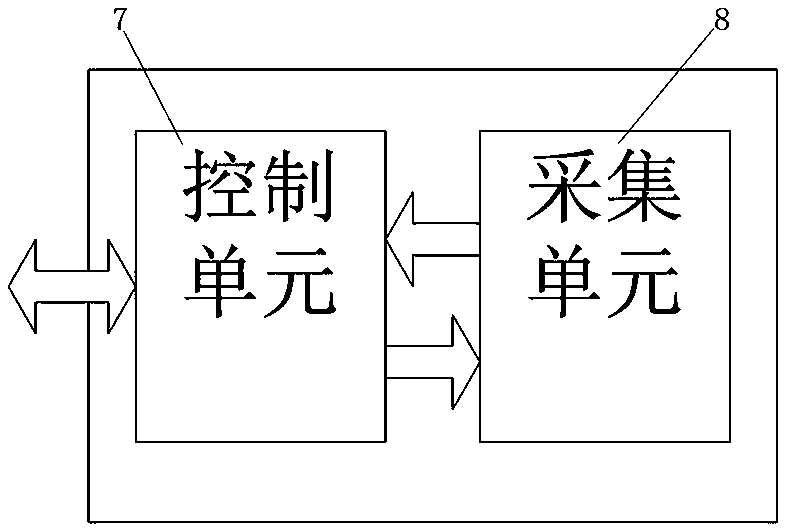

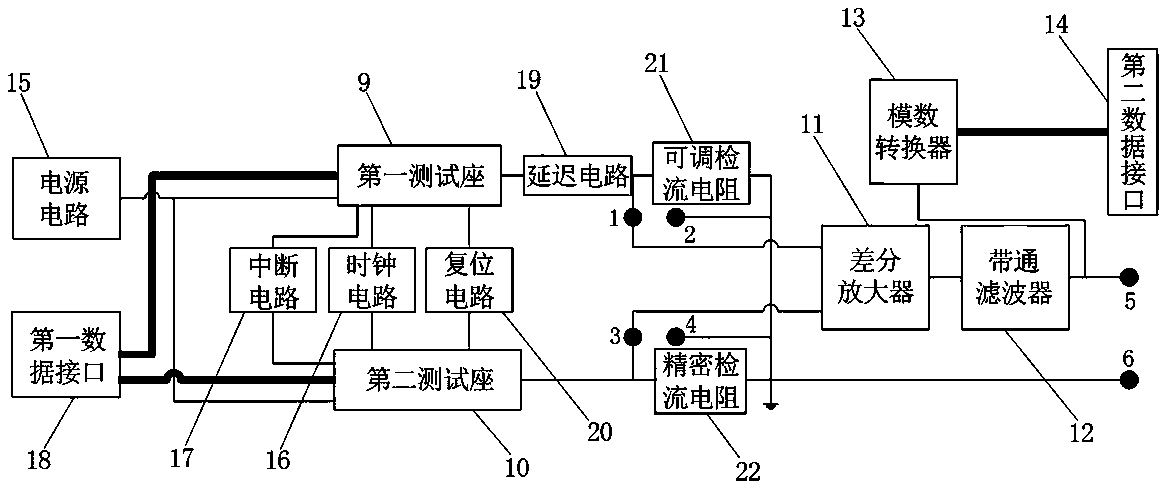

Integrated Circuit Bypass Signal Differential Amplification Sampling System and Acquisition Method

InactiveCN105739338BQuality improvementReduce distractionsPc applicationsProgramme control in sequence/logic controllersBand-pass filterEngineering

The invention relates to an integrated circuit bypass signal difference amplification sampling system and an acquisition method. The sampling system comprises a control unit and a collection unit; the control unit is connected to a collection unit through a first data port for controlling the collection process of the collection unit, transmitting a collection stop signal, regulating delaying parameters and filter parameters, receiving collected a digital bypass signals, and performing data interaction with the upper computer through the second data port; the collection unit comprises a first test socket for inserting the detected integrated circuit chip, a second test socket for inserting the safety chip, a difference amplifier, a band pass filter, an analog-to-digital converter and a second data port; and the first test socket and a second test socket are commonly connected to the same set of the periphery circuit. The integrated circuit bypass signal difference amplification sampling system and acquisition method can obtain the dynamic high accuracy bypass signal of the integrated circuit chip, can effectively inhibit the interference of the logic noise, gets rid of the dependence on the high accuracy oscilloscope, and improves the collection accuracy and collection efficiency on the integrated circuit.

Owner:PEOPLES LIBERATION ARMY ORDNANCE ENG COLLEGE

A phase synchronization detection method and device based on ipt parallel multi-inverter

ActiveCN112072941BAchieving Phase SynchronizationAc-dc conversionVoltage-current phase angleInverterHemt circuits

The invention provides a phase synchronization detection method and device based on IPT parallel multi-inverter, the device includes n inverter modules, one inverter module is the main inverter module, and the other n-1 inverter modules The inverter module is a slave inverter module; n drive circuits are respectively connected with n external coupled inductors ICT i Parallel connection, 1≤i≤n; each drive circuit includes 4 half-bridge switching arms, 4 half-bridge switching arms are respectively connected with 4 coupling inductors ICT ij Parallel connection, 1≤j≤4; the present invention reflects the synchronous state of the inverter voltage phase according to the error between the inverter output phase and the average value of all output phases, and adjusts the output voltage phase, thereby realizing multiple parallel connections. The function of phase synchronization of inverters and correct measurement of voltage phases of multiple inverters in parallel.

Owner:WUHAN UNIV

A four-phase reflective coherent optical communication system

ActiveCN109981182BAchieving Phase SynchronizationImprove confidentialityElectromagnetic receiversDigital signal processingSignal light

A four-phase reflective coherent optical communication system belongs to the technical field of optical communication systems. The optical communication system includes a laser, a reflective optical modulator, a polarization controller, a 3dB coupler, a polarization beam splitter, a homodyne coherent reception, a digital signal processing module and an adder. The reflective coherent optical communication system provided by the present invention adopts the self-coherent demodulation technology, the signal light and the local oscillator light come from the same light source, and does not need the closed-loop feedback in the traditional coherent optical communication system to realize the wavelength tracking of the local oscillator laser , the receiving part is relatively simple.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method, device and system for suppressing circulation between high-power pwm rectifier power supply modules

ActiveCN105048829BSuppressed circulationBalance loadAc-dc conversion without reversalPhase differenceCarrier signal

The invention relates to a method, a device and a system for inhibiting ring current between large power PWM (Pulse-Width Modulation) rectification power supply modules. The method comprises steps of collecting three phase input current of a first rectification power supply module to obtain ring current between the first rectification power supply module and a second rectification power supply module; obtaining a phase difference of triangular carrier signals of the first rectification power supply module and the second rectification power supply module according to the ring current; calculating a carrier compensation delay time according to the carrier phase difference; and adjusting a phase of the triangular carrier signal of the first rectification power supply module according to the carrier compensation delay time so as to synchronize phases of the triangular carrier signals of the first rectification power supply module and the second rectification power supply module. The invention can effectively inhibit ring current between two rectification power supply modules, balances loads of the two rectification power supply modules, and improves safety and stability of a power distribution network.

Owner:HUNAN UNIV +1