Thin film field effect transistor array substrate, manufacture method and display device thereof

A transistor array and thin film field effect technology, which is applied in semiconductor/solid-state device manufacturing, optics, instruments, etc., can solve problems such as pixel charging difficulties, and achieve the effects of reducing area, reducing lateral electric field, and reducing overlapping area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

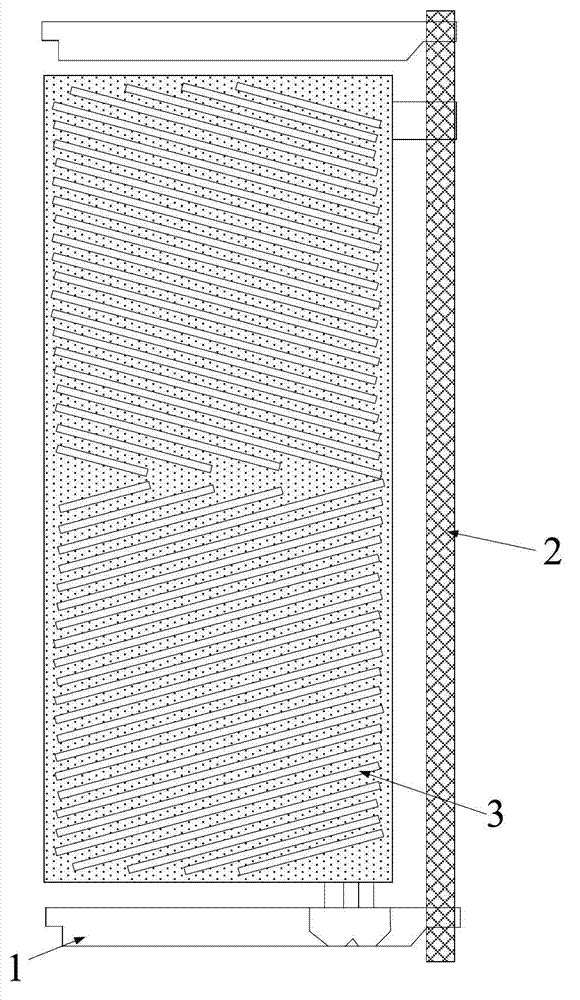

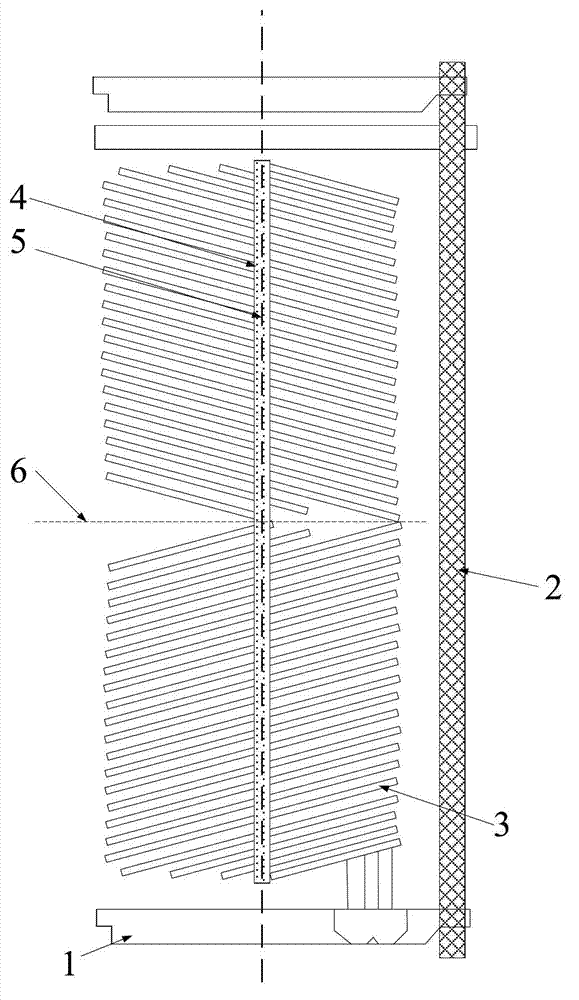

[0034] figure 2 Shown is a schematic structural view of the pixel electrode of the thin film field effect transistor array substrate of this embodiment, as figure 2 As shown, the thin film field effect transistor array substrate of this embodiment includes a plurality of gate lines and data lines, the gate lines and data lines are arranged perpendicular to each other; the sub-pixel area defined by the crossing of the gate lines and data lines; and A plurality of strip-shaped pixel electrodes formed in the sub-pixel area, wherein the thin film field effect transistor array substrate further includes: each strip-shaped pixel electrode arranged in the middle of each sub-pixel area, parallel to the data line 2 and connected to the sub-pixel area 3 are connected to a pixel electrode connection line 4.

[0035] Wherein, the sub-pixel area has a center line 5 parallel to the data line 2 (ie, the first center line) and a center line 6 parallel to the gate line 1 (ie, the second cen...

Embodiment 2

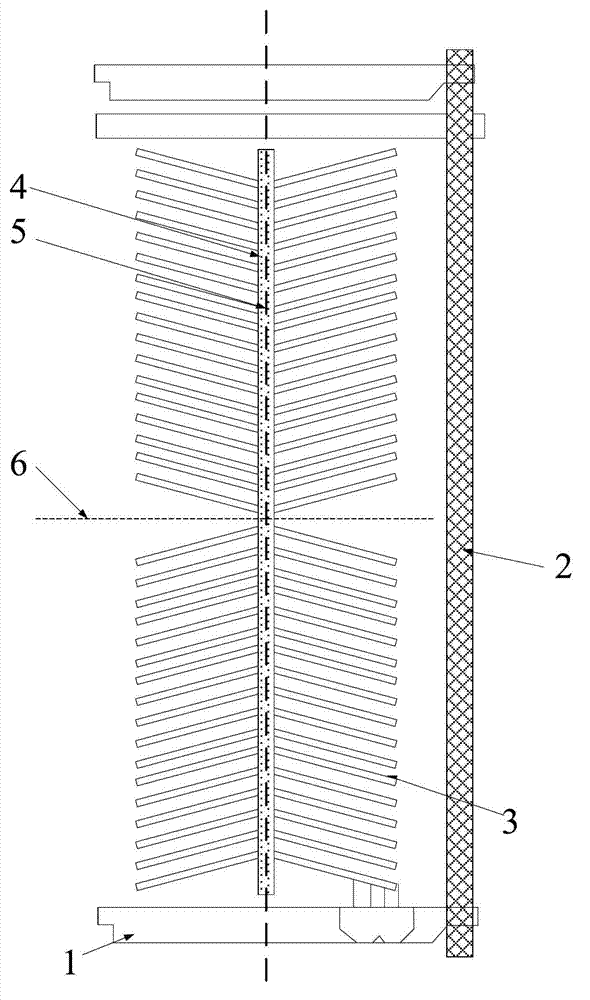

[0039] image 3 Shown is a schematic structural view of the pixel electrode of the thin film field effect transistor array substrate of this embodiment, as image 3 As shown, the thin film field effect transistor array substrate of this embodiment includes a plurality of gate lines and data lines, the gate lines and data lines are arranged perpendicular to each other; the sub-pixel area defined by the crossing of the gate lines and data lines; and A plurality of strip-shaped pixel electrodes formed in the sub-pixel area, wherein the thin film field effect transistor array substrate further includes: each strip-shaped pixel electrode arranged in the middle of each sub-pixel area, parallel to the data line 2 and connected to the sub-pixel area 3 are connected to a pixel electrode connection line 4.

[0040] Among them, the sub-pixel area has a center line 5 parallel to the data line 2 (ie, the first center line) and a center line 6 parallel to the gate line 1 (ie, the second cent...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More