Patents

Literature

38results about How to "Reduce storage capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

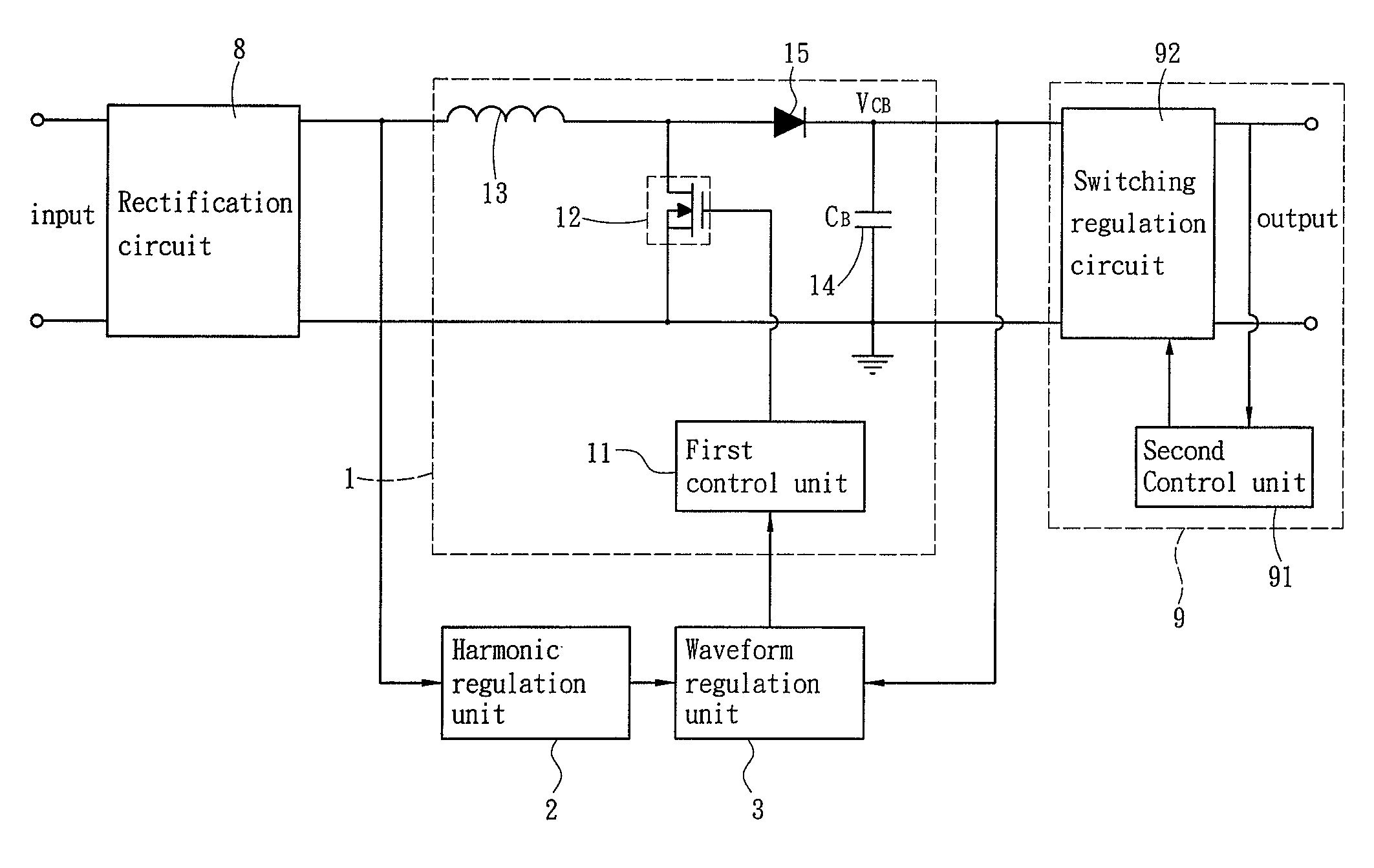

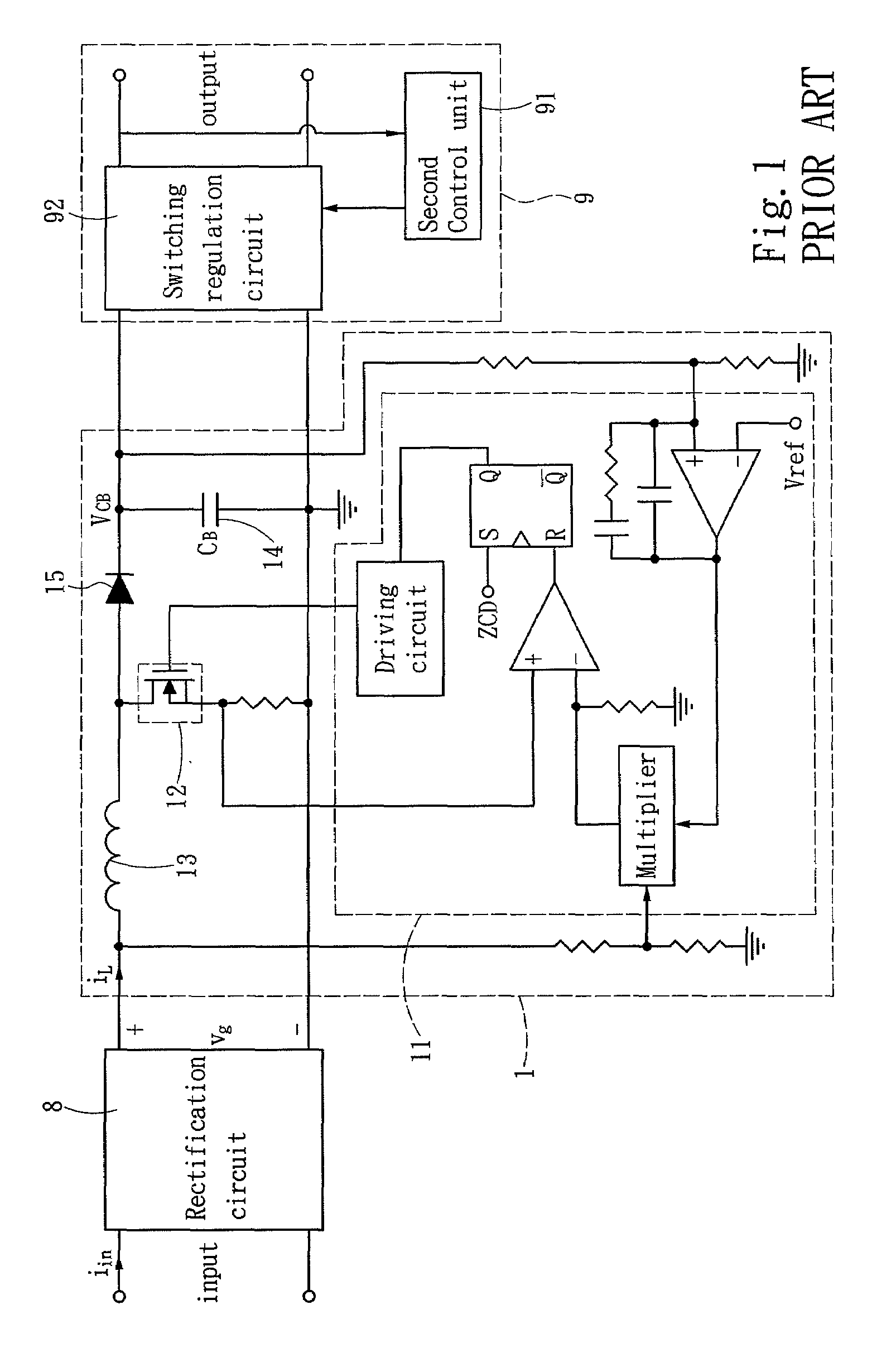

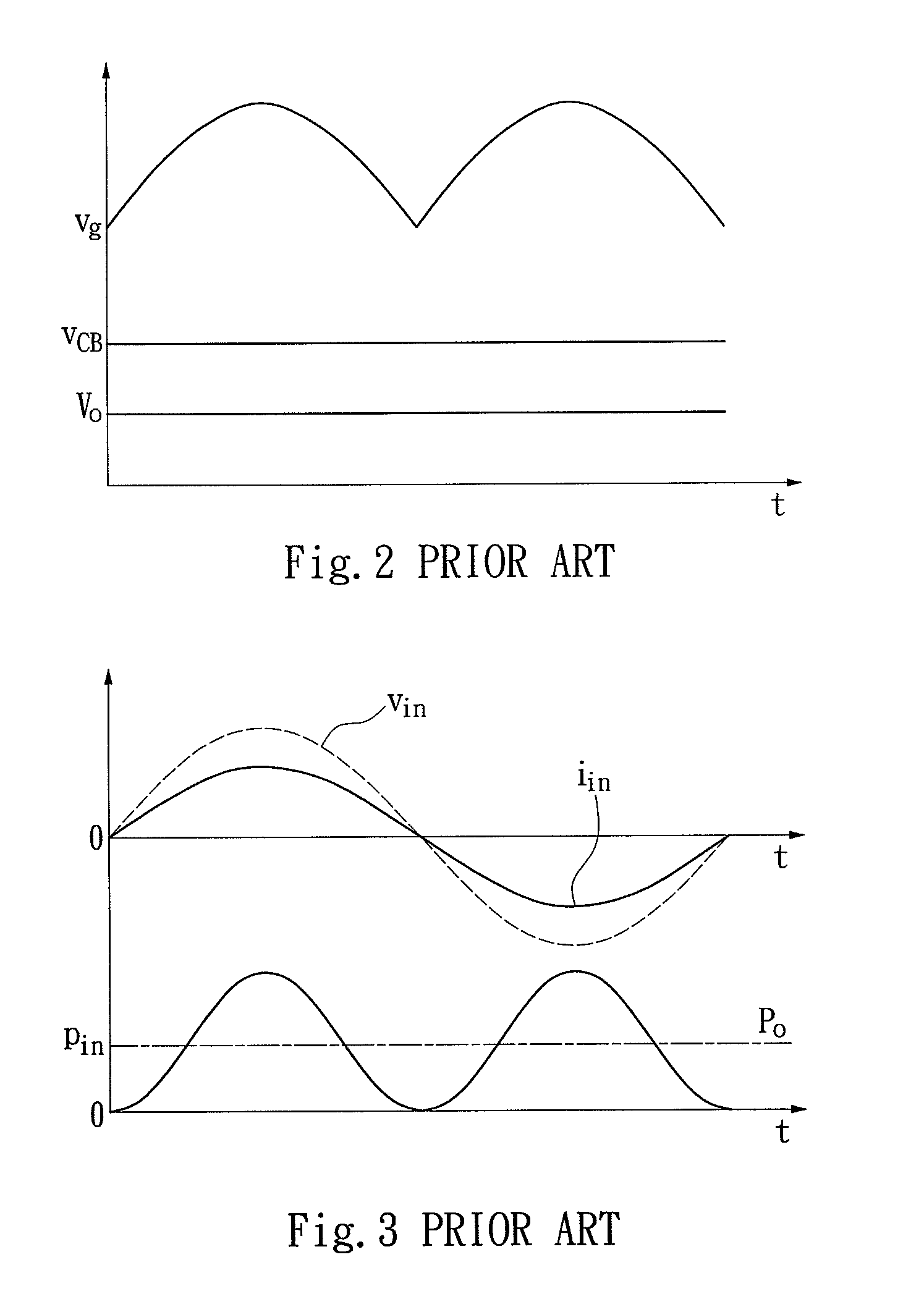

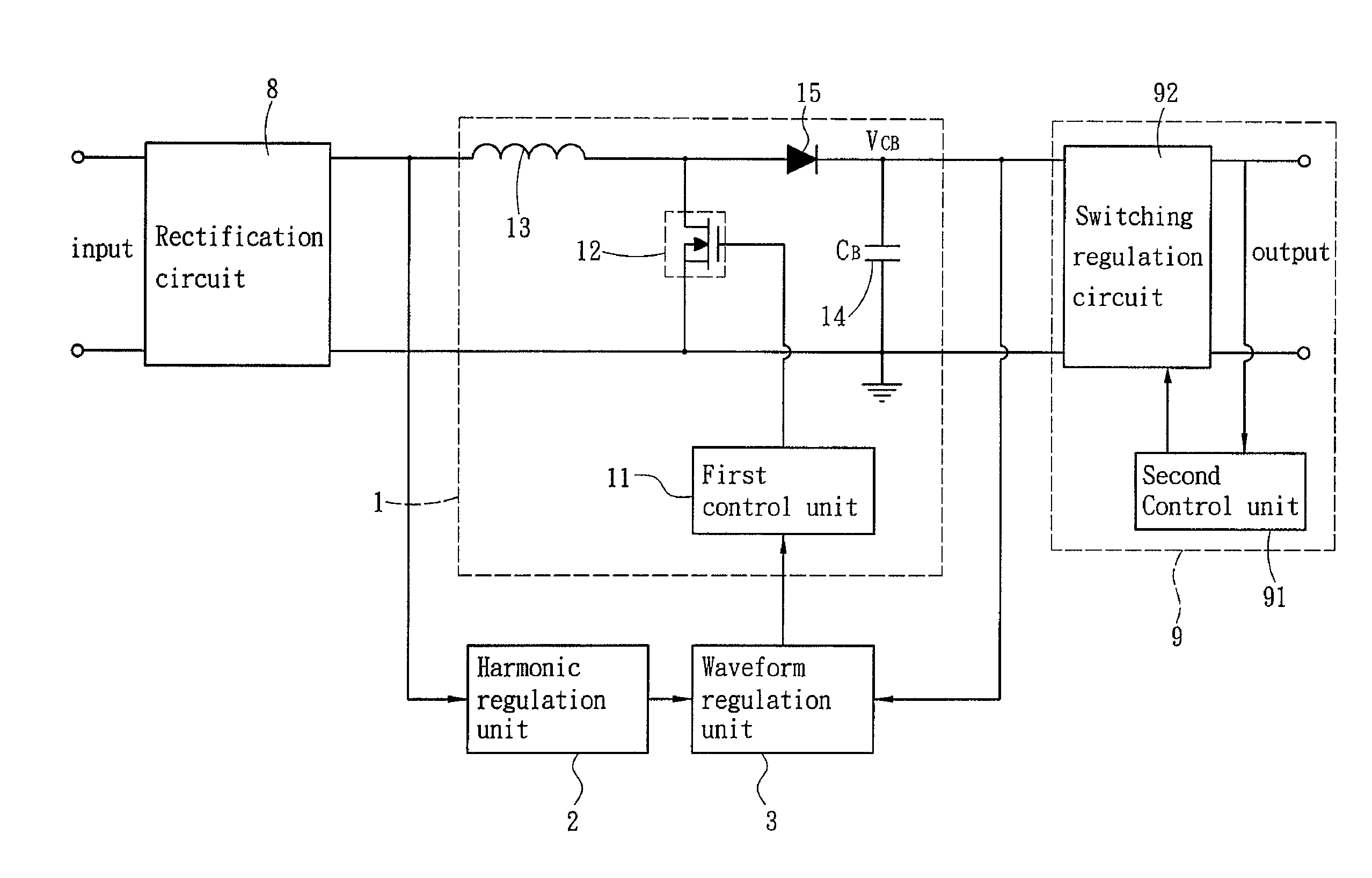

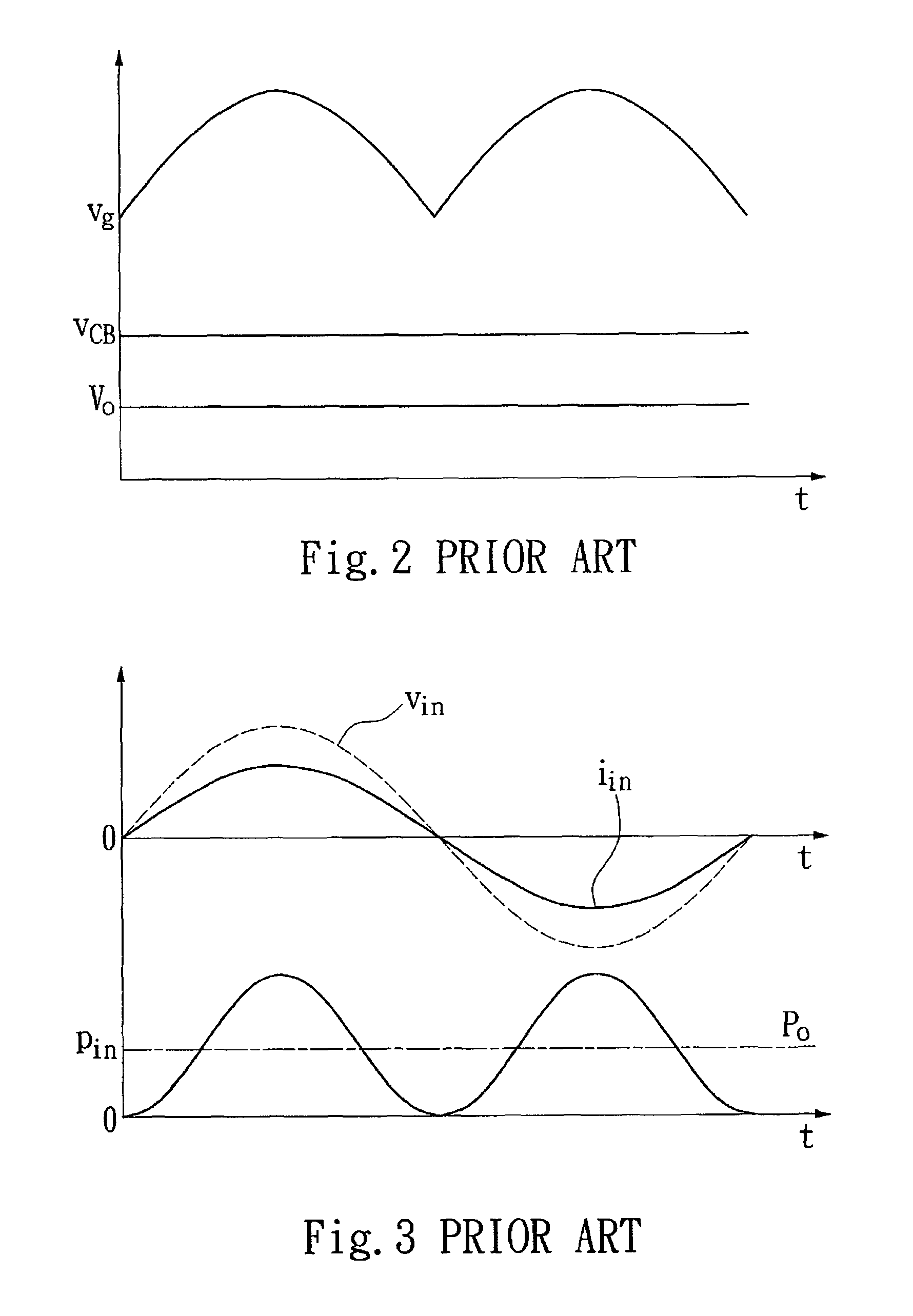

Means of eliminating electrolytic capacitor as the energy storage component in the single phase ad/dc two-stage converter

ActiveUS20100014326A1Extended service lifeReduce volatilityEfficient power electronics conversionEnergy industryCapacitanceEngineering

A power factor correction (PFC) circuit includes an inductor, a diode, a storage capacitor, a switch and a control unit. The input power has a voltage fluctuation V1. The storage component absorbs a first voltage fluctuation and a switch regulation circuit absorbs a second voltage fluctuation V2. Thus output voltage from the PFC circuit is not a conventional constant voltage but a voltage of a great ripple. The PFC circuit further has a harmonic regulation unit. The harmonic regulation unit generates a voltage signal containing 3rd harmonic. The control unit receives a feedback signal and the voltage signal containing 3rd harmonic to generate a reference to the inductor current. Therefore, the inductor current contains 3rd harmonic. Thus power fluctuation absorbed and released by the capacitor is smaller. As a result energy storage capacitance can be reduced significantly.

Owner:SPI ELECTRONICS +1

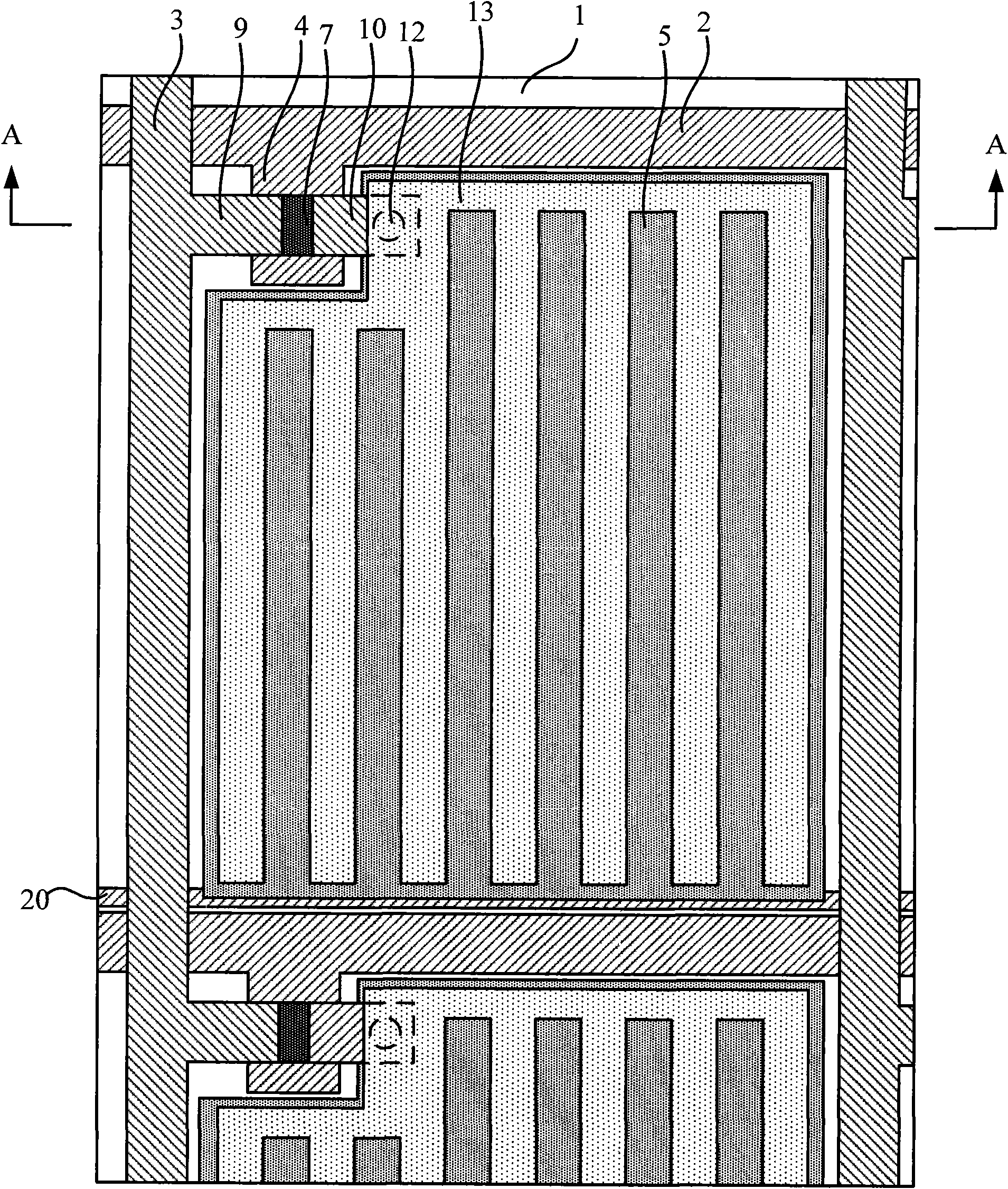

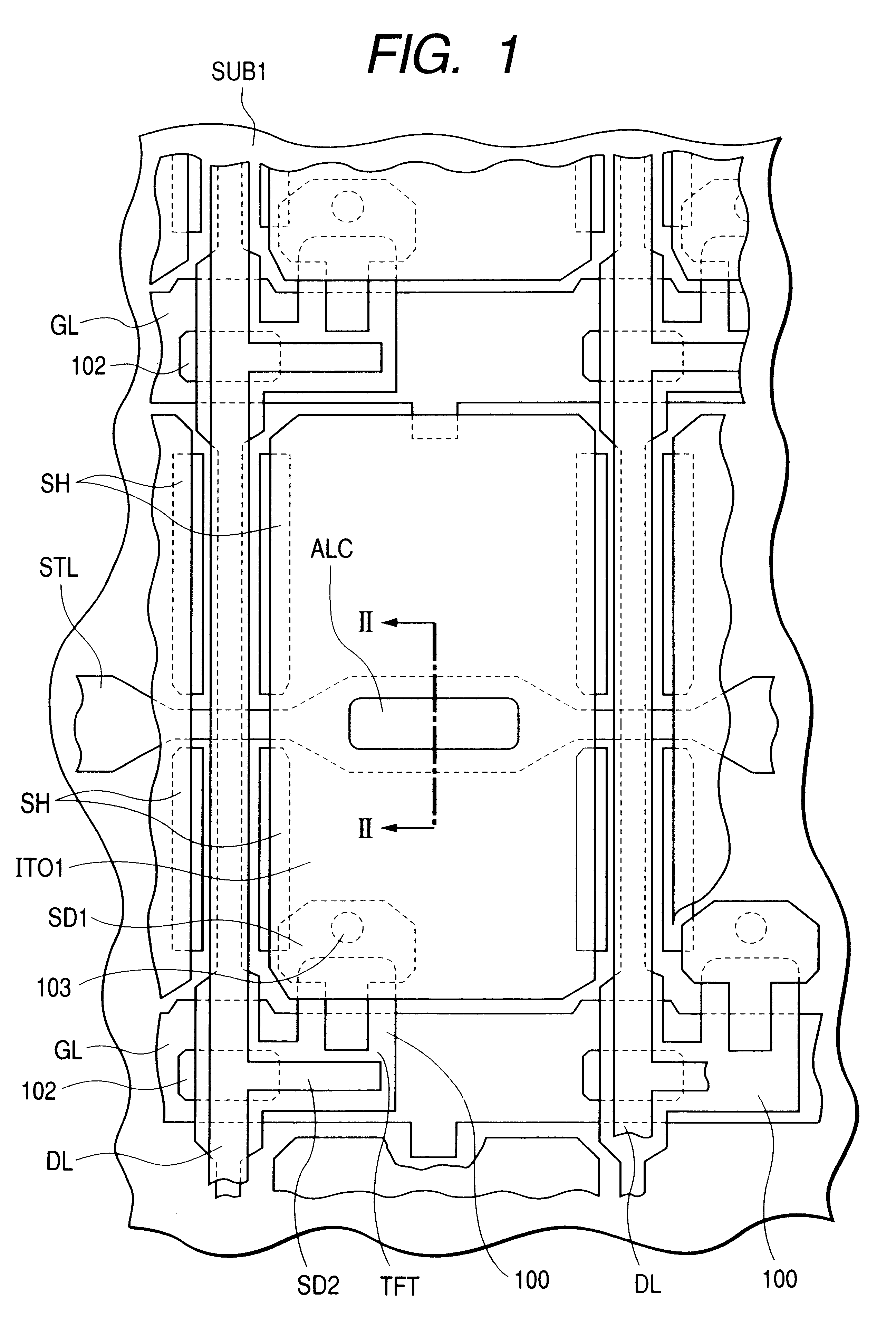

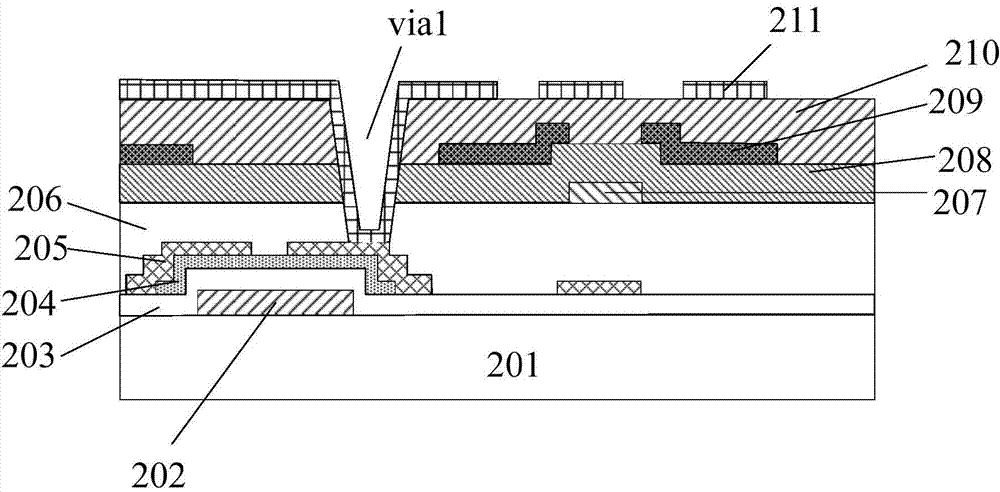

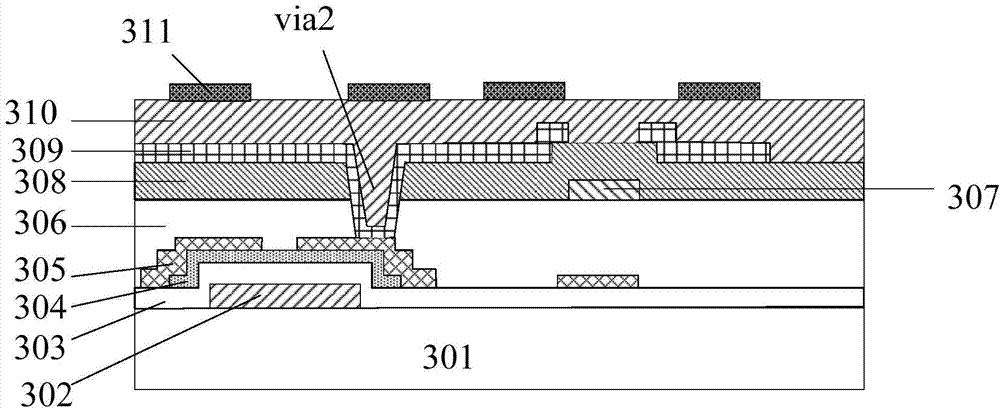

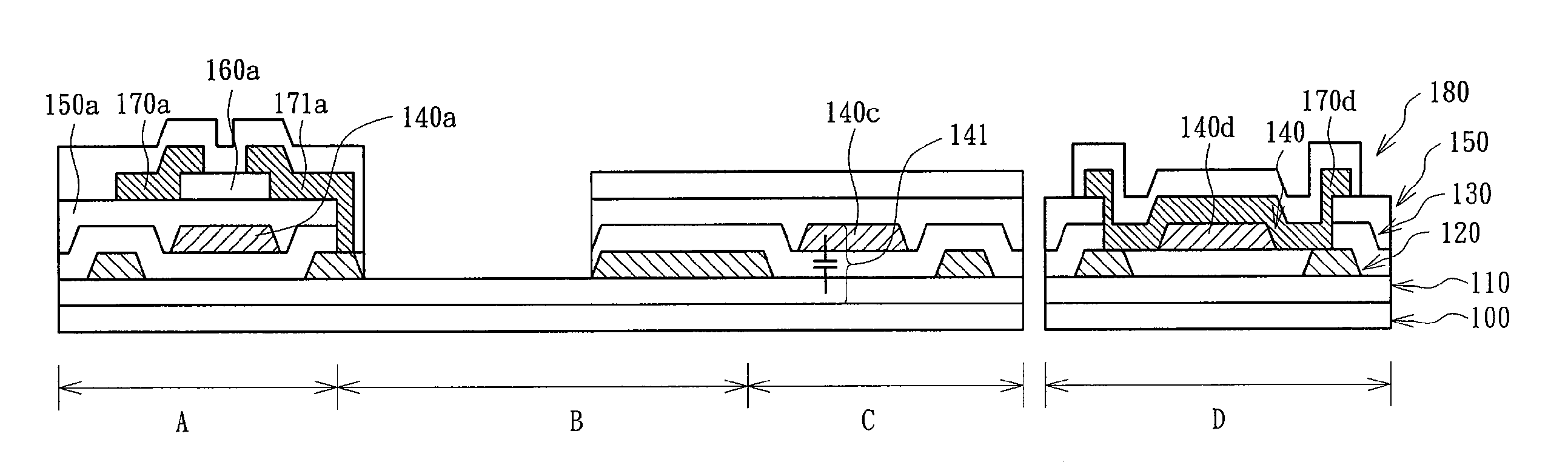

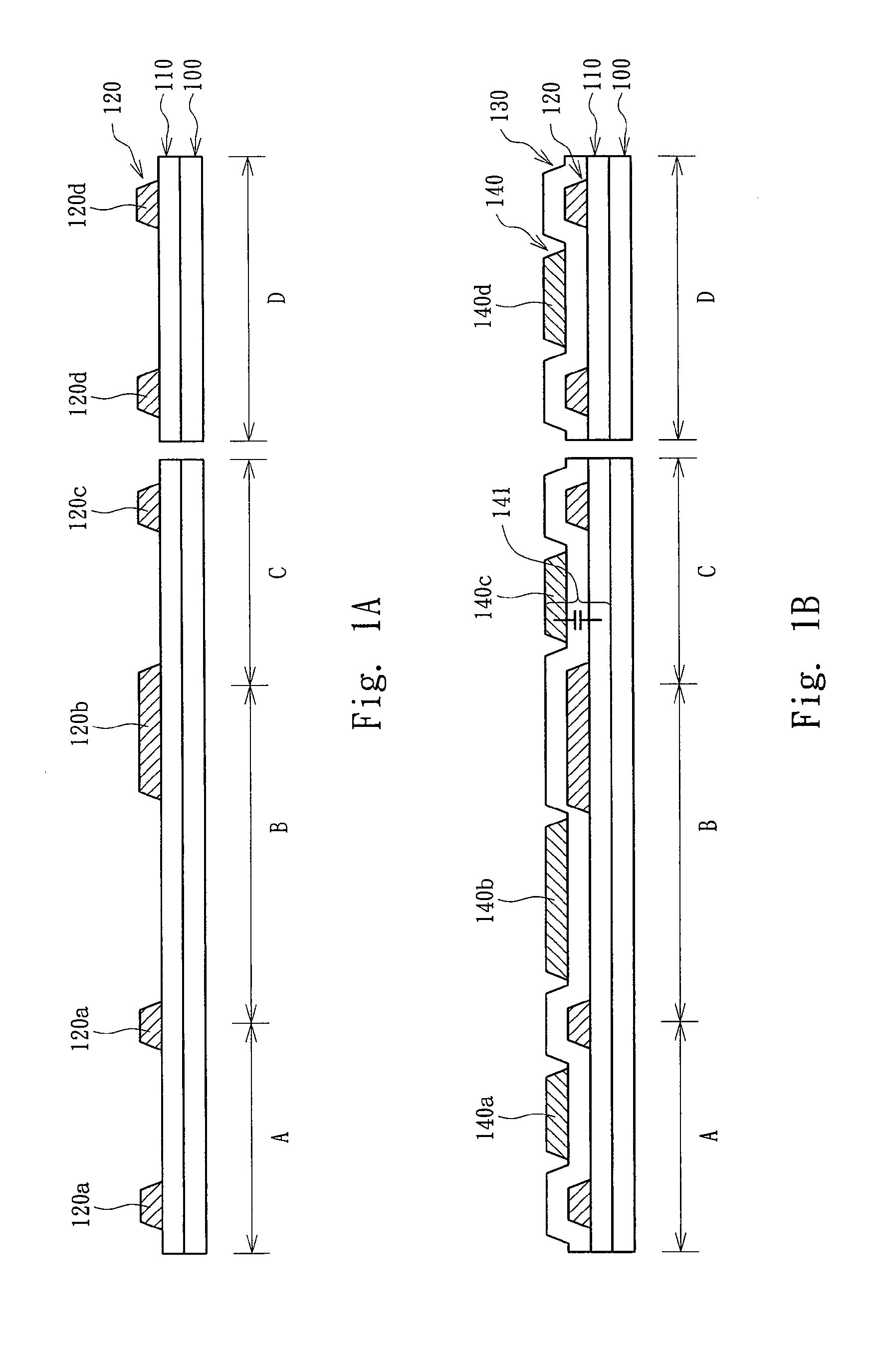

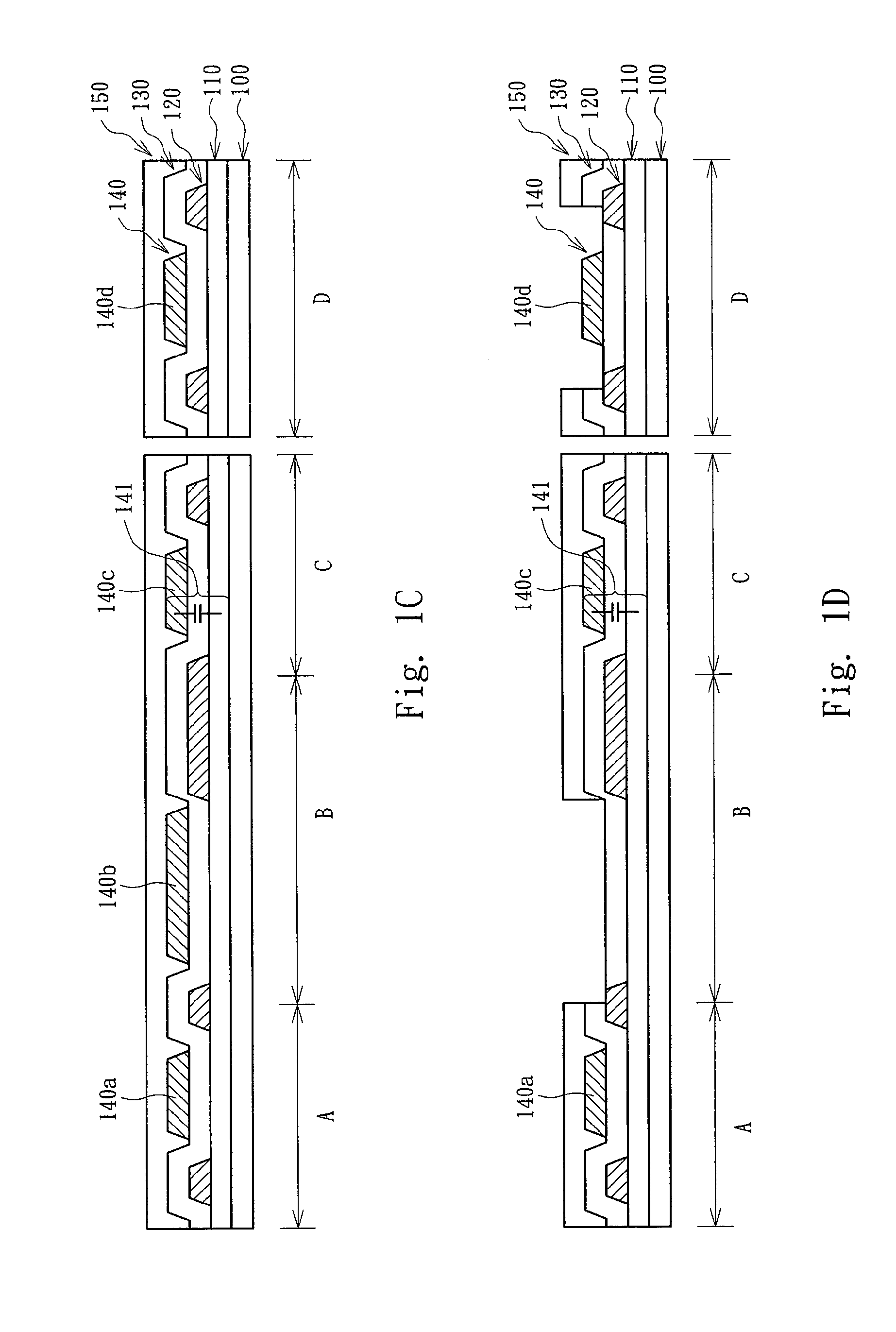

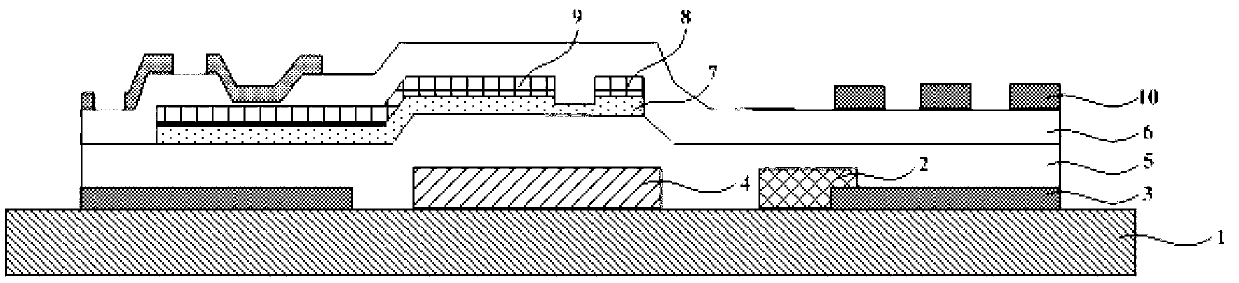

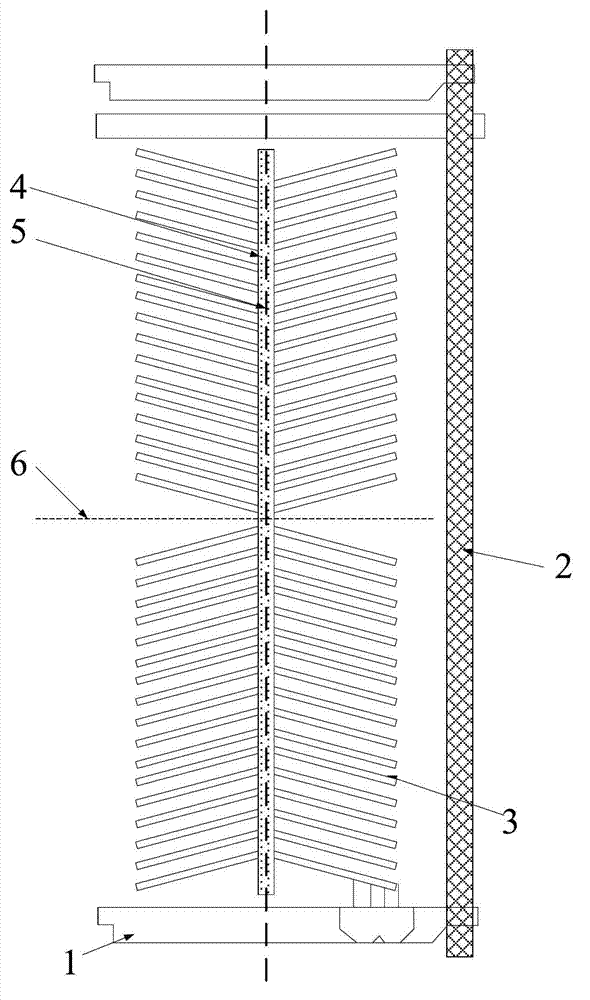

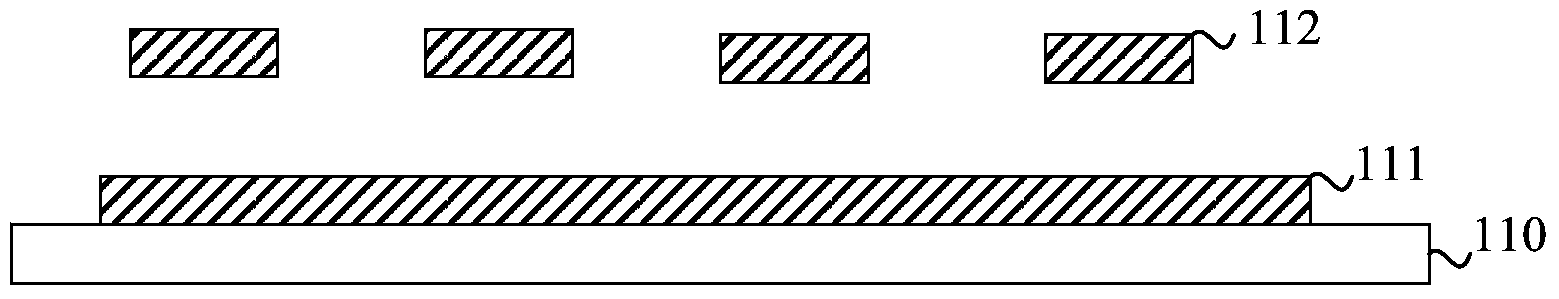

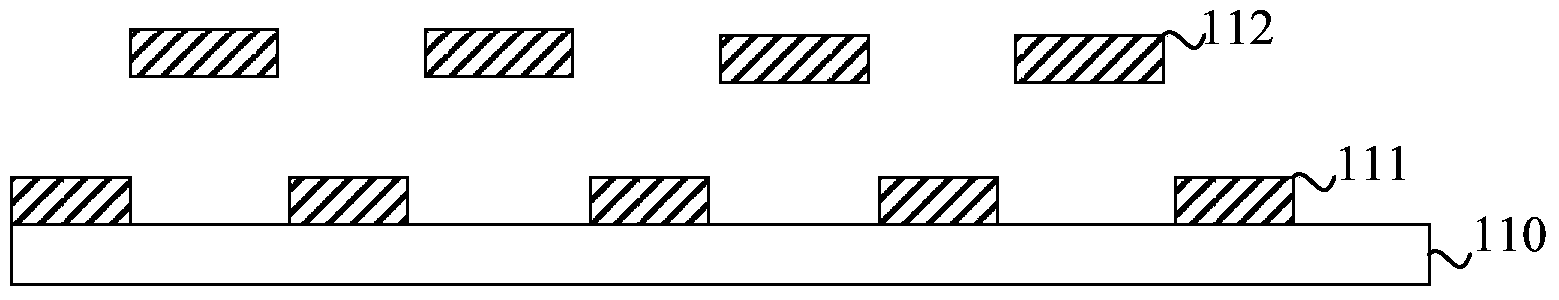

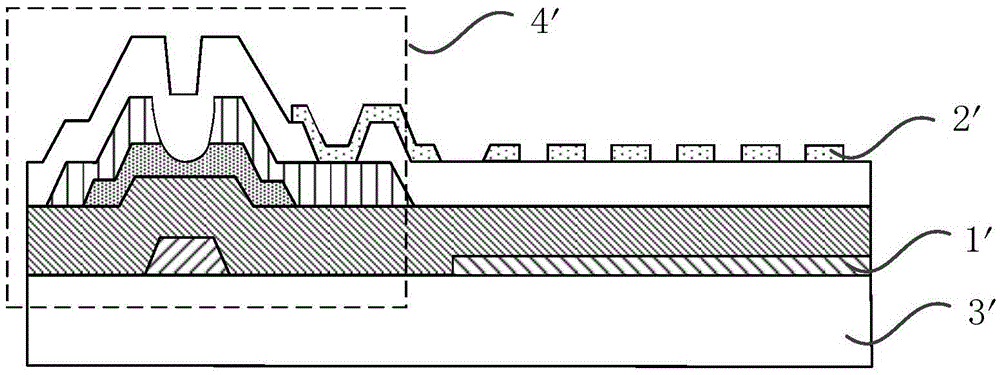

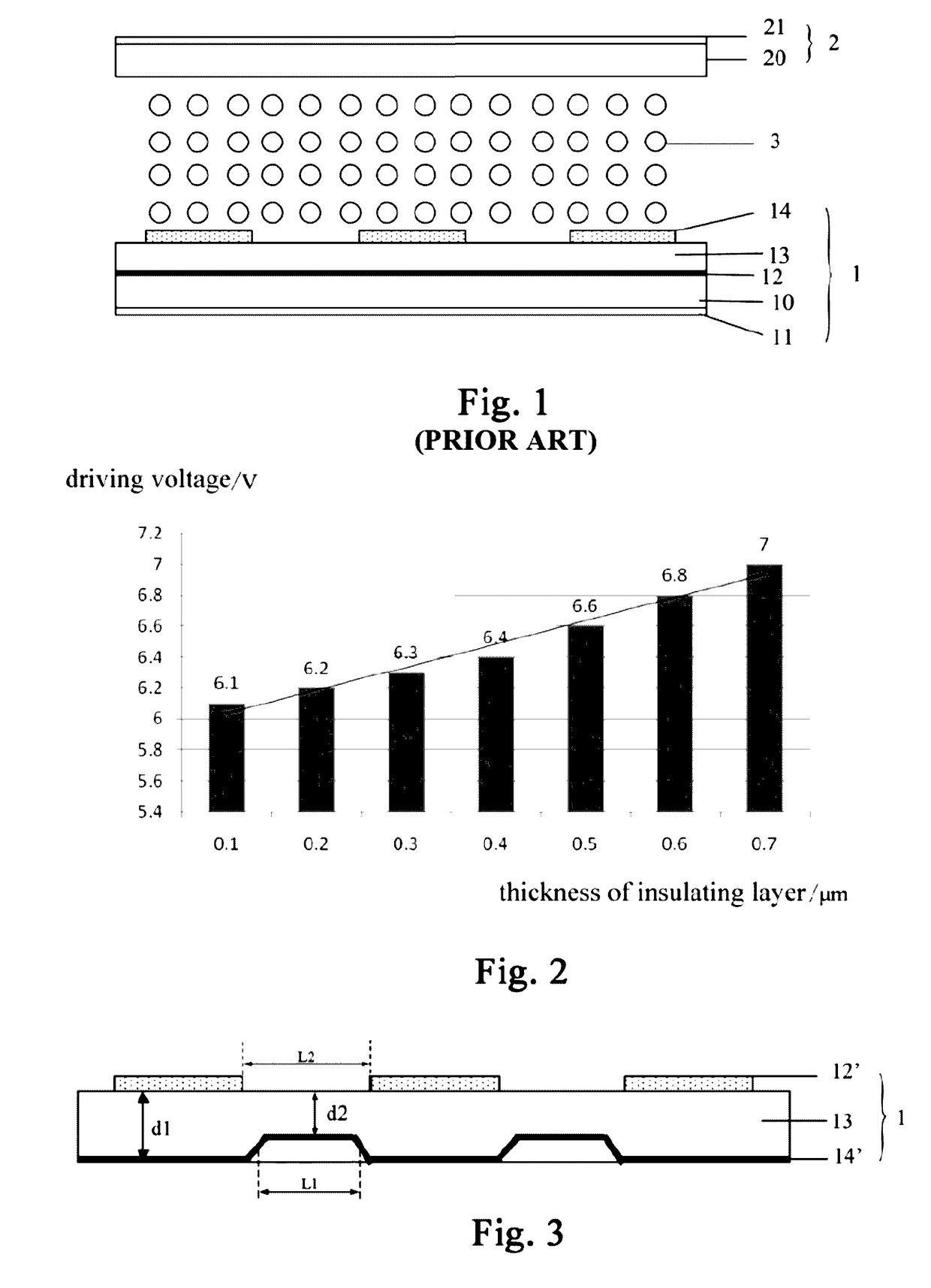

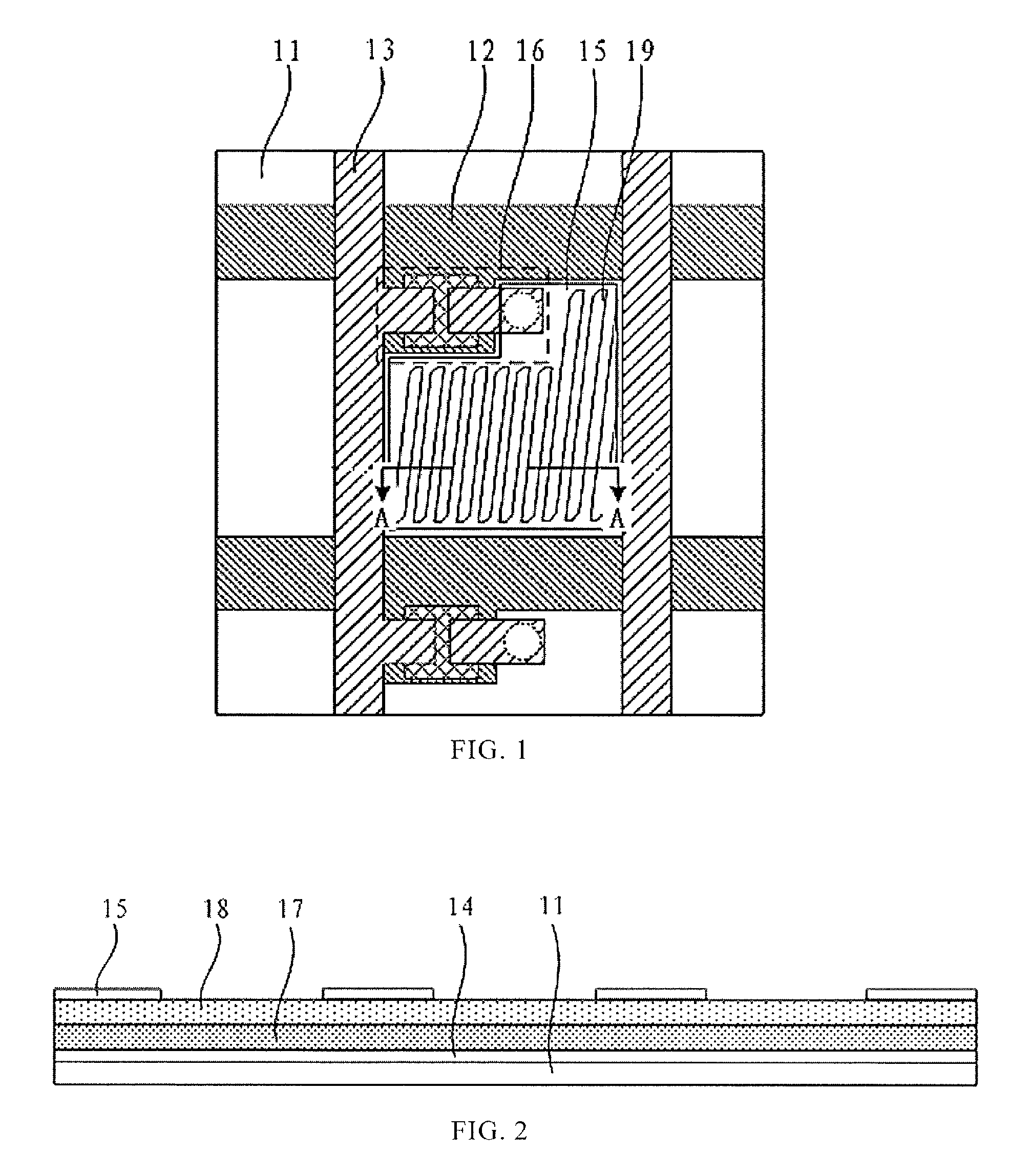

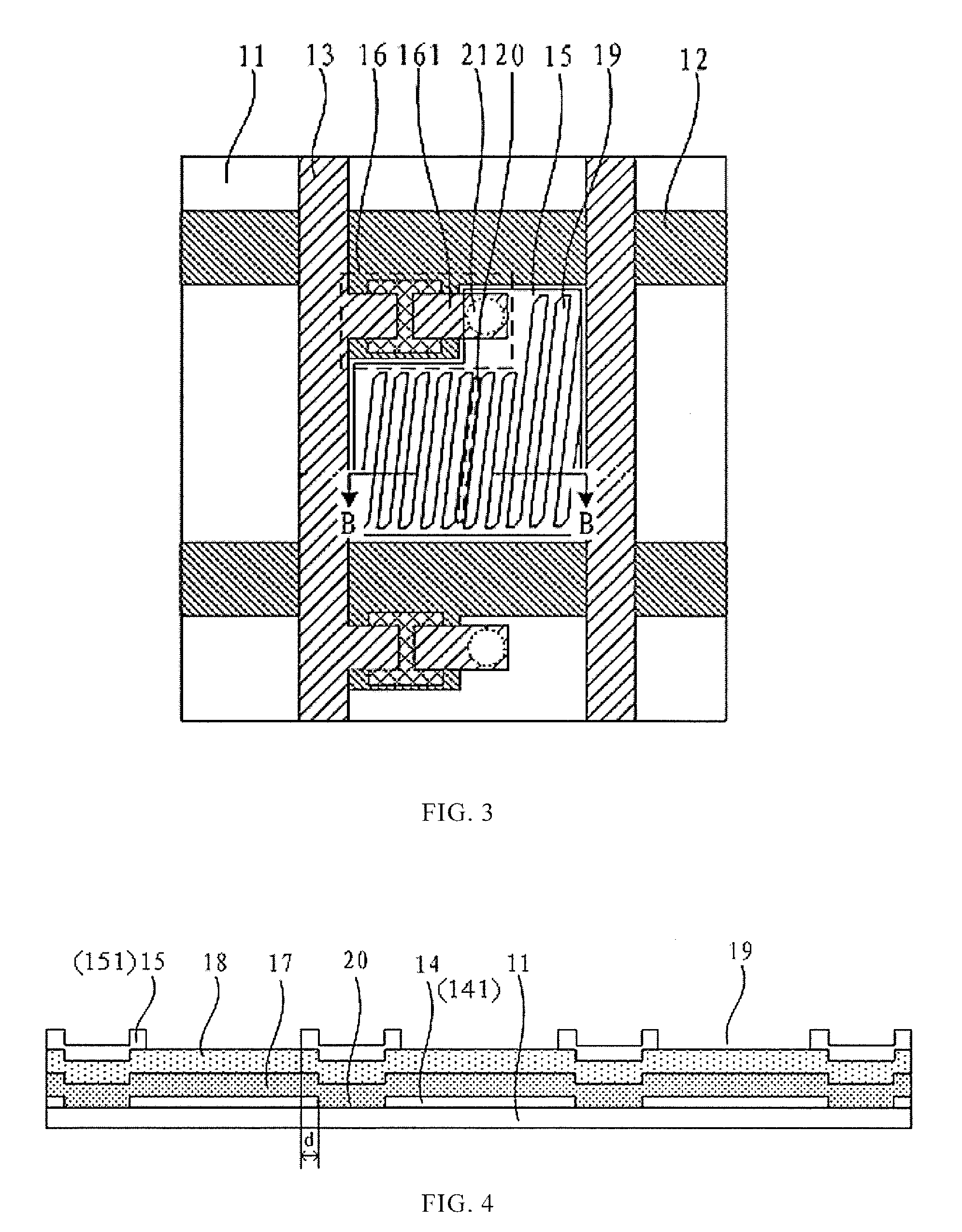

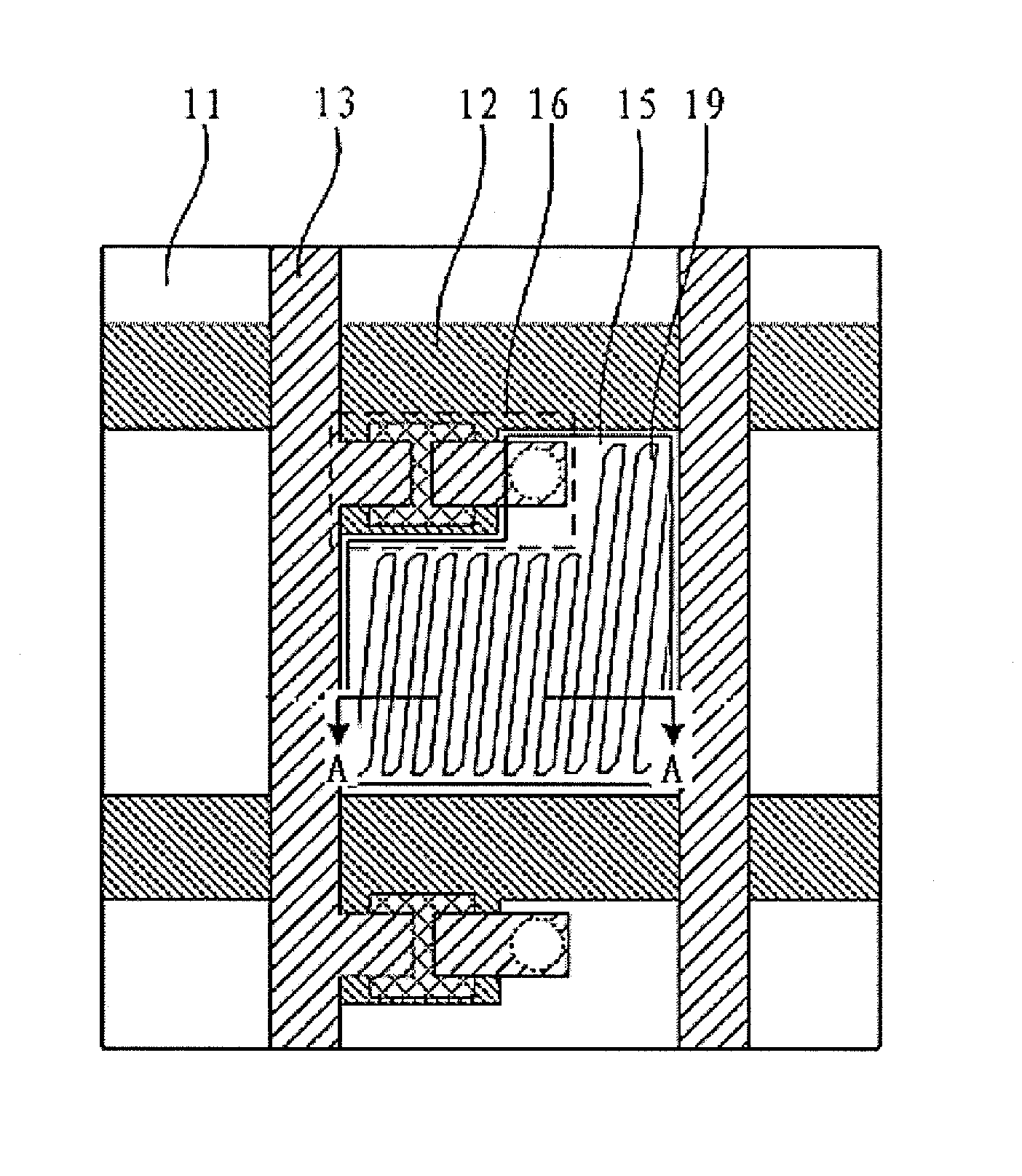

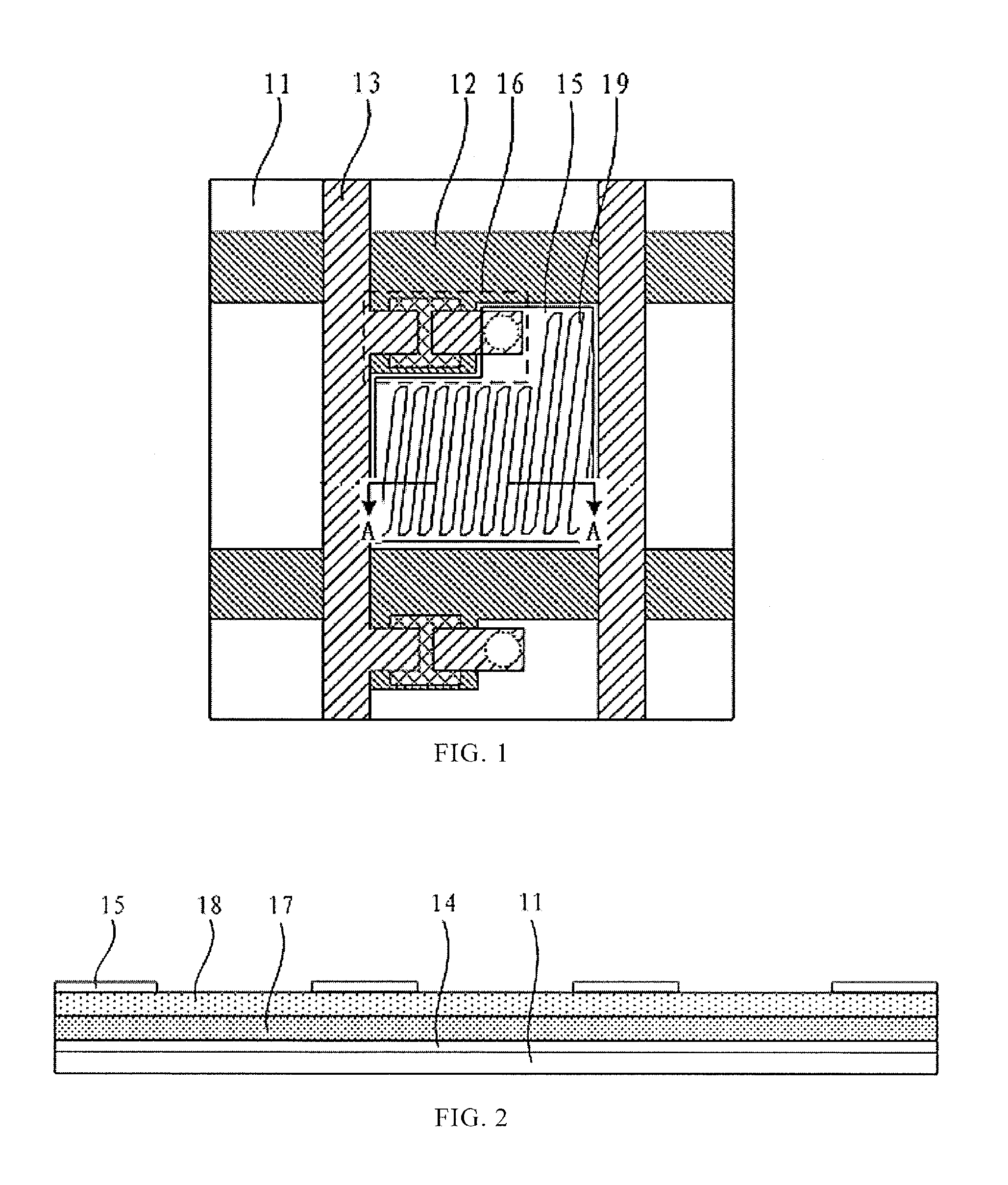

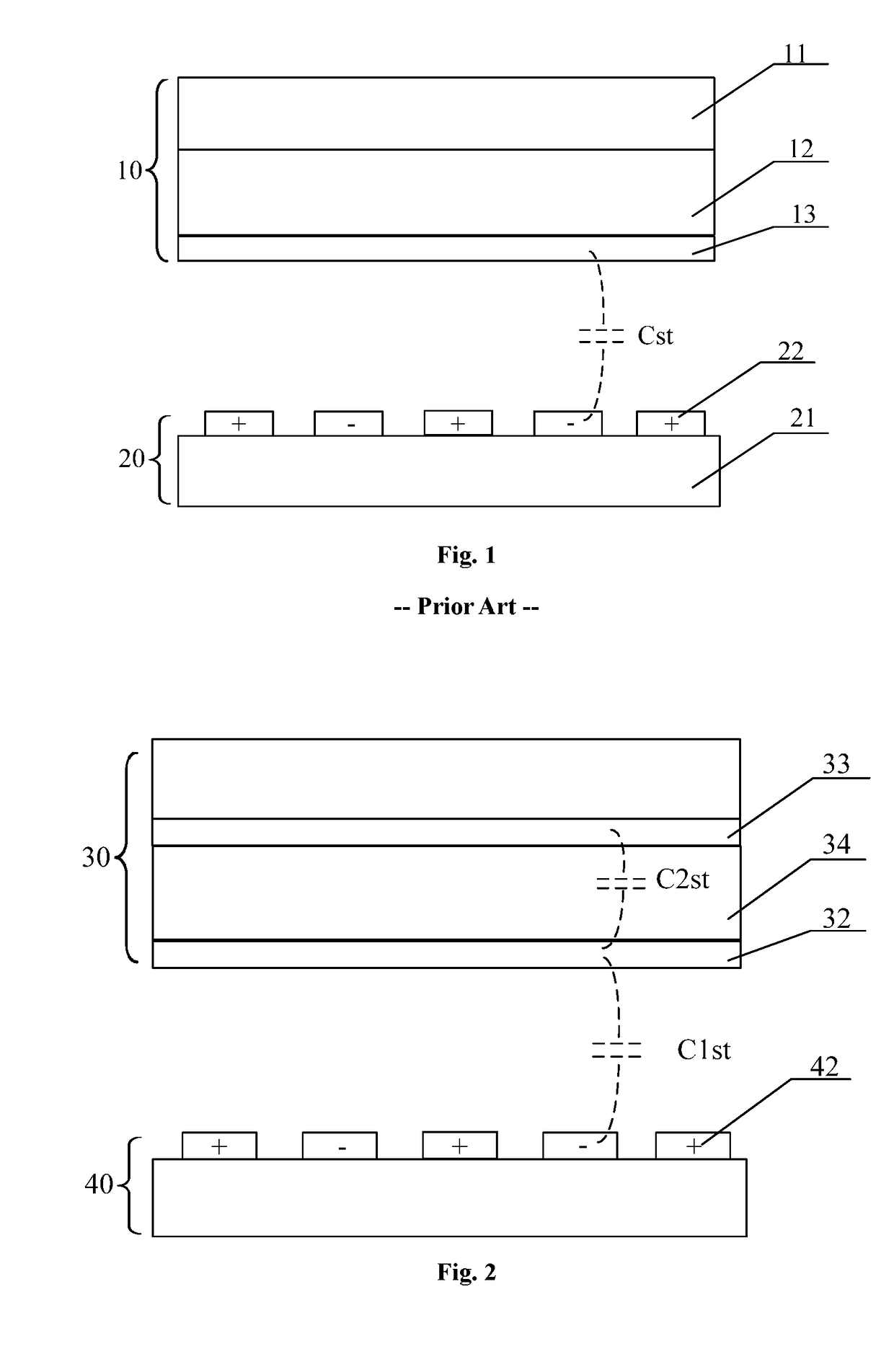

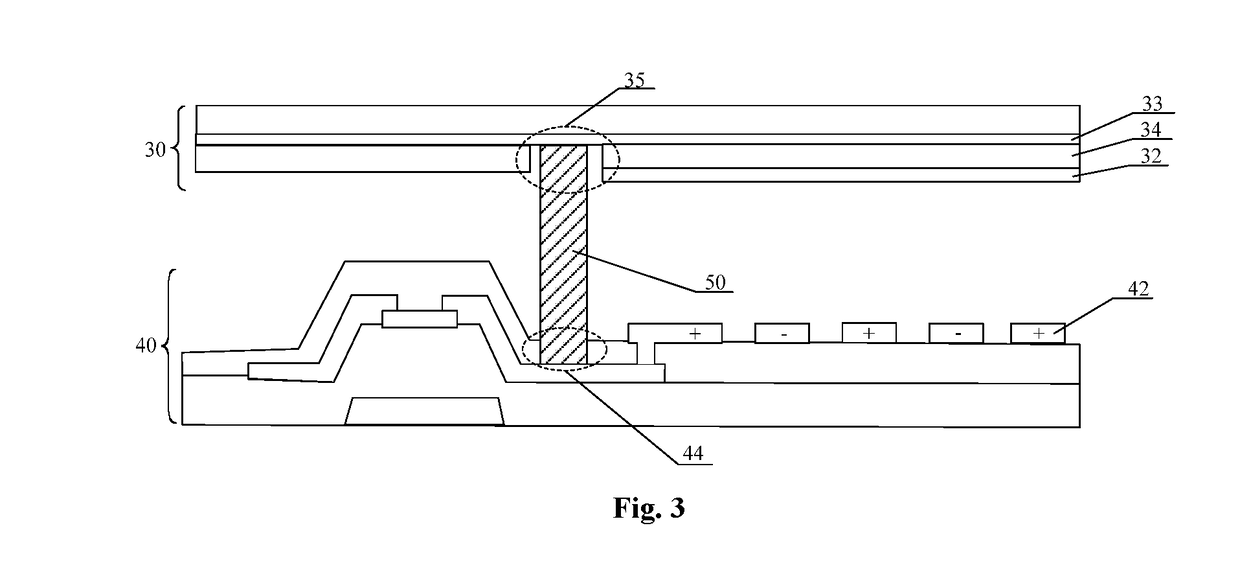

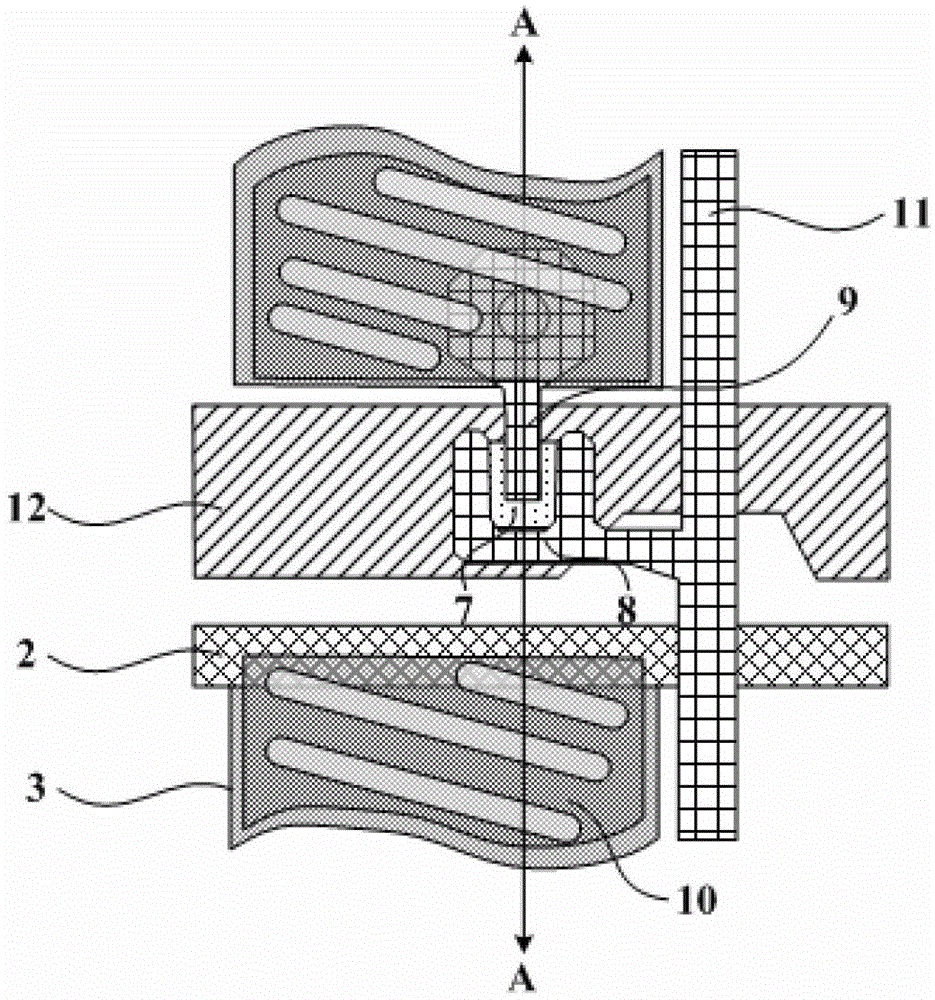

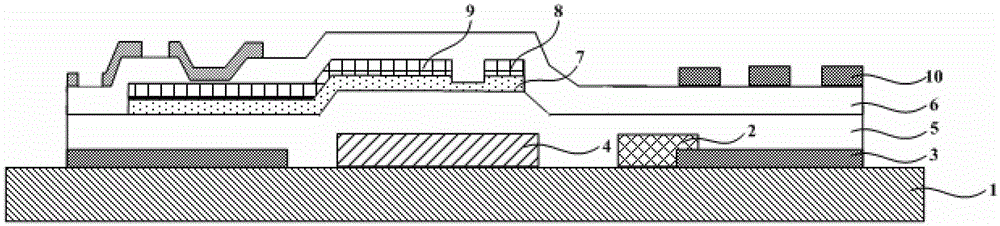

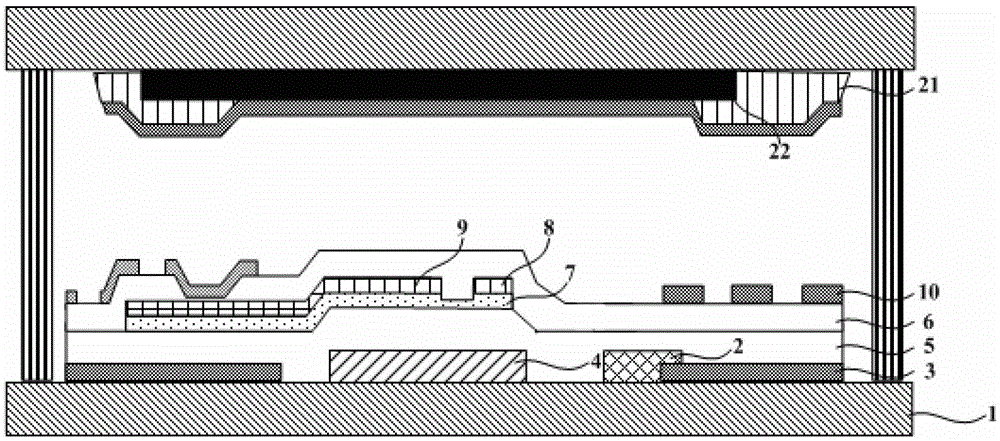

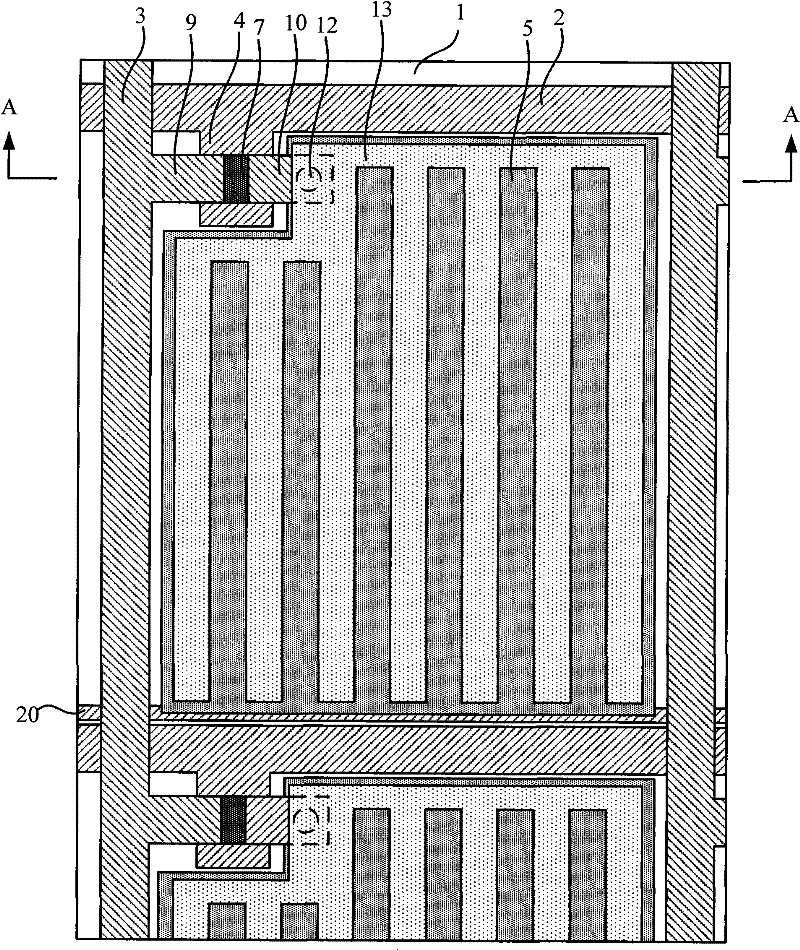

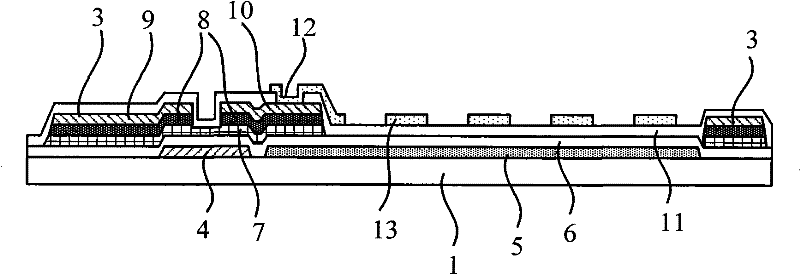

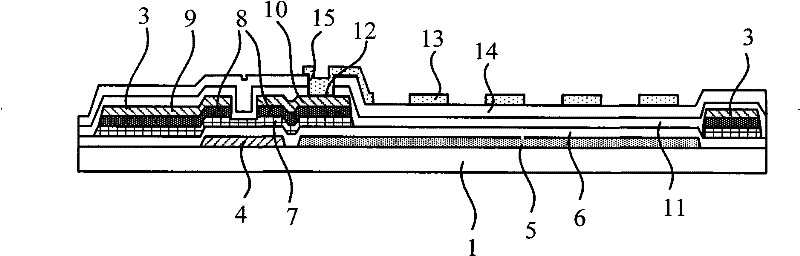

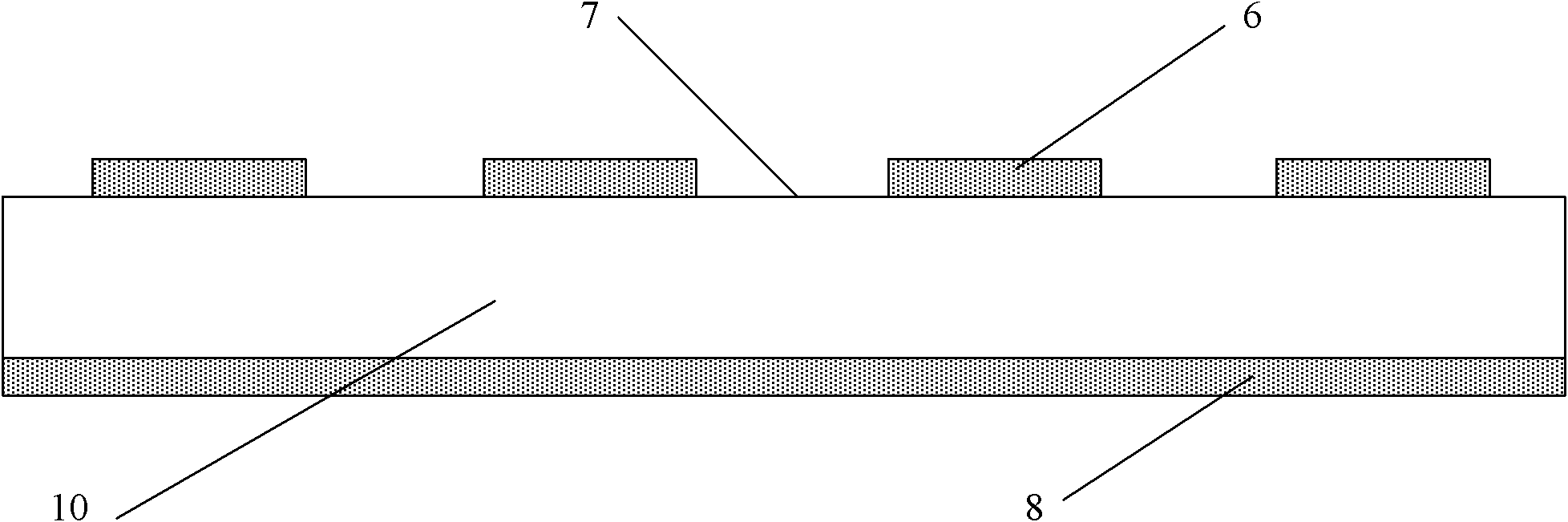

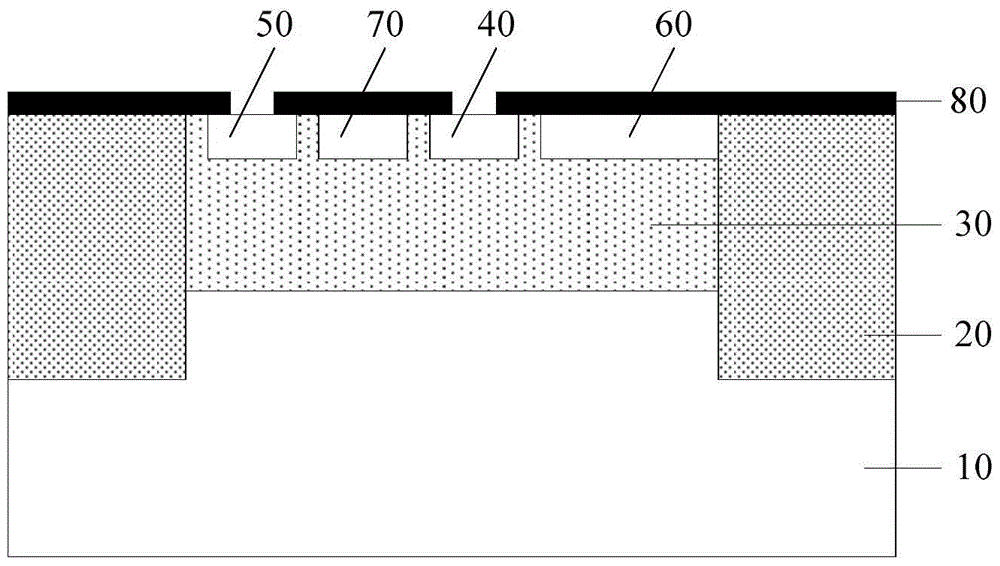

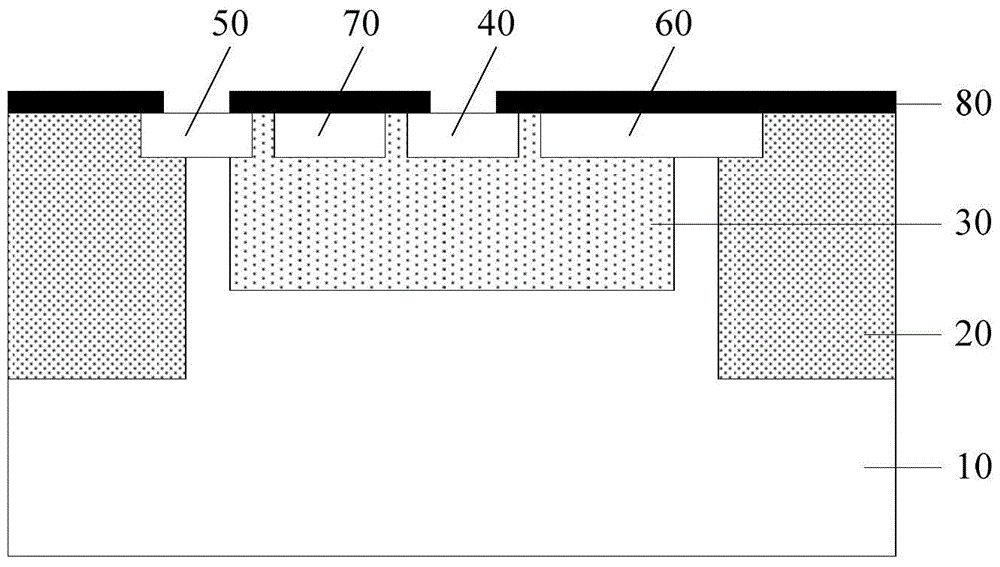

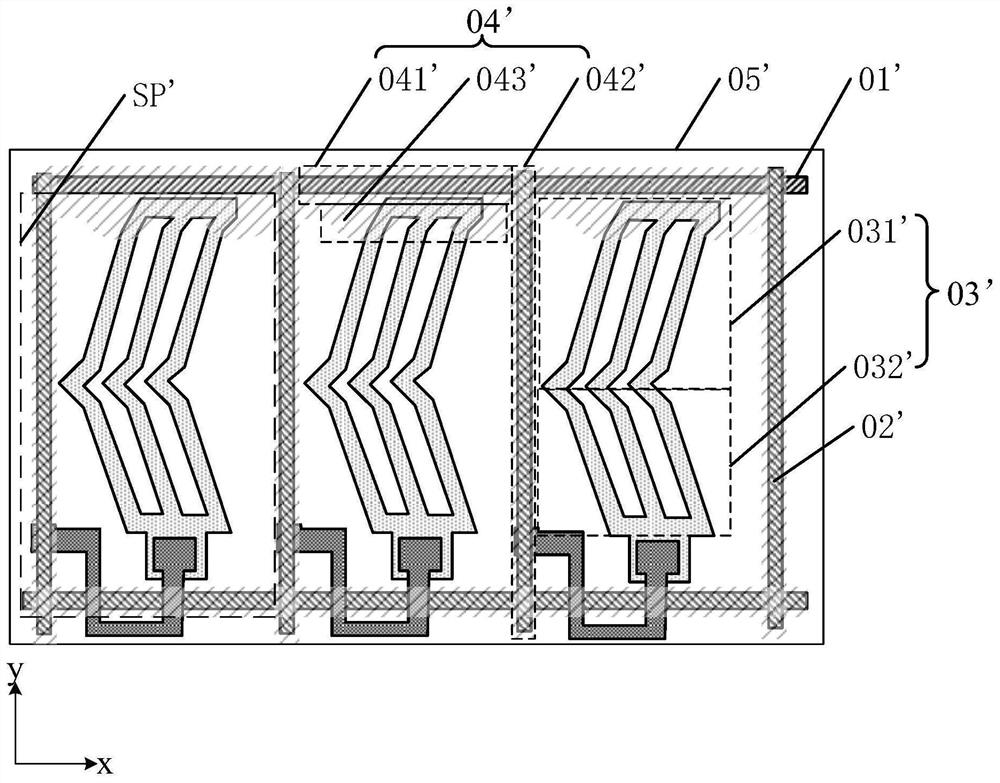

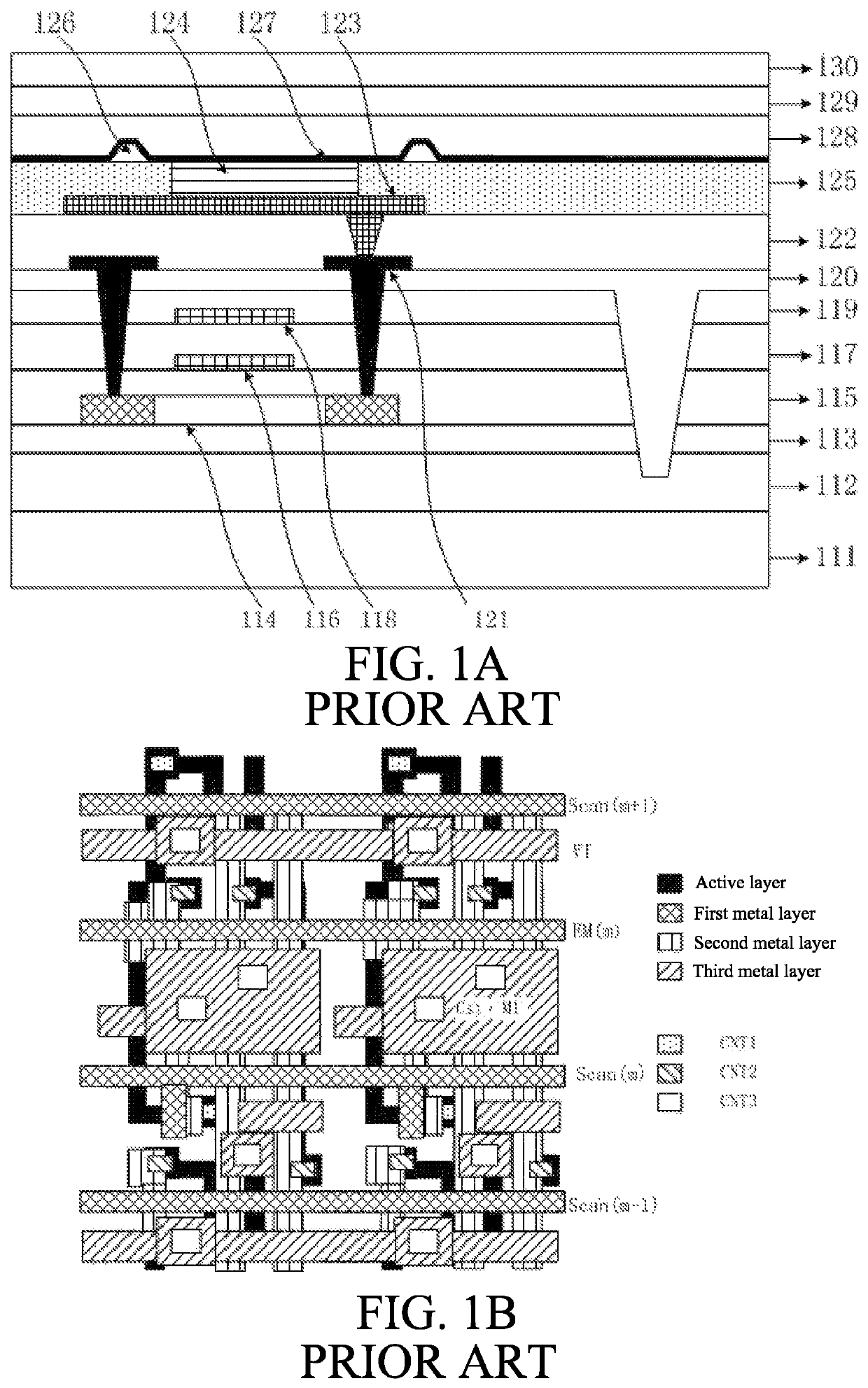

Array substrate, manufacturing method thereof and wide-viewing angle liquid crystal display

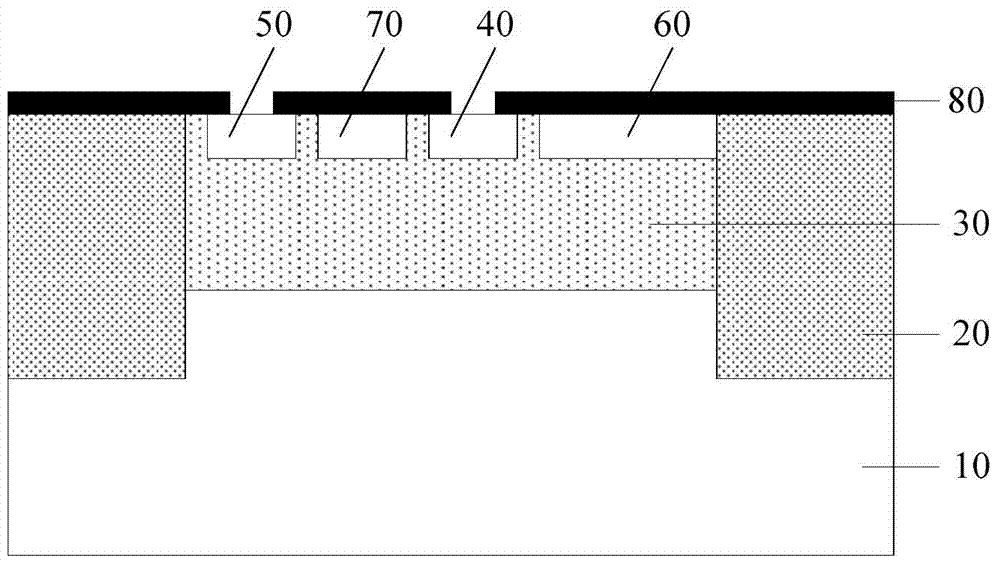

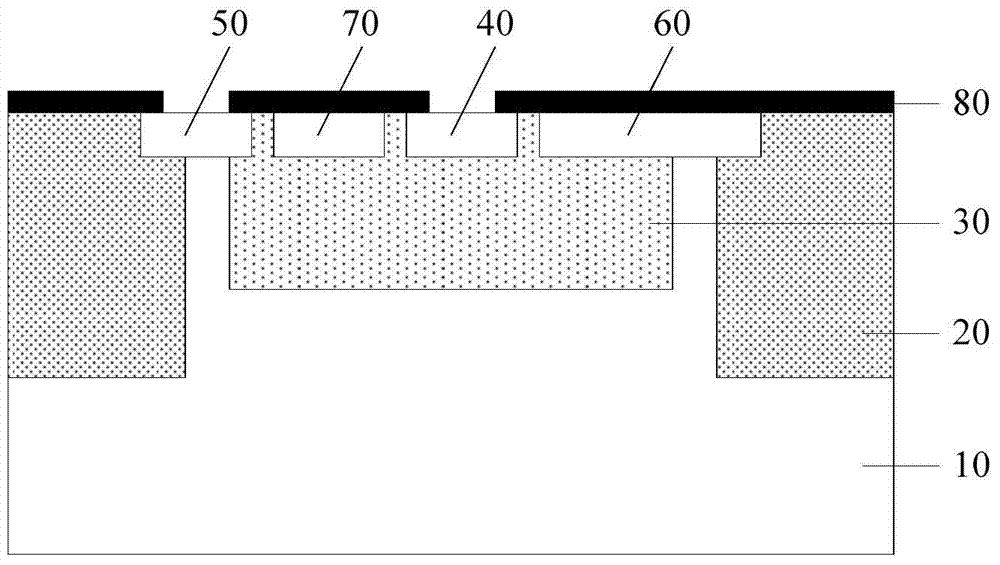

ActiveCN101847641AIncreasing the thicknessReduce storage capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceLiquid-crystal display

The invention relates to an array substrate, a manufacturing method thereof and a wide-viewing angle liquid crystal display. The array substrate comprises a substrate, a plurality of pixel areas and an organic transparent insulating layer, wherein the organic transparent insulating layer is formed between a passivation layer and a pixel electrode. The manufacturing method comprises the following steps of: forming a public electrode, a public electrode wire and patterns of a thin film transistor switch on the substrate; depositing the passivation layer; forming the organic transparent insulating layer, an organic layer via hole and a passivation layer via hole on the passivation layer; and forming patterns of the pixel electrode on the organic transparent insulating layer, wherein a plurality of gaps are formed on the patterns of the pixel electrode, and the pixel electrode is connected with the thin film transistor switch through the organic layer via hole and the passivation layer via hole. A liquid crystal display of the invention comprises the array substrate. In the array substrate, the technical means of adding the organic transparent insulating layer between the pixel electrode and the passivation layer is adopted to increase the thickness of film layers between the pixel electrode and the public electrode, so that the storage capacitance and residual images can be reduced effectively.

Owner:BOE TECH GRP CO LTD

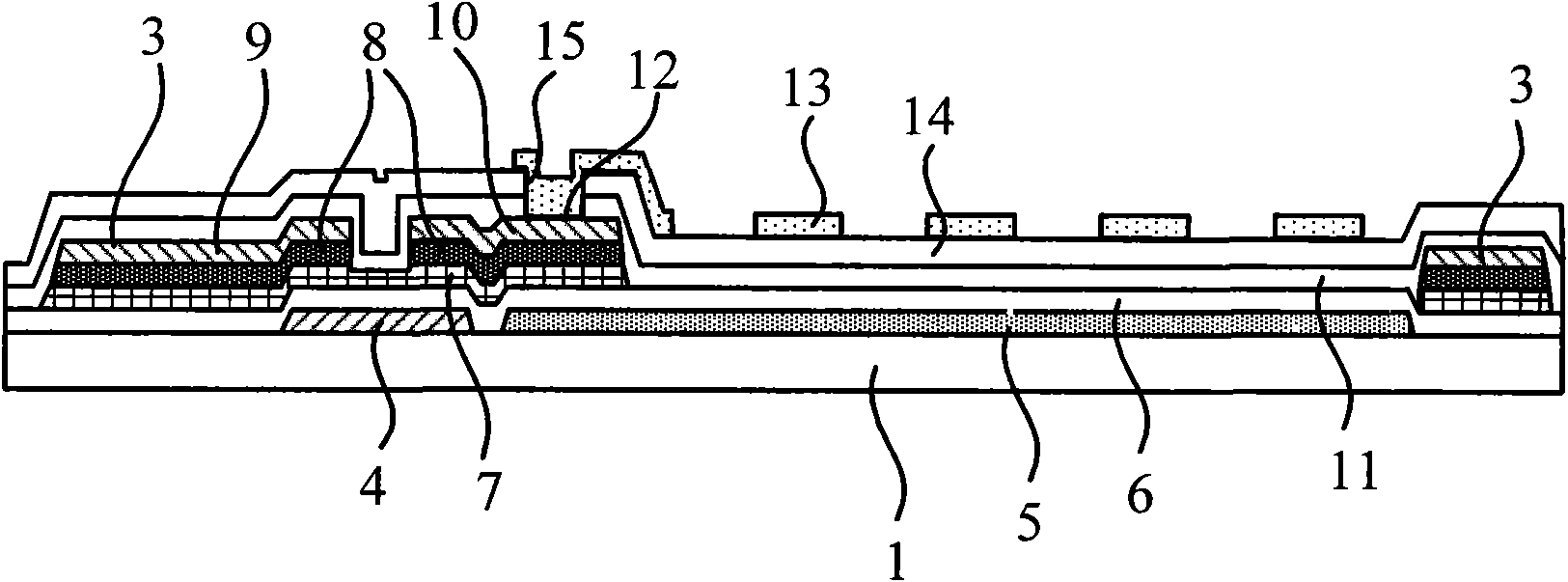

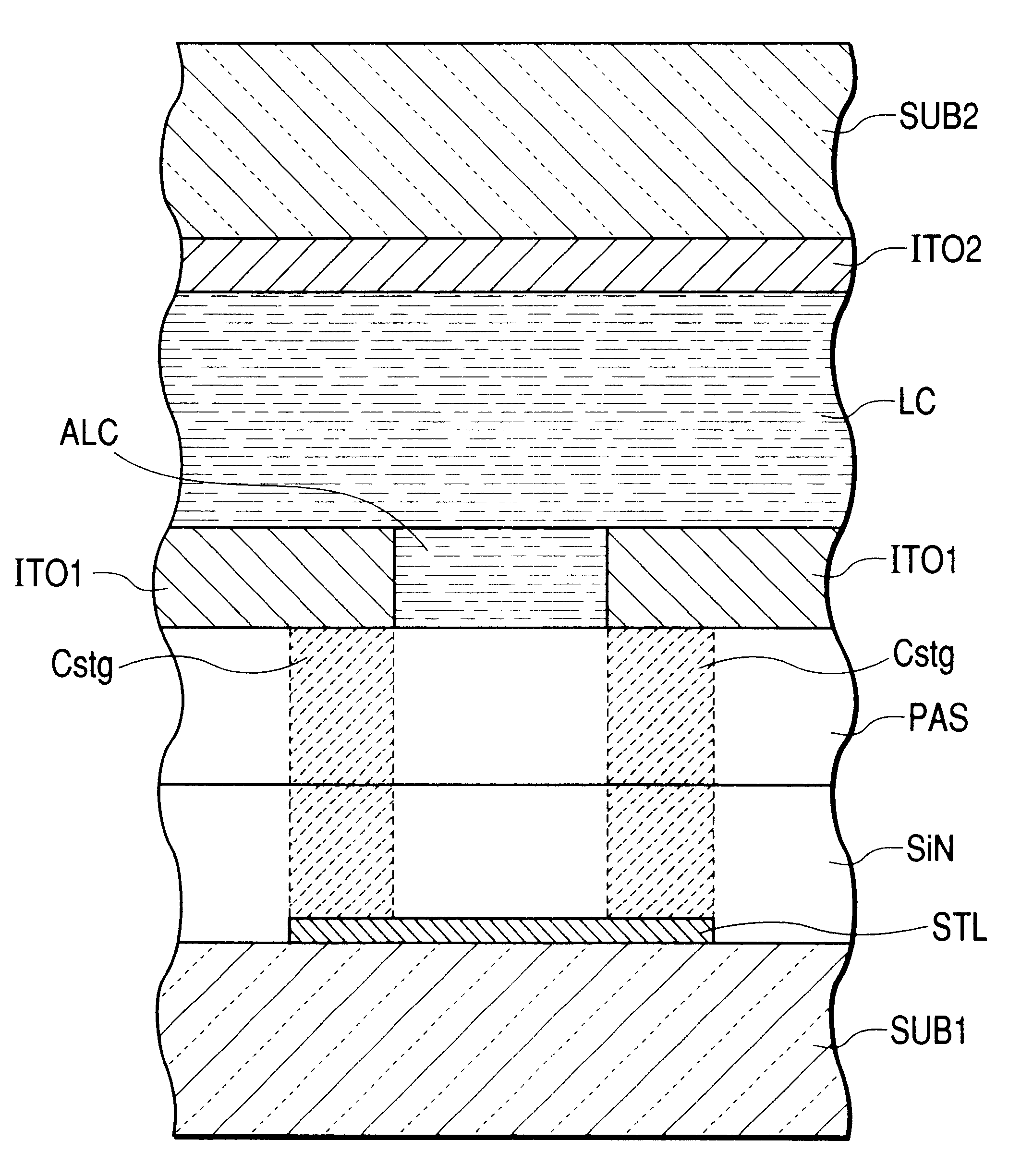

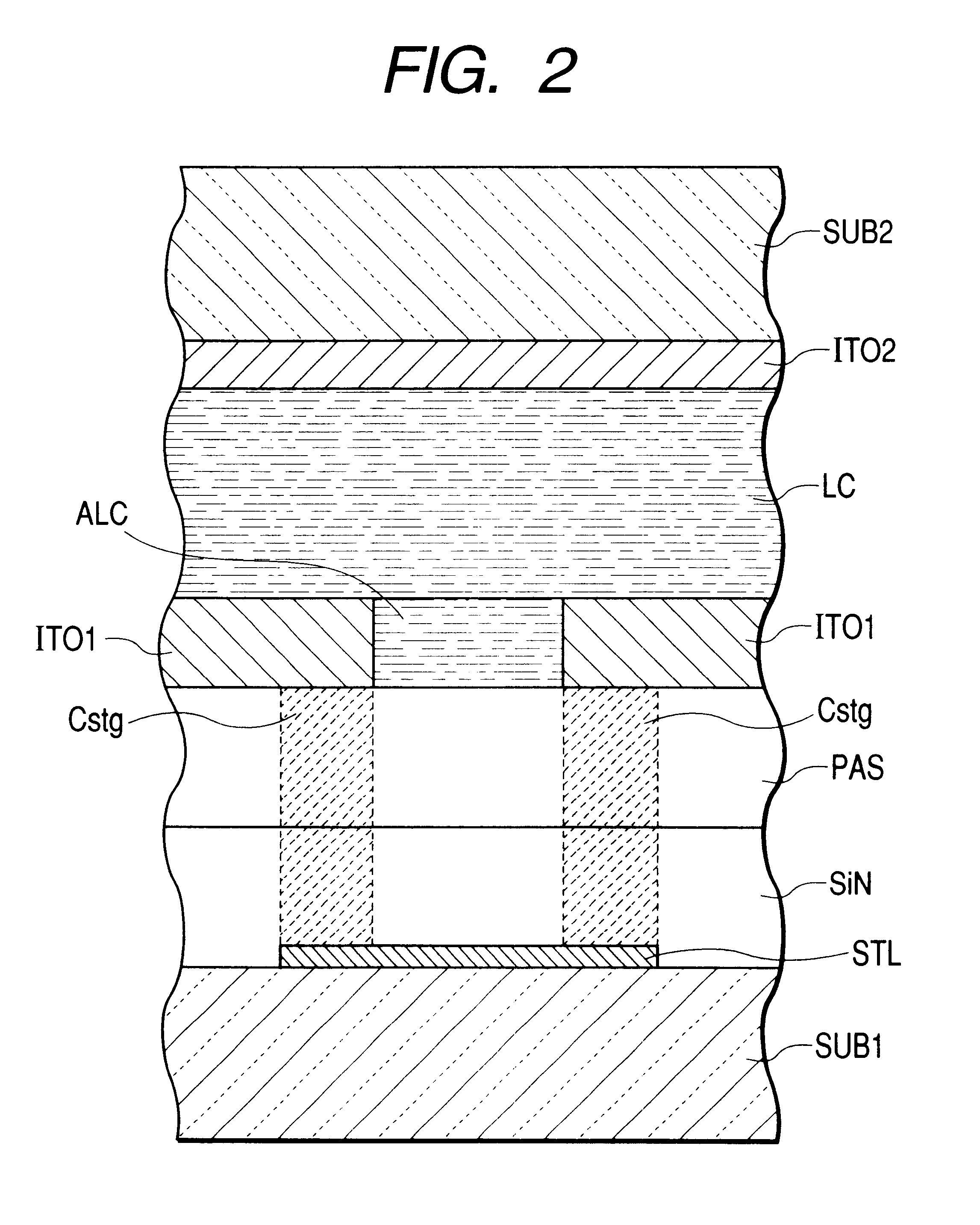

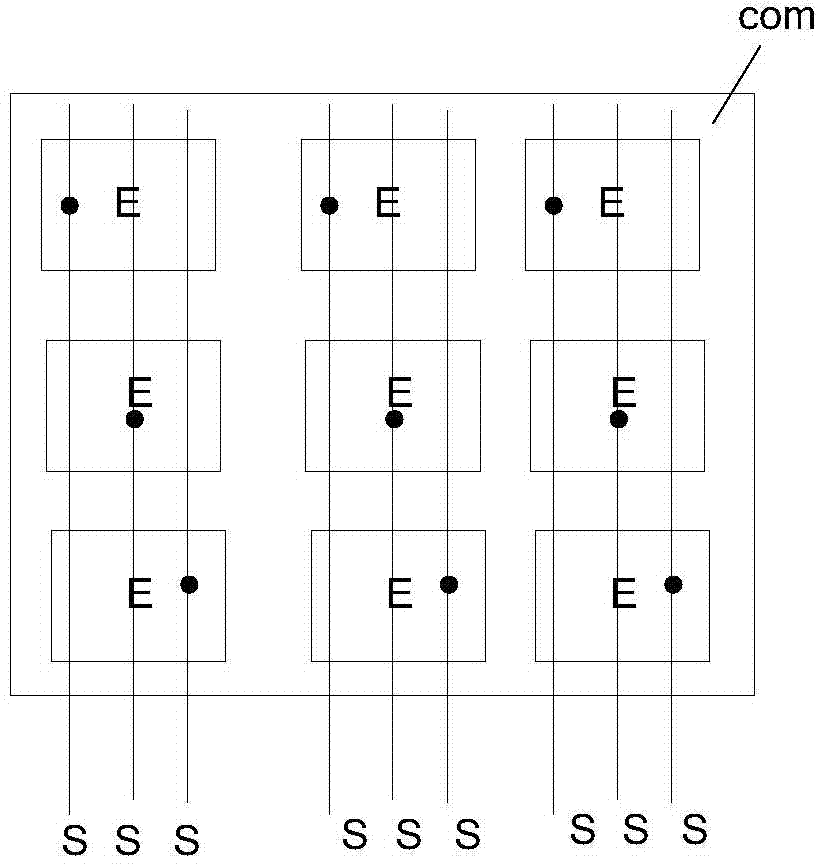

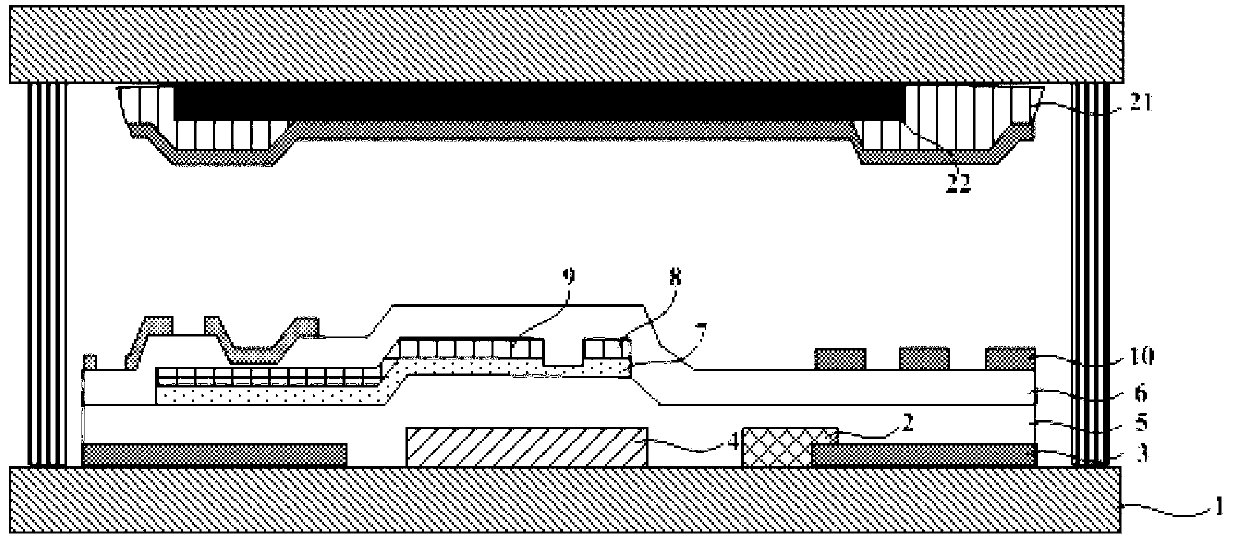

Liquid crystal display having an opening in each pixel electrode corresponding to each storage line

InactiveUS6583829B2Reduce storage capacitanceImprove manufacturing tactNon-linear opticsCapacitanceLiquid-crystal display

A liquid crystal display element includes a pair of substrates, a liquid crystal layer sandwiched therebetween, gate lines and drain lines disposed to intersect the gate lines disposed on one of the substrates, thin film transistors disposed at the intersections of the gate and drain lines, pixel electrodes disposed in an area surrounded by two adjacent gate lines and two adjacent drain lines, a common electrode disposed on the other substrate. The liquid crystal display element is also provided with storage lines disposed below the pixel electrodes with an insulating layer interposed therebetween to form a capacitance therebetween. Each of the pixel electrodes is formed with an opening in a portion thereof facing the storage lines.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

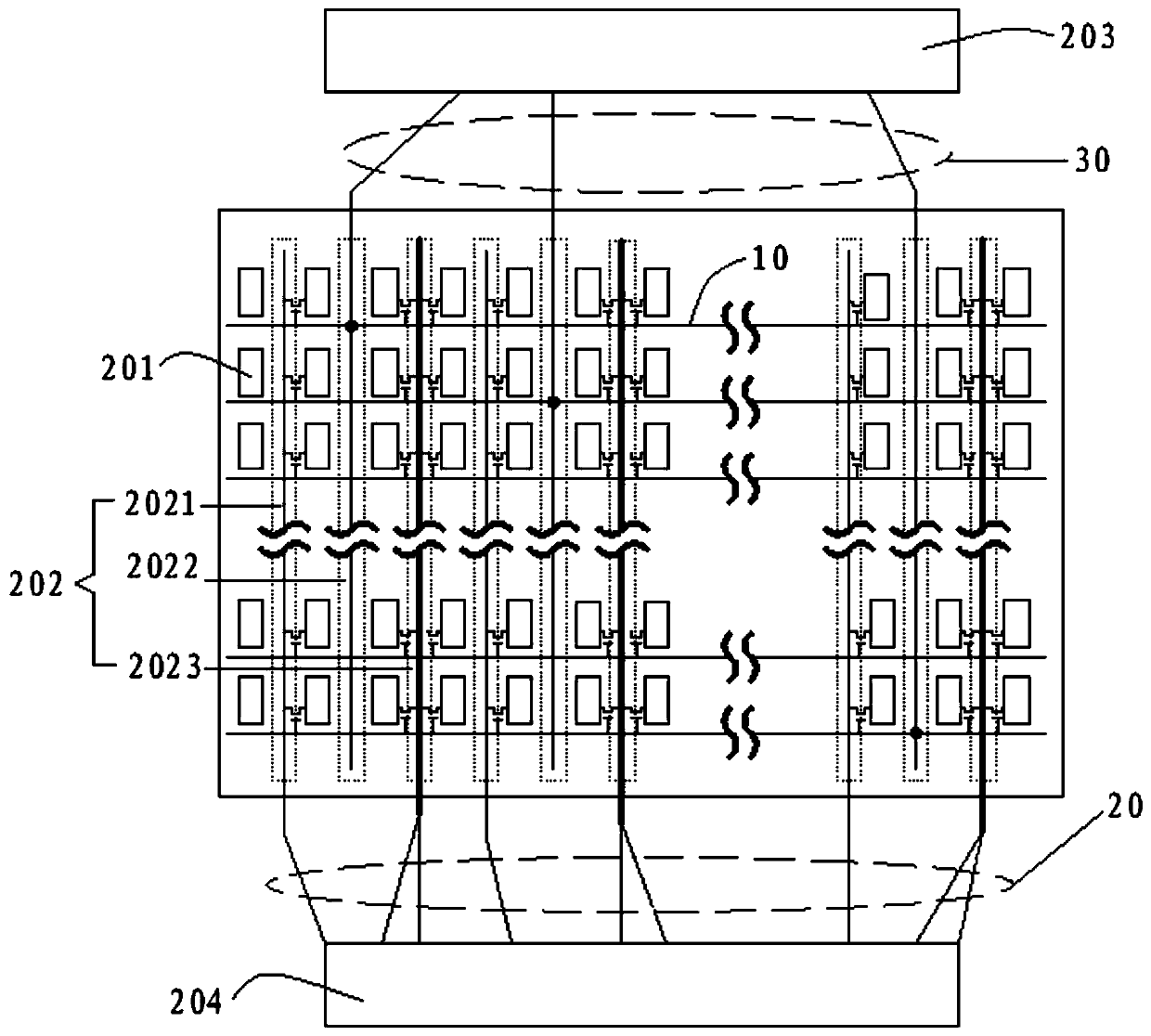

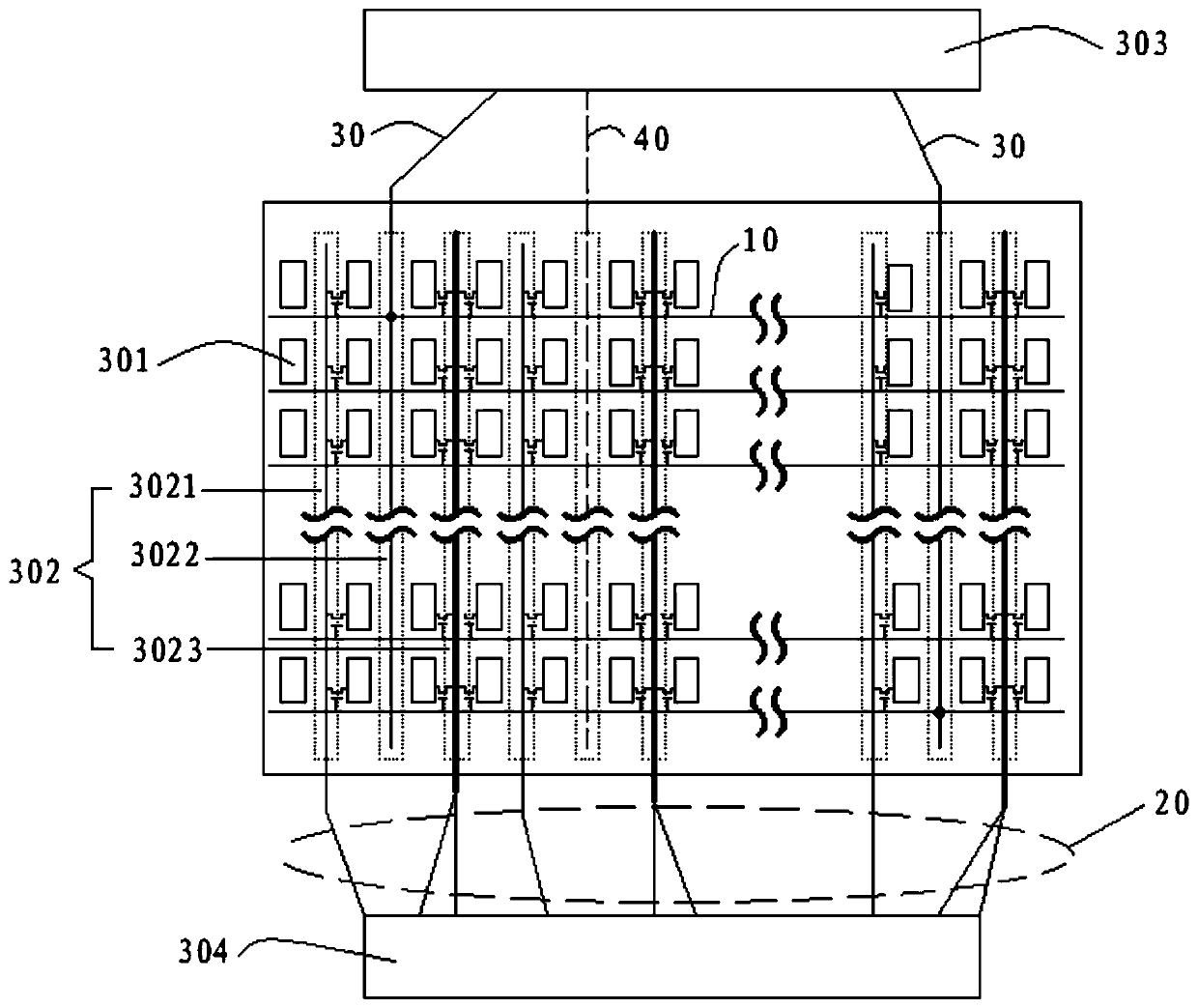

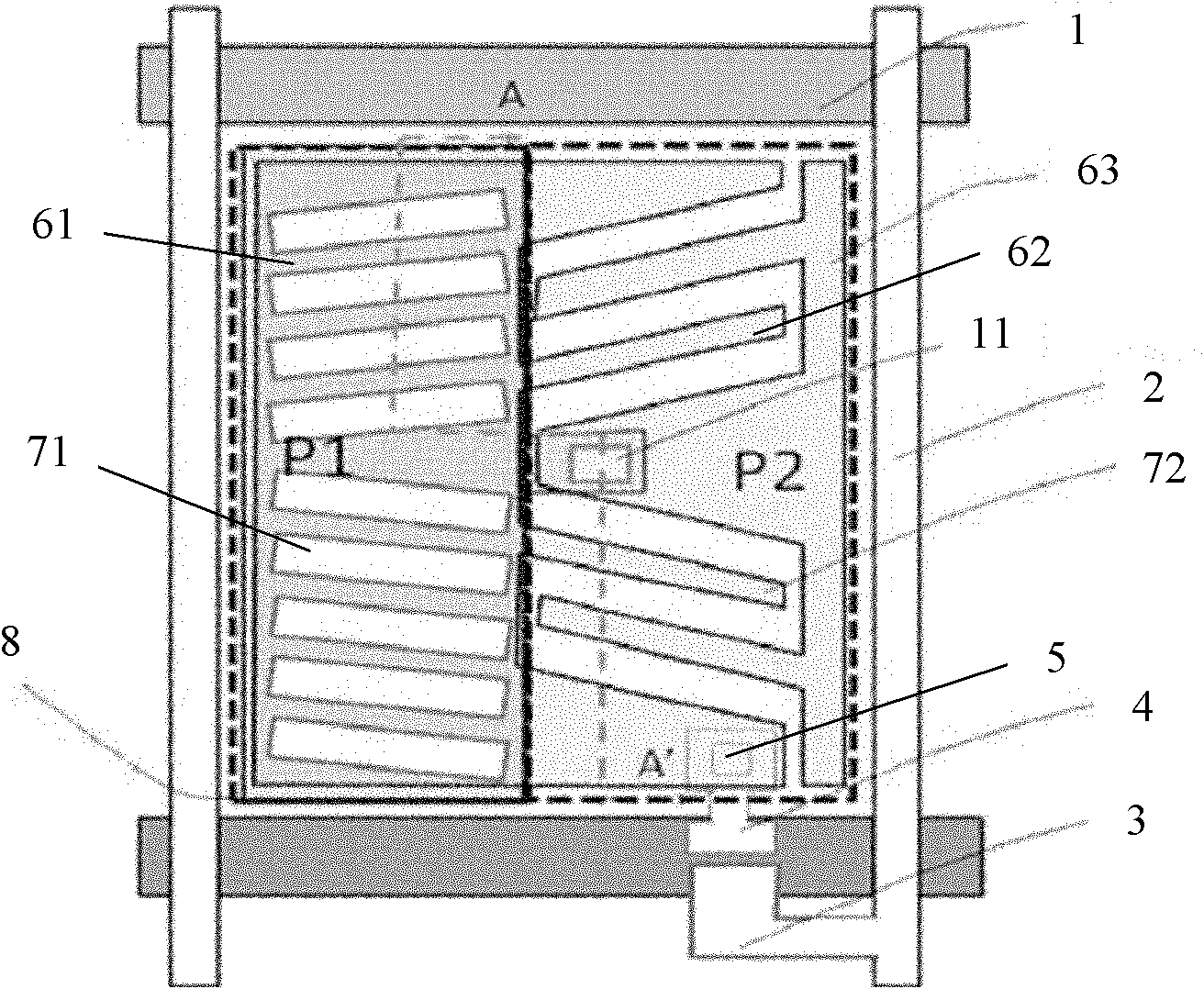

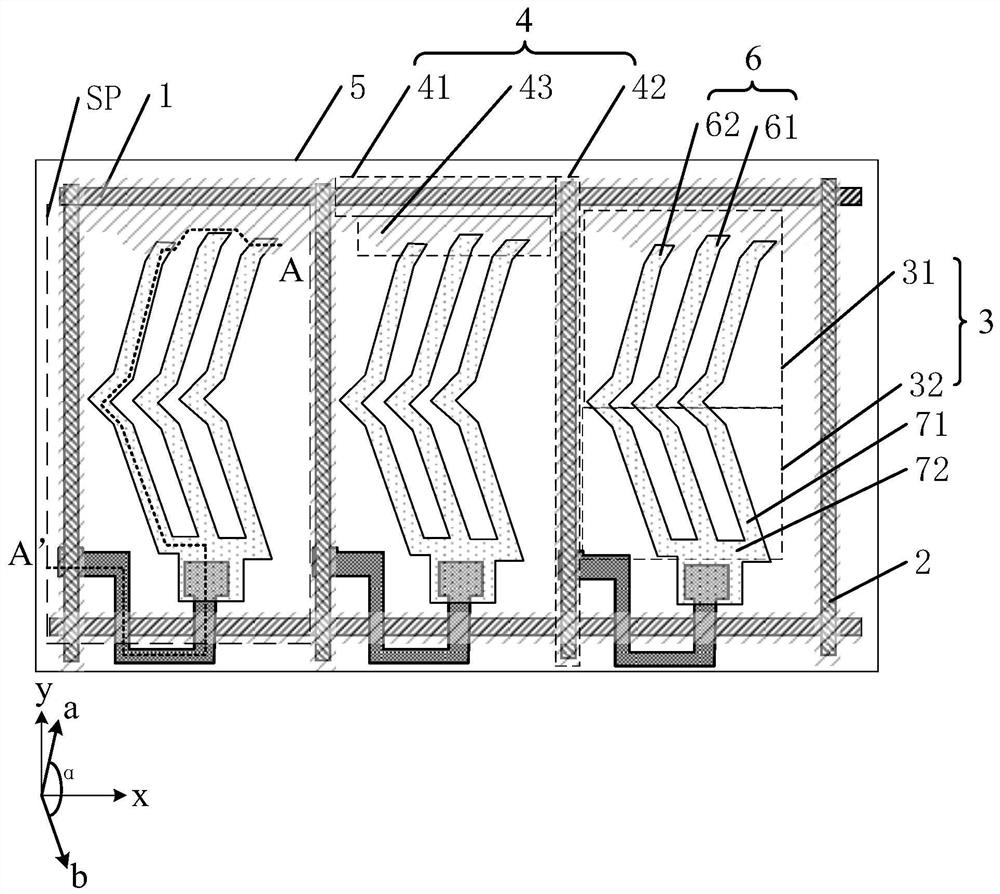

Array substrate, display panel and display device

ActiveCN104730782AReduce parasitic capacitanceReduce loadSolid-state devicesNon-linear opticsParasitic capacitanceDisplay device

Owner:BEIHAI HKC OPTOELECTRONICS TECH CO LTD

Method of Manufacturing an Array Substrate of a Transflective Liquid Crystal Display

ActiveUS20070287235A1Reduce in quantityIncrease capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayEngineering

A method of manufacturing an array substrate of a transflective liquid crystal display is provided. Utilizing backward exposure and half-tone photo-mask to reduce the number of photo-masks used in the manufacturing process, only three to four photo-masks are used to manufacture a transflective liquid crystal display.

Owner:AU OPTRONICS CORP

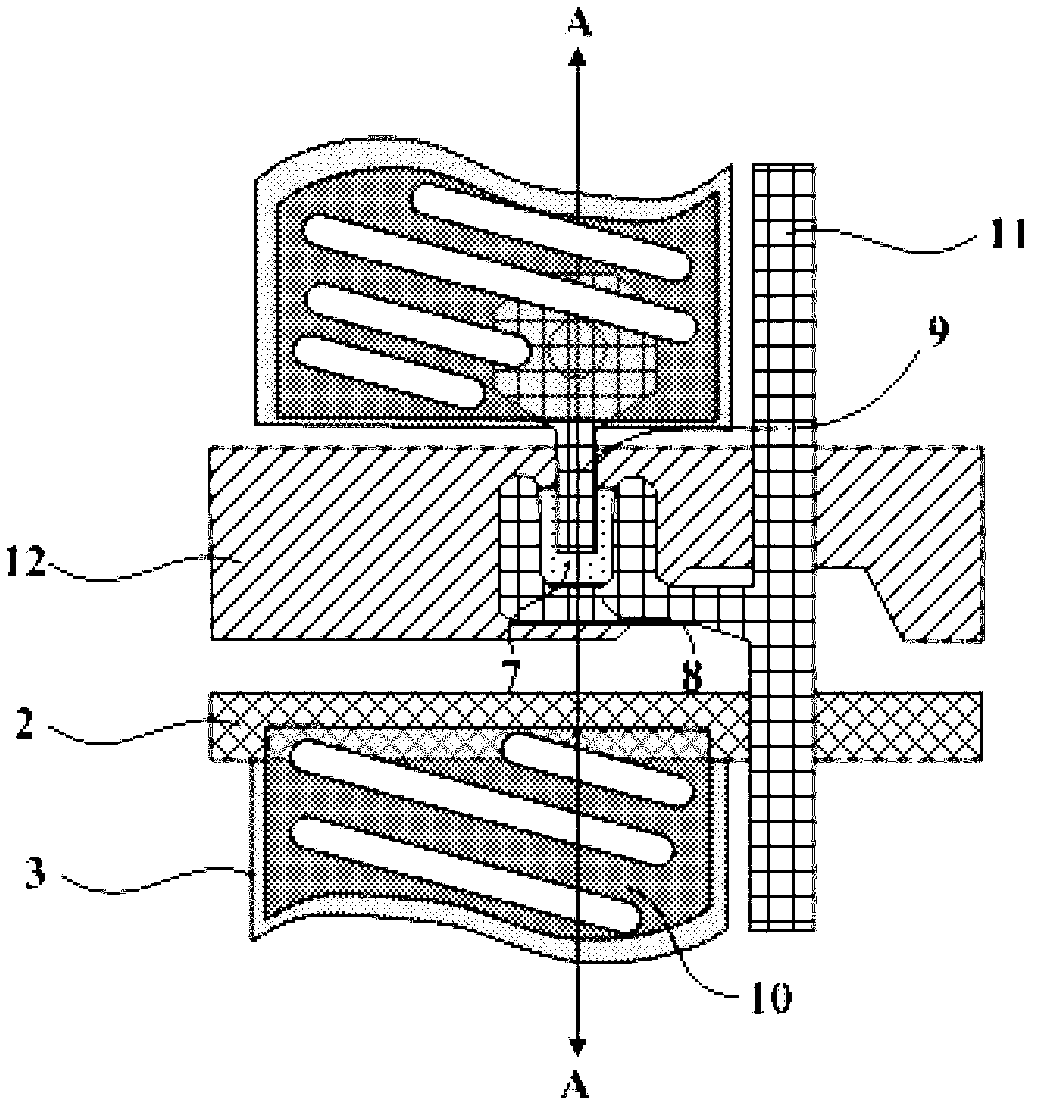

Array substrate, display device and manufacturing method of array substrate

ActiveCN103278986AReduce line widthShorten charging timeSolid-state devicesSemiconductor/solid-state device manufacturingScan lineColor film

The invention relates to the display technical field, and discloses an array substrate, a display device and a manufacturing method of the array substrate. The array substrate comprises an underlayer substrate and a plurality of thin film transistors arranged in an array and further comprises public electrode wires, public electrodes and an insulating layer, wherein the public electrode wires are positioned on the underlayer substrate, the public electrodes are positioned on the underlayer substrate and connected with the public electrode wires, and the insulating layer covers the public electrode wires, the public electrodes and the underlayer substrate. The thin film transistors are positioned on the insulating layer, and scanning lines connected with grids of the thin film transistors in each row are positioned above the public electrode wires. By adoption of the technical scheme, due to the fact that the public electrode wires are positioned below the scanning lines, and the insulating layer is adopted for carrying out insulating between the scanning lines and the public electrode wires, the line width of a black matrix of a color film substrate can be reduced correspondingly, and then an aperture opening ratio and transmittance of a panel are improved.

Owner:BOE TECH GRP CO LTD +1

Means of eliminating electrolytic capacitor as the energy storage component in the single phase AD/DC two-stage converter

ActiveUS8102165B2Reduce volatilityExtended service lifeEfficient power electronics conversionEnergy industryCapacitanceElectrolysis

A power factor correction (PFC) circuit includes an inductor, a diode, a storage capacitor, a switch and a control unit. The input power has a voltage fluctuation V1. The storage component absorbs a first voltage fluctuation and a switch regulation circuit absorbs a second voltage fluctuation V2. Thus output voltage from the PFC circuit is not a conventional constant voltage but a voltage of a great ripple. The PFC circuit further has a harmonic regulation unit. The harmonic regulation unit generates a voltage signal containing 3rd harmonic. The control unit receives a feedback signal and the voltage signal containing 3rd harmonic to generate a reference to the inductor current. Therefore, the inductor current contains 3rd harmonic. Thus power fluctuation absorbed and released by the capacitor is smaller. As a result energy storage capacitance can be reduced significantly.

Owner:SPI ELECTRONICS +1

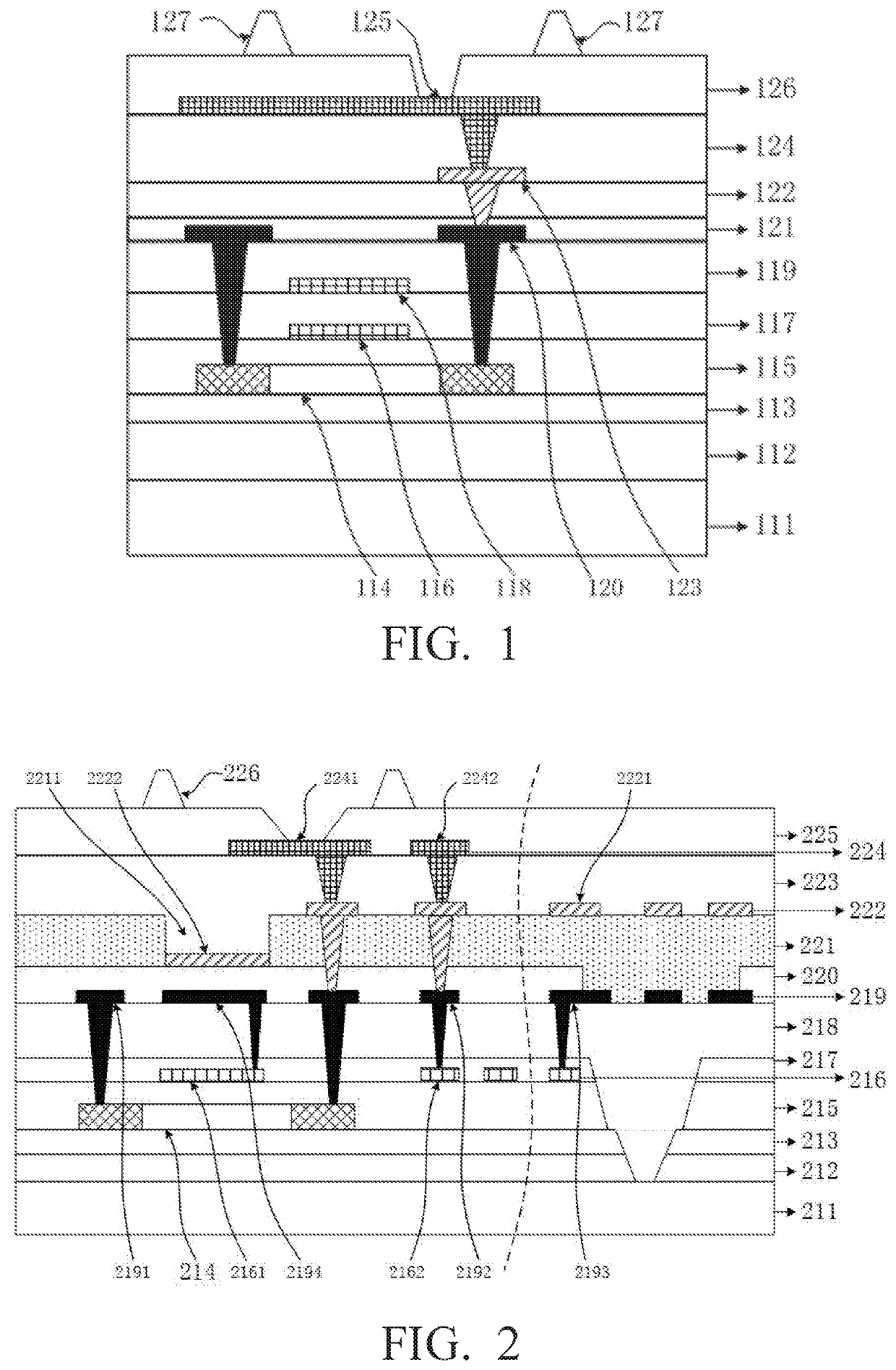

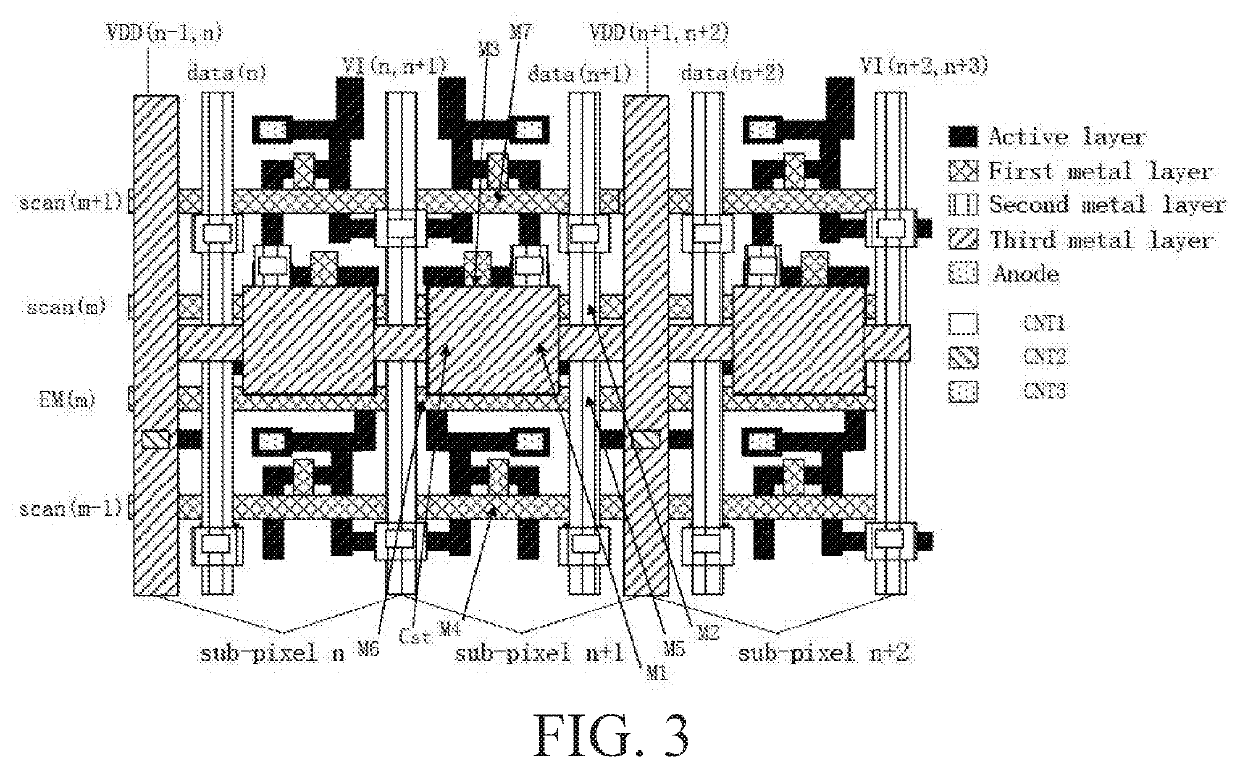

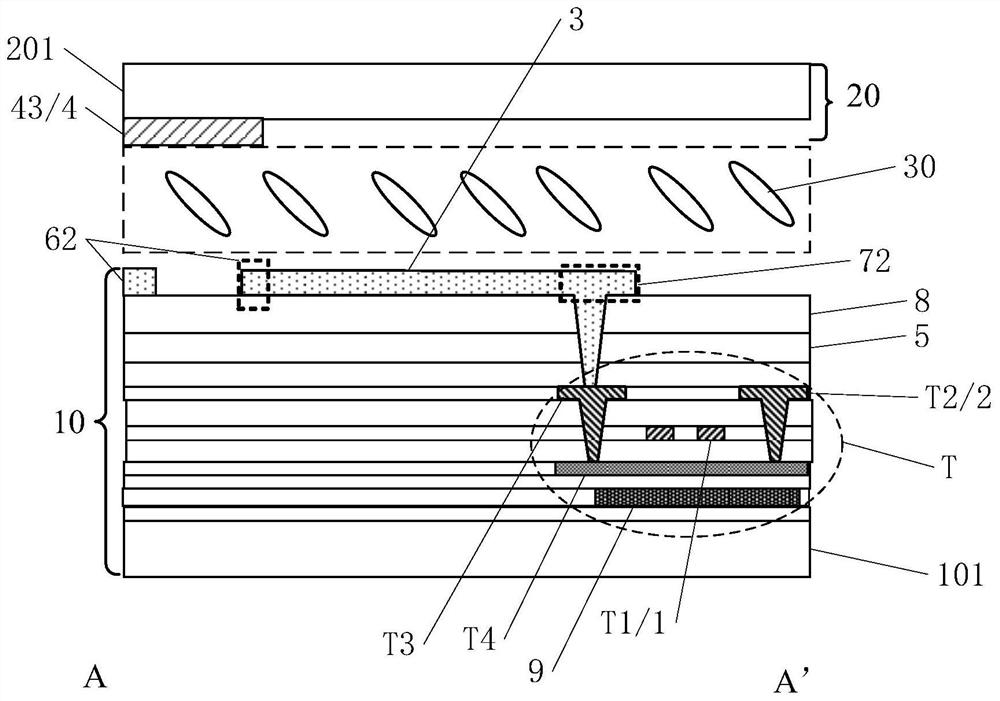

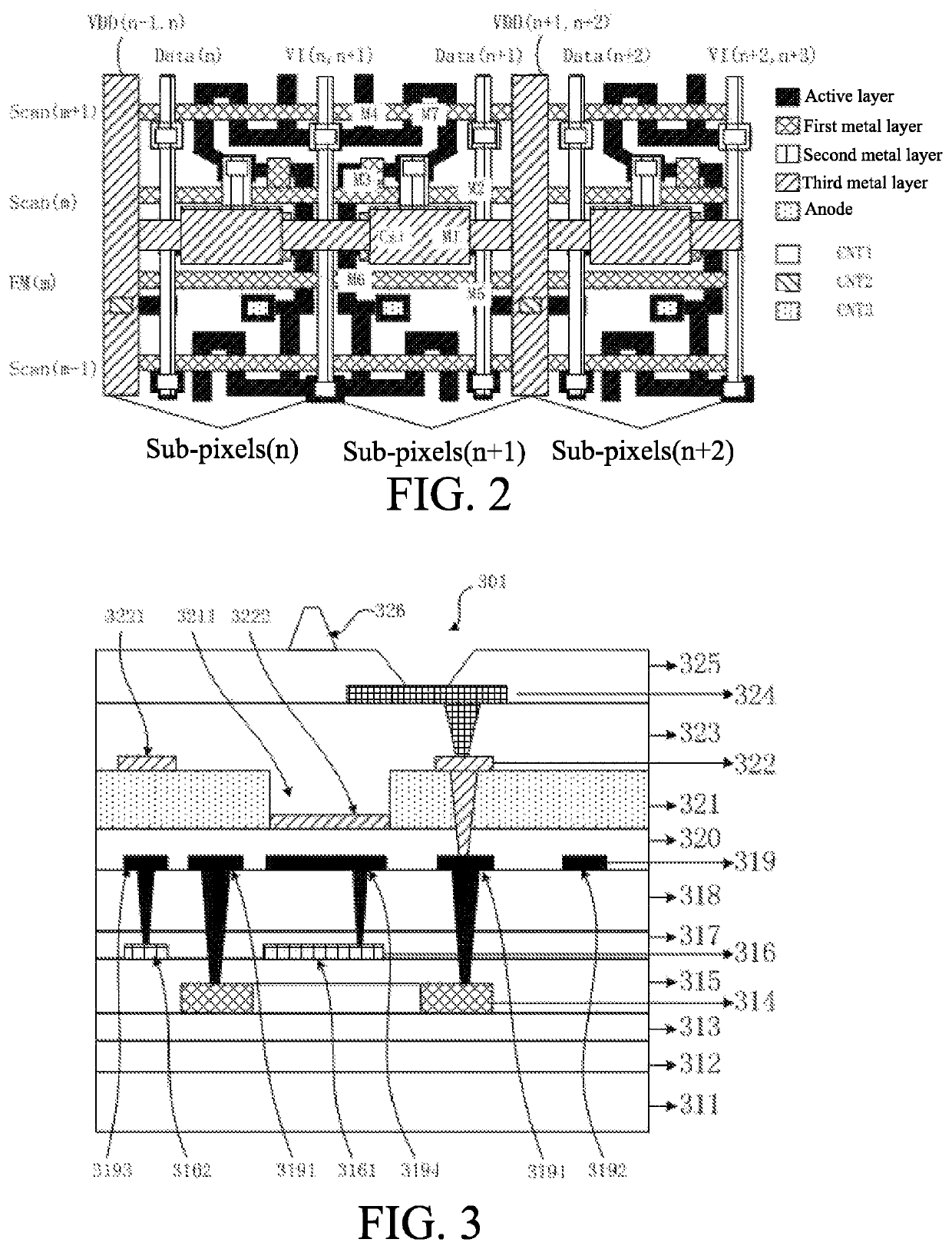

Array substrate and OLED display device

ActiveUS20210028259A1Improve display uniformityLarge capacitanceSolid-state devicesSemiconductor devicesCapacitanceDisplay device

An array substrate and an OLED display device are provided. A trace system of the array substrate is designed in a structure with three layers of metal. By providing one layer of inorganic insulation film and one layer of organic insulation film between two layers of metal, a coupling effect between two layers of trace can be reduced. By exposing all or part of an organic insulation film in a region, which will form a second electrode plate of a storage capacitor, a storage capacitor with larger capacitance can be formed. By forming a third metal layer as a mesh structure, it is possible to reduce IR drop without increasing mask and improve display uniformity of the display device.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

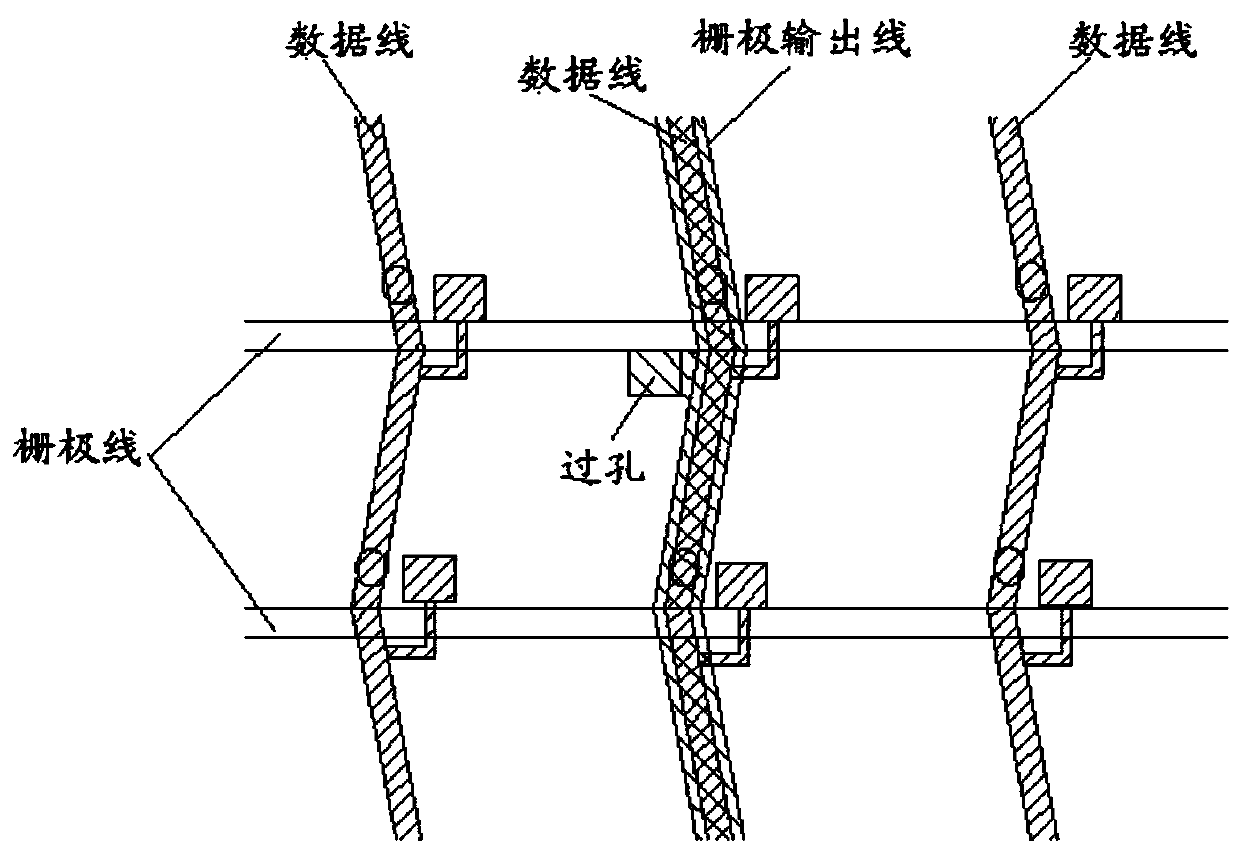

Thin film field effect transistor array substrate, manufacture method and display device thereof

InactiveCN102929052AEasy to chargeReduce crosstalkSemiconductor/solid-state device manufacturingNon-linear opticsTransistor arrayLiquid-crystal display

The invention provides a thin film field effect transistor array substrate, a manufacture method and a display device thereof and belongs to the field of liquid crystal display. The thin film field effect transistor array substrate comprises a plurality of grid lines, a plurality of data lines, sub pixel regions, a plurality of strip-shaped pixel electrodes formed in each sub pixel region and pixel electrode connection wires, wherein the grid lines are perpendicular to the data lines, the sub pixel regions are defined by crossing the grid lines and the data lines, and the pixel electrode connection wire is parallel to the data line and is connected with all the strip-shaped pixel electrodes in each sub pixel region. According to the technical scheme, display effects can be optimized.

Owner:BOE TECH GRP CO LTD +1

Array substrate, preparing method thereof and display device

InactiveCN103413784AReduce storage capacitanceGuaranteed qualitySolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceDisplay device

The invention provides an array substrate, a preparing method thereof and a display device. The preparing method of the array substrate comprises the steps that a public electrode and a pixel electrode are formed on the substrate, the public electrode is of a slit structure, and the pixel electrode is of a slit structure and has no overlap with the public electrode. According to the scheme, storage capacitance of the public electrode and storage capacitance of the pixel electrode can be reduced, and image quality is guaranteed.

Owner:BOE TECH GRP CO LTD

Pixel structure, array substrate and display device

InactiveCN103676353AReduce storage capacitanceImprove transmittanceNon-linear opticsCapacitanceHigh transmittance

The invention discloses a pixel structure, an array substrate and a display device. The pixel structure comprises a first electrode and a second electrode, wherein the first electrode comprises a plurality of first electrode parts and a plurality of first gaps located between the adjacent first electrode parts, the second electrode comprises a plurality of parallel strip-shaped second electrode parts and a plurality of second gaps located between the adjacent second electrode parts, the downward perpendicular projection of each first electrode part is overlapped with the downward perpendicular projection of each second electrode part, the second electrode comprises third electrode parts, and each second electrode part is connected with the adjacent electrode part through one third electrode part. The array substrate comprises the pixel structure. The display device comprises the array substrate. According to the technical scheme, storage capacitance is reduced, the second electrode is designed in a narrow gap patterning mode, and on the basis of reducing the storage capacitance, high transmittance and high technological yield are maintained.

Owner:BOE TECH GRP CO LTD

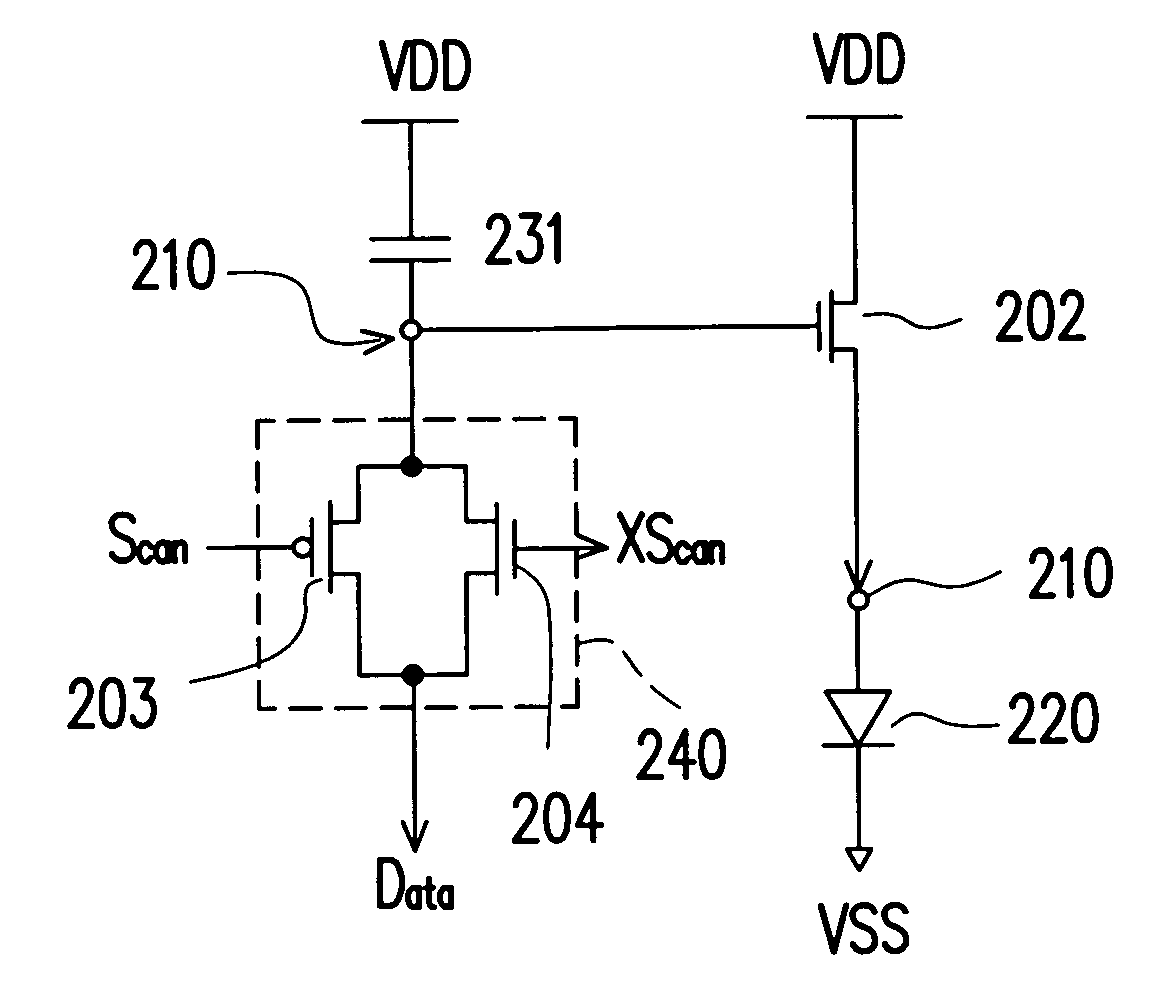

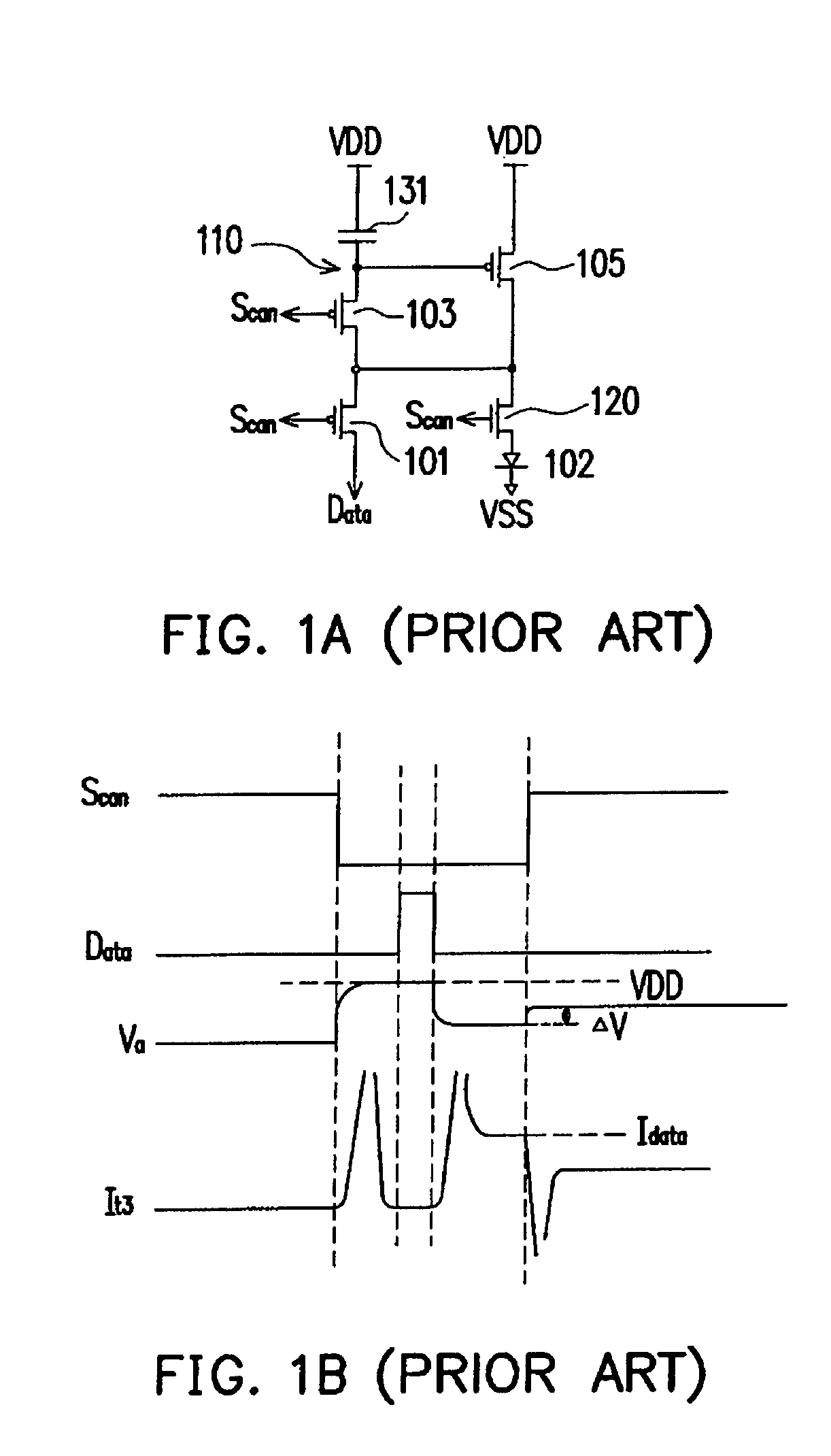

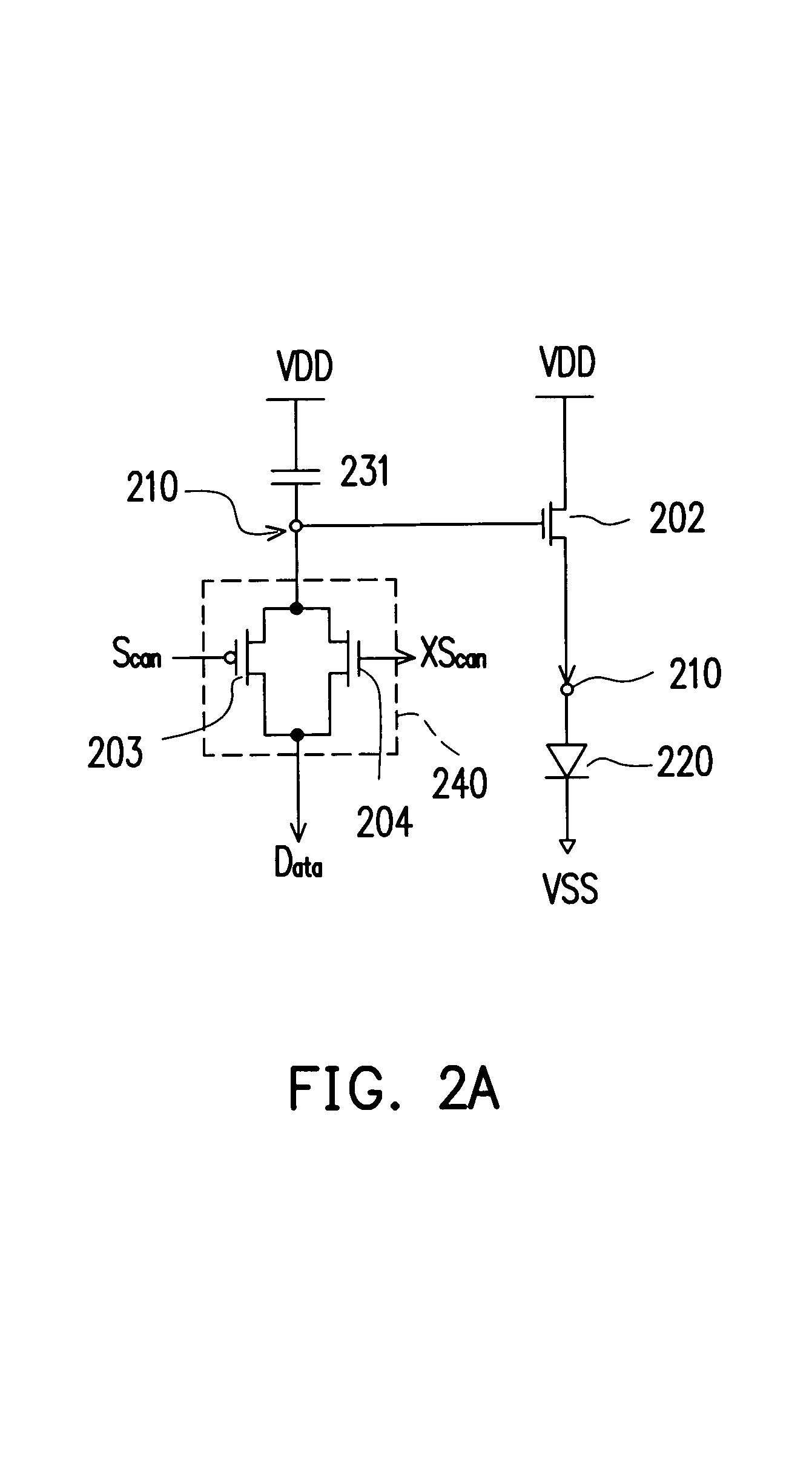

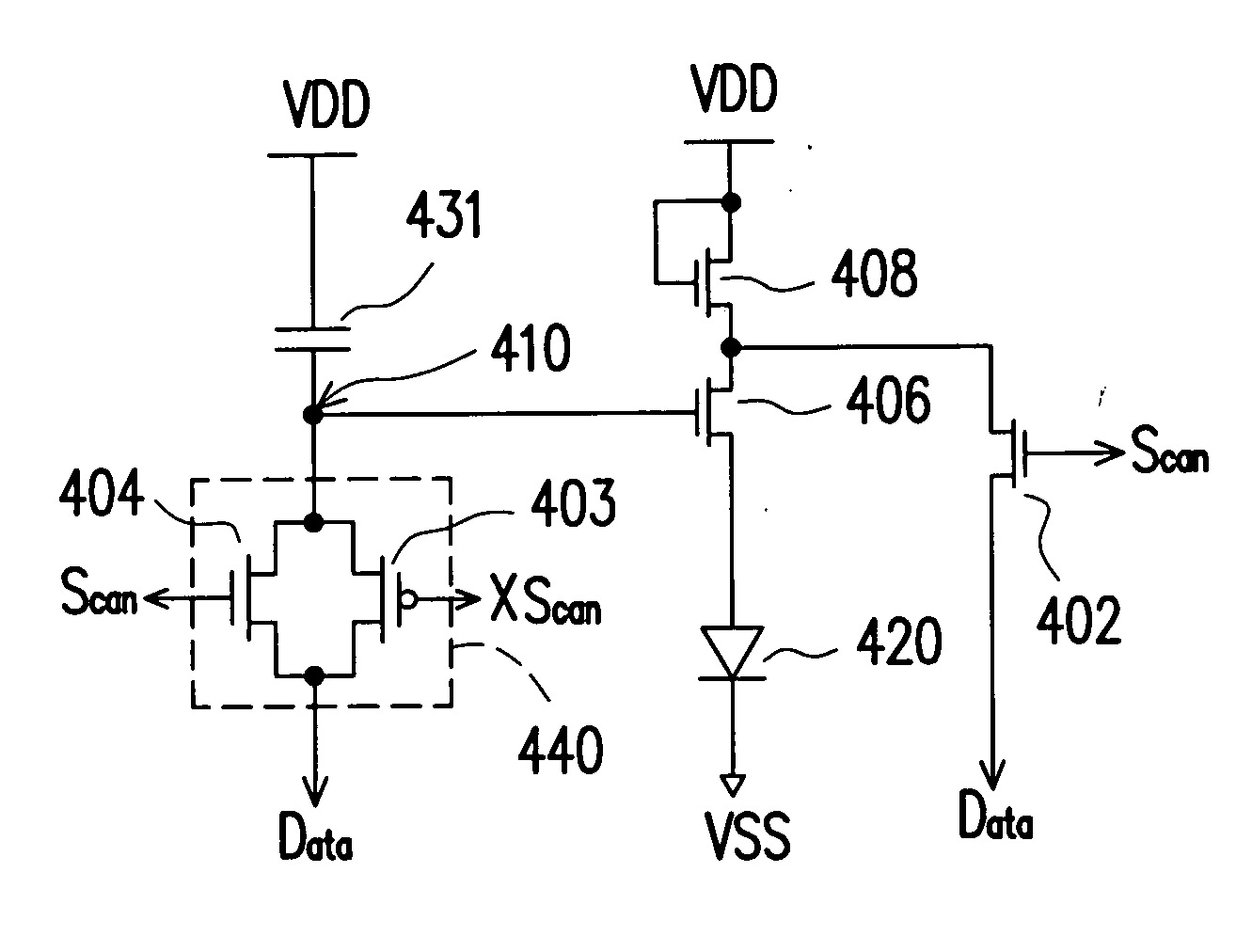

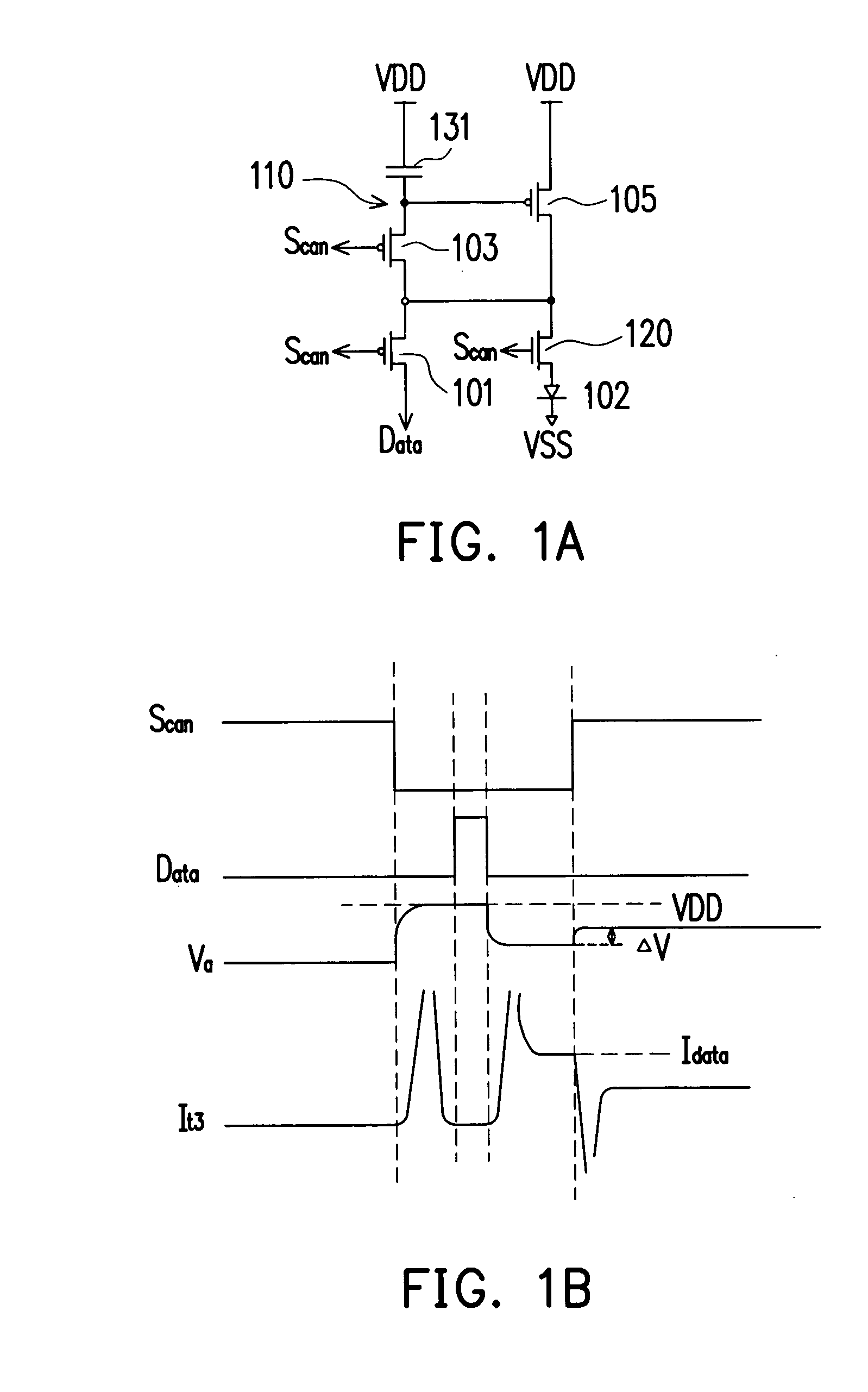

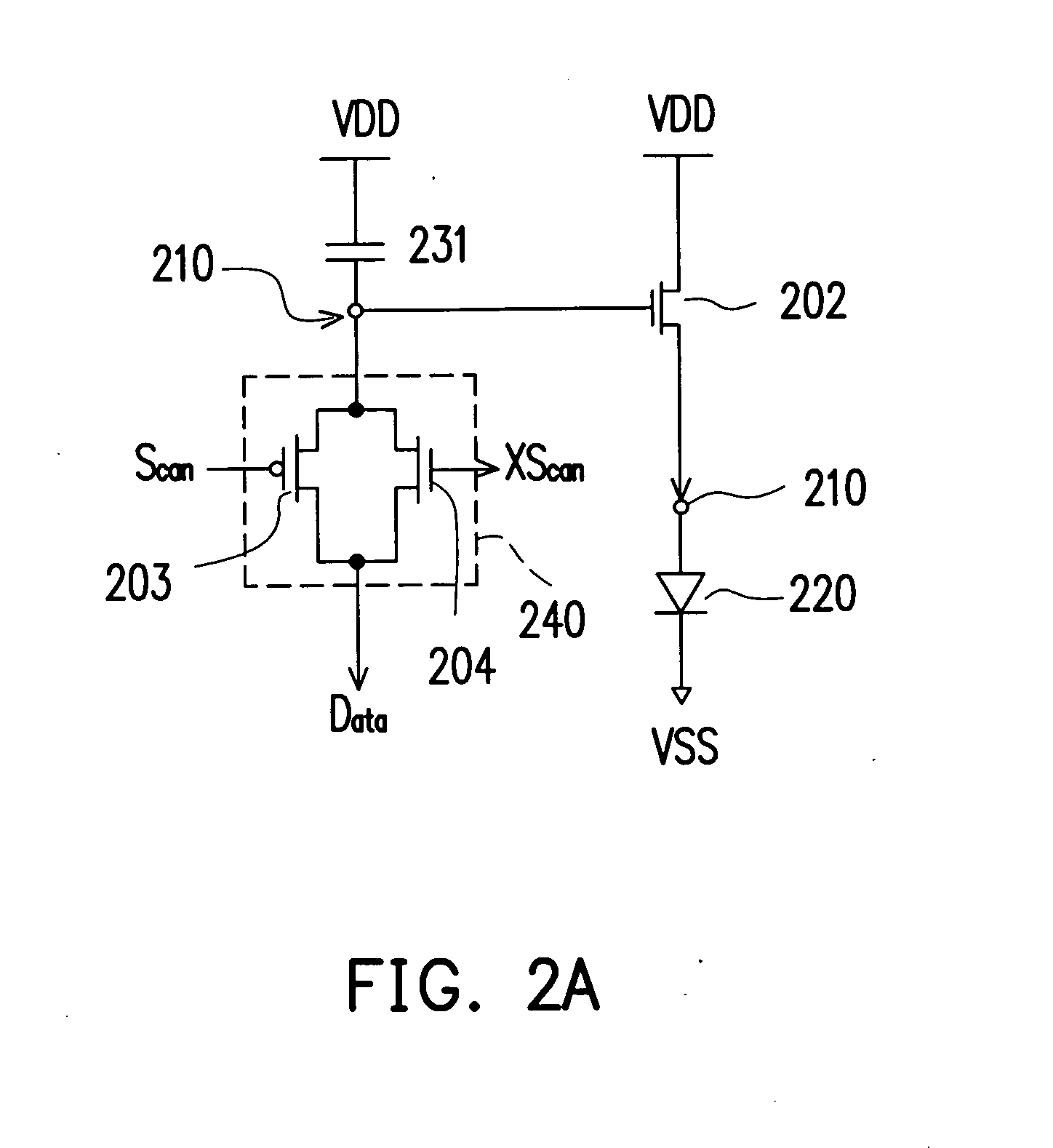

Circuit for driving flat panel display

ActiveUS7292210B2Increase speedReduce impactStatic indicating devicesTransmission gateCurrent limiting

The present invention provides a circuit for driving a flat panel display, including a storage capacitor, a transmission gate and a current-limiting transistor. A first terminal of the storage capacitor is coupled to a system voltage, and a second terminal of the storage capacitor is at storage voltage. A first input / output terminal of the transmission gate is coupled to the storage voltage, and the second input / output terminal of the transmission gate is coupled to the data current source. A first gate terminal of the transmission gate is coupled to the first signal; a second gate terminal of the transmission gate is coupled to the second signal. A gate terminal of the current-limiting transistor is coupled to the storage voltage, wherein a first source / drain terminal is coupled to the system voltage, and a second source / drain terminal provides current for driving the flat panel display.

Owner:AU OPTRONICS CORP

Pixel structure and making method thereof, array substrate and display device

InactiveCN105487311AImprove charging efficiencyReduce overlapping areasNon-linear opticsCapacitanceDisplay device

The invention relates to the technical field of display, and discloses a pixel structure and a making method thereof, an array substrate and a display device. The pixel structure comprises a substrate and a first transparent electrode layer and a second transparent electrode layer which are arranged on the substrate, the second transparent electrode layer comprises multiple strip-shaped electrodes, the first transparent electrode layer comprises at least one slit, and each slit is at least partially located in a projection of the corresponding the strip-shaped electrode in the substrate. According to the pixel structure, by means of the slits formed in the first transparent electrode layer, the overlapping regions of the first transparent electrode layer and the second transparent electrode layer is effectively decreased, storage capacitance formed between the overlapping regions is decreased, and the charging efficiency of pixels and the display quality of the display device are improved.

Owner:CHONGQING BOE OPTOELECTRONICS +1

Circuit for driving flat panel display

ActiveUS20050122290A1Improve reaction speedImprove response speedStatic indicating devicesCapacitanceTransmission gate

The present invention provides a circuit for driving a flat panel display, including a storage capacitor, a transmission gate and a current-limiting transistor. A first terminal of the storage capacitor is coupled to a system voltage, and a second terminal of the storage capacitor is at storage voltage. A first input / output terminal of the transmission gate is coupled to the storage voltage, and the second input / output terminal of the transmission gate is coupled to the data current source. A first gate terminal of the transmission gate is coupled to the first signal; a second gate terminal of the transmission gate is coupled to the second signal. A gate terminal of the current-limiting transistor is coupled to the storage voltage, wherein a first source / drain terminal is coupled to the system voltage, and a second source / drain terminal provides current for driving the flat panel display.

Owner:AU OPTRONICS CORP

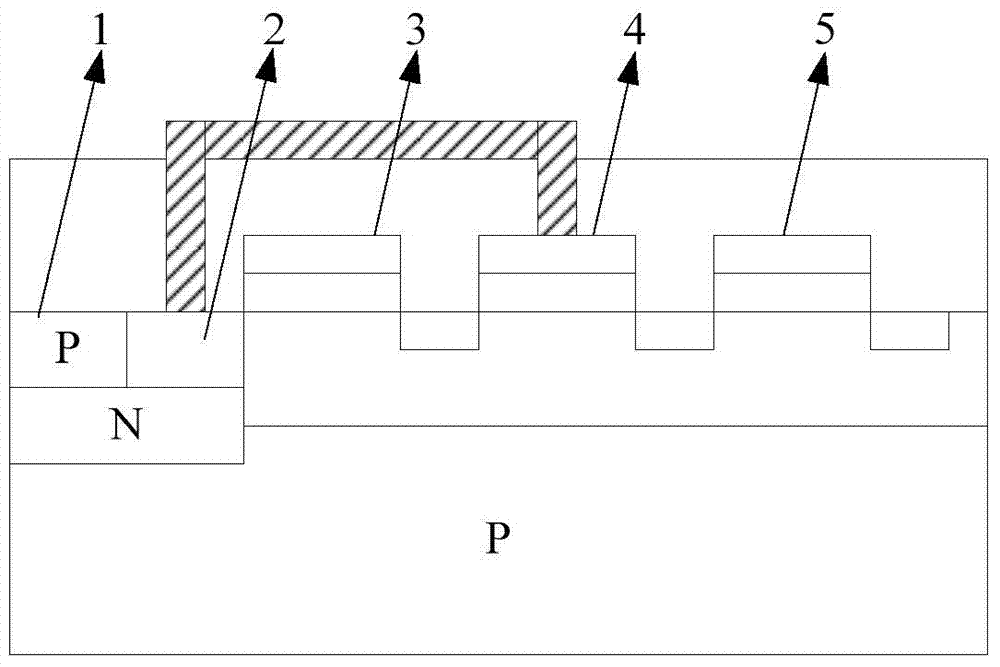

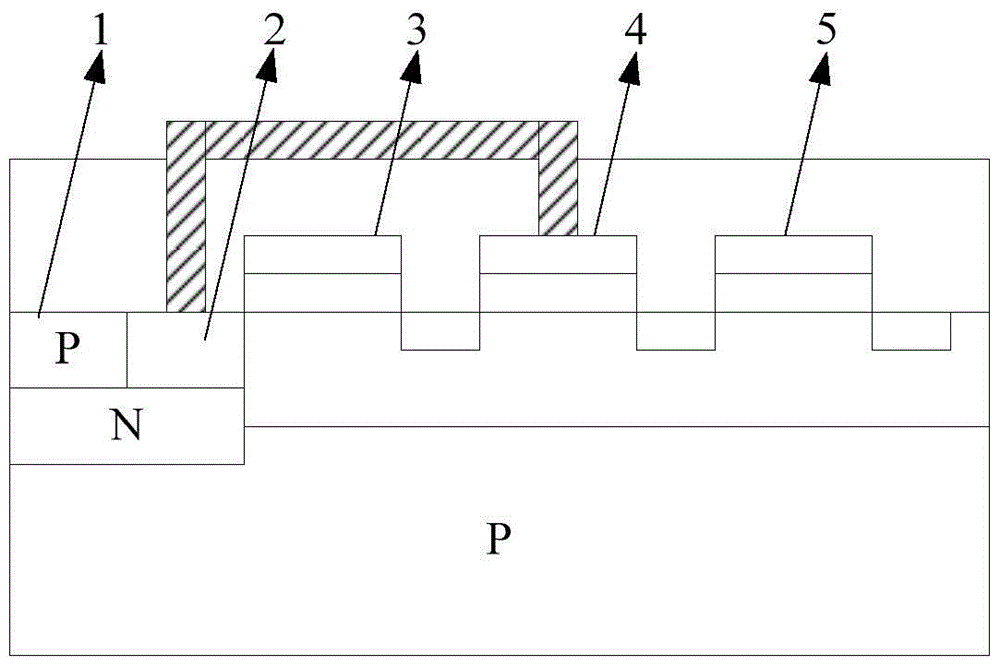

CMOS image sensor

ActiveCN104269418ASpeed up the flowReduce storage capacitanceRadiation controlled devicesCMOSSemiconductor

The embodiment of the invention provides a CMOS image sensor and relates to the technical field of semiconductors. The CMOS image sensor can achieve high-sensitivity and high-speed responses. Each pixel unit of the CMOS image sensor comprises a P type semiconductor substrate, a first N type ion layer on the upper portion of the P type semiconductor substrate, a P trap surrounding the first N type ion layer, a second N type ion layer, a third N type ion layer, a first P type ion layer and a second P type ion layer, wherein the second N type ion layer, the third N type ion layer, the first P type ion layer and the second P type ion layer are arranged on the upper portion of the first N type ion layer; the first P type ion layer and the second P type ion layer are spaced by the second N type ion layer, the second N type ion layer and the third N type ion layer are spaced by the second P type ion layer, the doping concentration of the second N type ion layer and the doping concentration of the third N type ion layer are larger than the doping concentration of the first N type ion layer, and the doping concentration of the first P type ion layer and the doping concentration of the second P type ion layer are between the doping concentration of the P trap and the doping concentration of the P type semiconductor substrate. The CMOS image sensor is used for sensor manufacturing.

Owner:BOE TECH GRP CO LTD

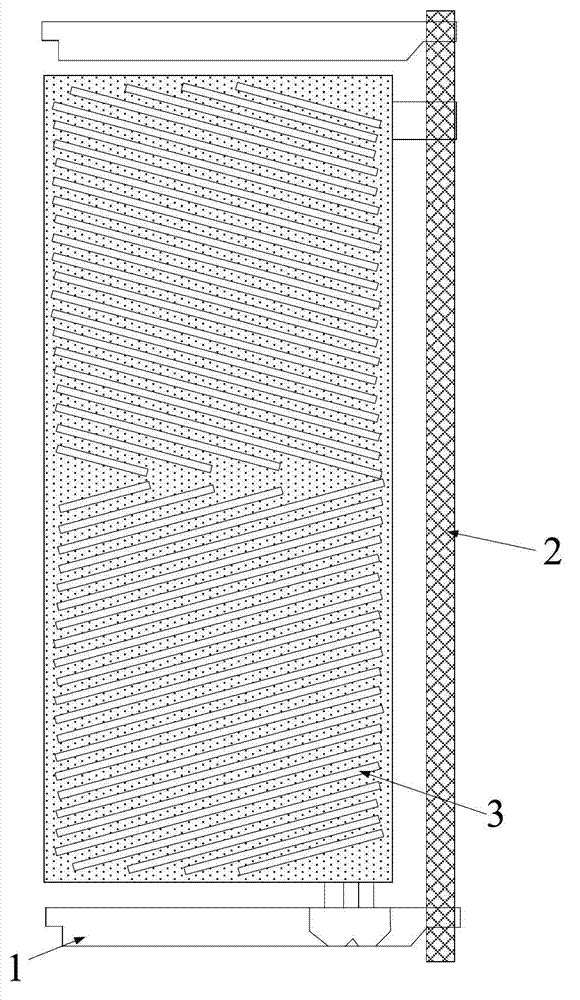

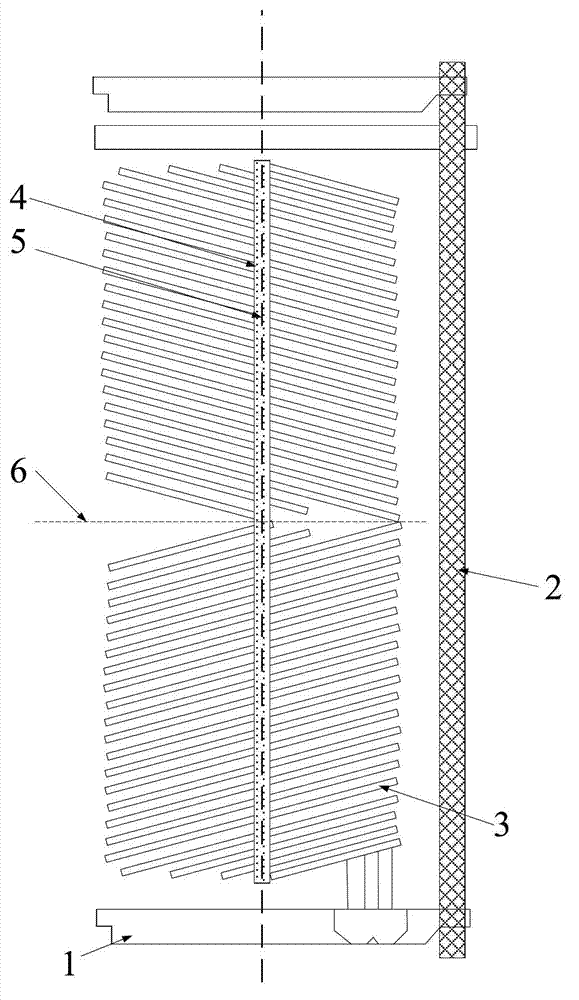

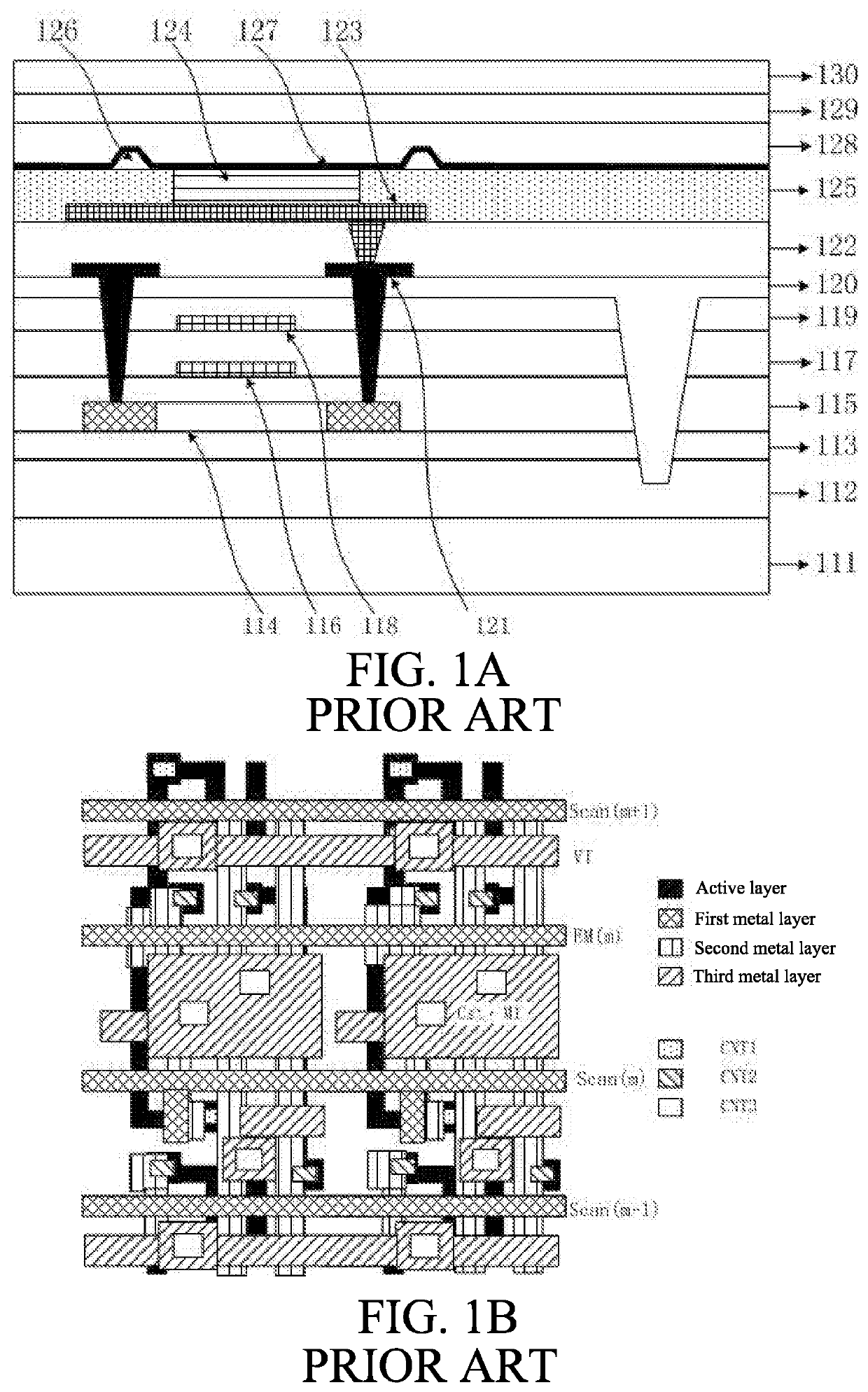

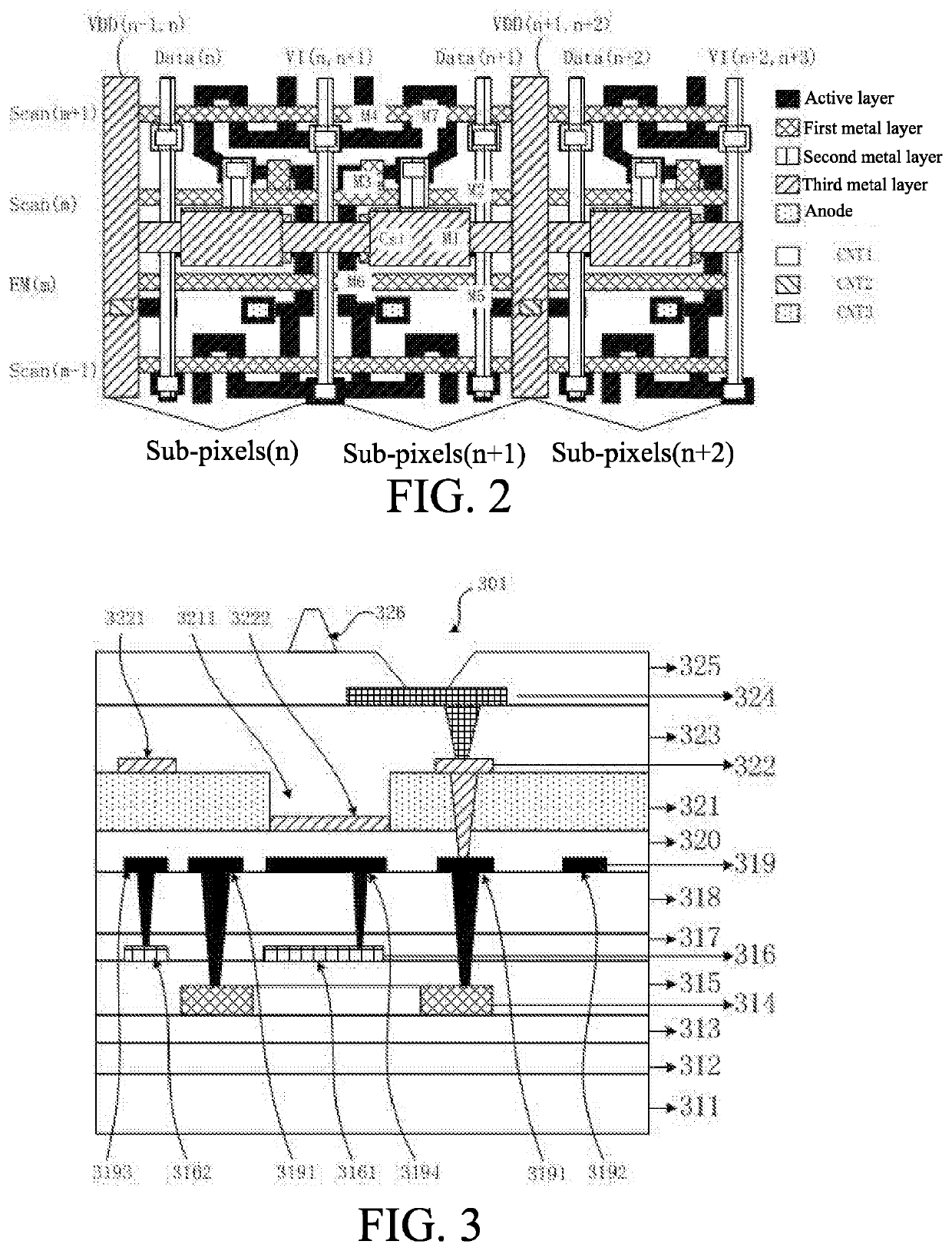

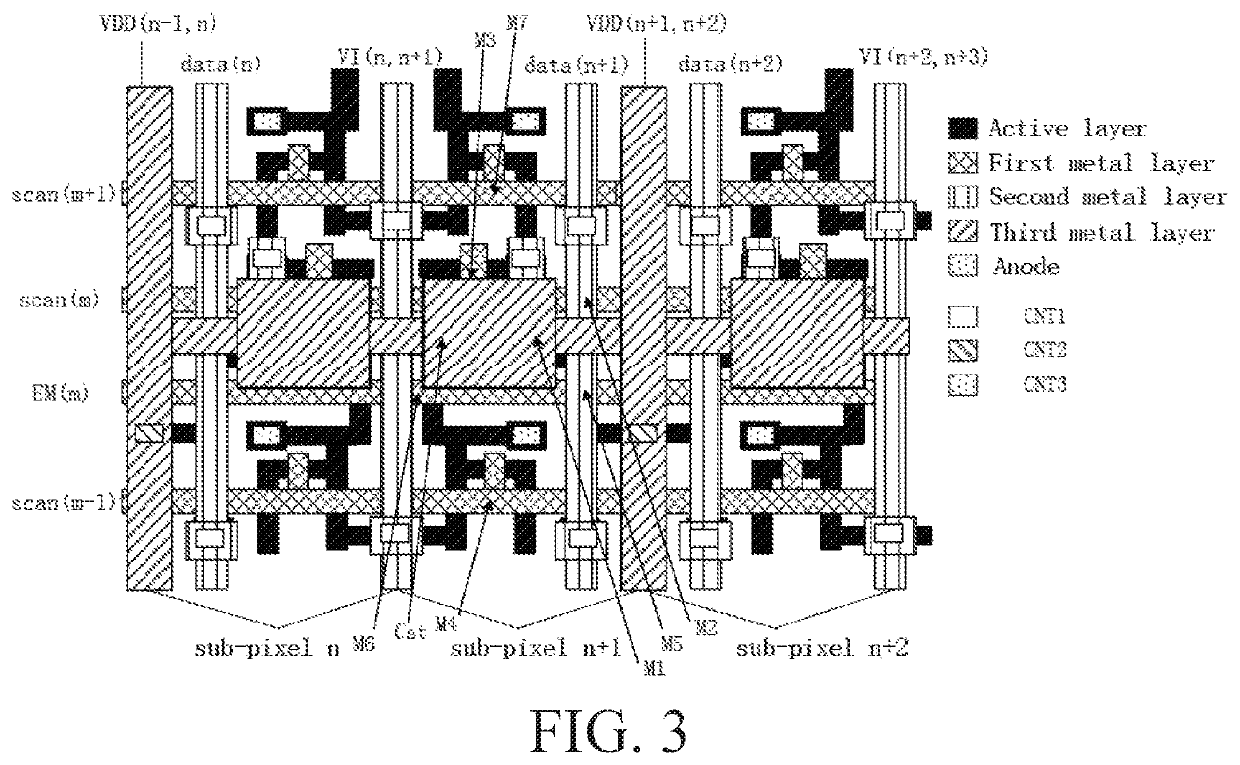

OLED array substrate and OLED display device

ActiveUS20210126075A1Great pixel densityIncrease image display uniformitySolid-state devicesSemiconductor devicesPhysicsEngineering

An organic light-emitting diode (OLED) array substrate and an OLED display device are provided. The OLED array substrate includes a plurality of driving circuits of a plurality of sub-pixels using a mirror symmetrical structure, and a plurality of reset signal lines and a plurality of power signal lines extending along a same direction. By sharing each of the reset signal lines and each of a plurality of first vias, and sharing each of the power signal lines and each of a plurality of second vias, about half of lines of power signal lines, reset signal lines, and vias are saved. Therefore, room for increasing pixels per inch (PPI) is provided, facilitating realizing high PPI panel designs.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Display substrate, method of manufacturing the same, display panel and display device

ActiveUS20170131598A1Reduce storage capacitanceReduce displayNon-linear opticsDisplay deviceEngineering

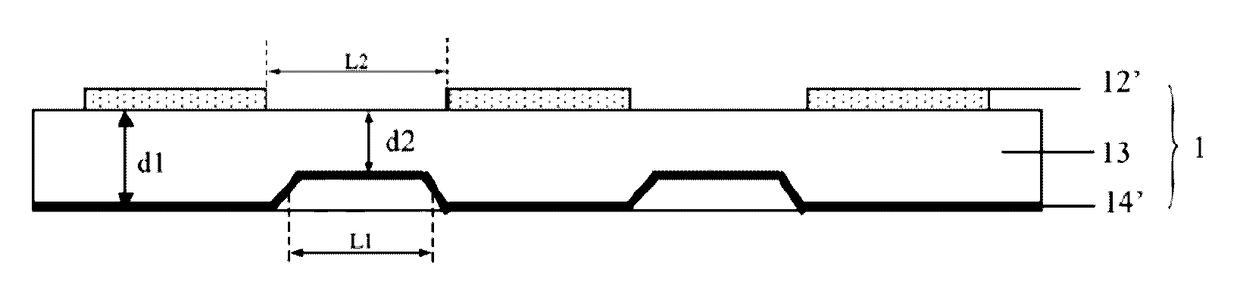

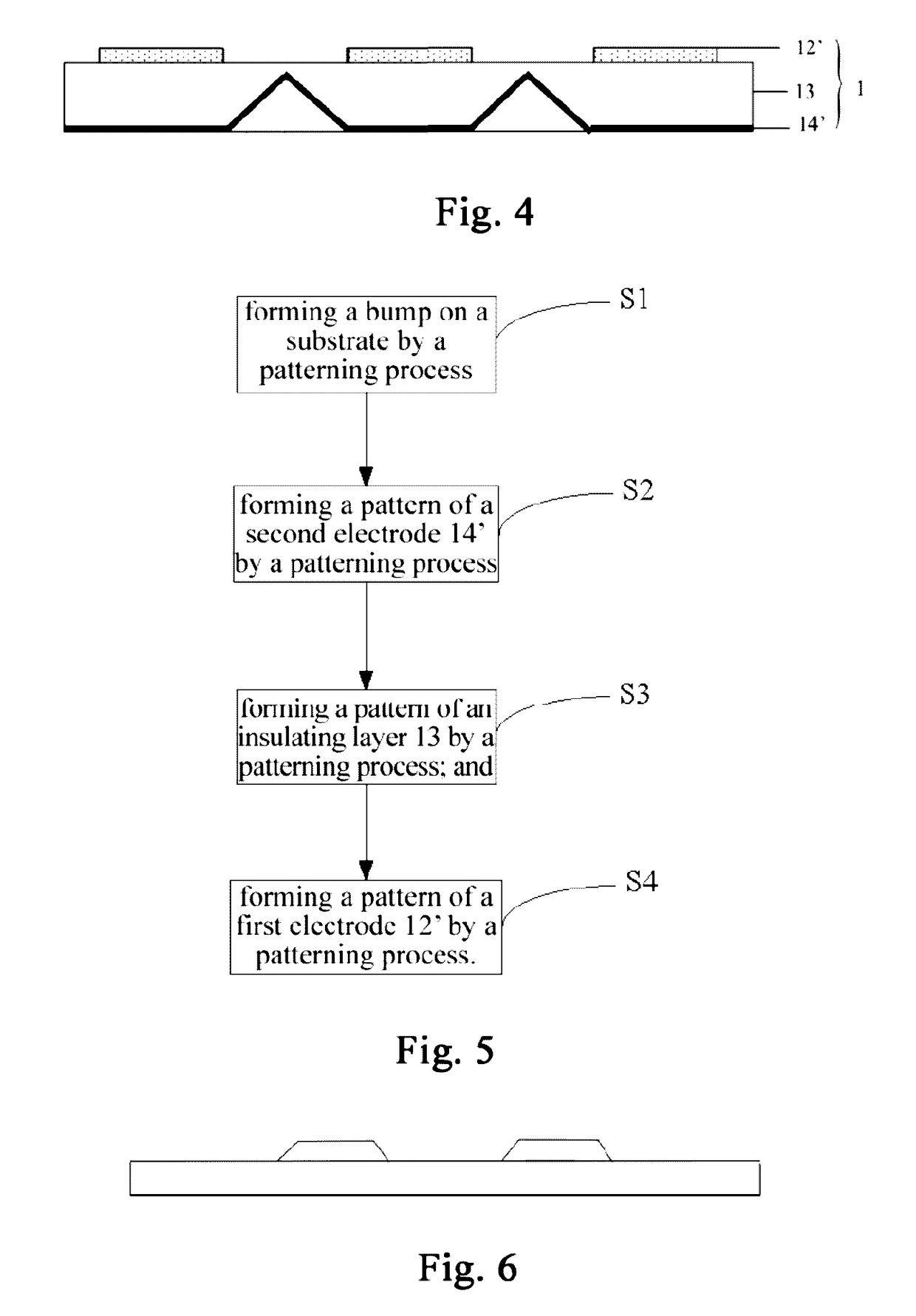

The present disclosure provides a display substrate including a plurality of first electrodes, a second electrode, and an insulating layer arranged among the first electrodes and the second electrode. The first electrodes are positioned above the second electrode. The second electrode includes a plurality of projections each, corresponding to a gap between two adjacent first electrodes and projecting towards the first electrodes.

Owner:BOE TECH GRP CO LTD

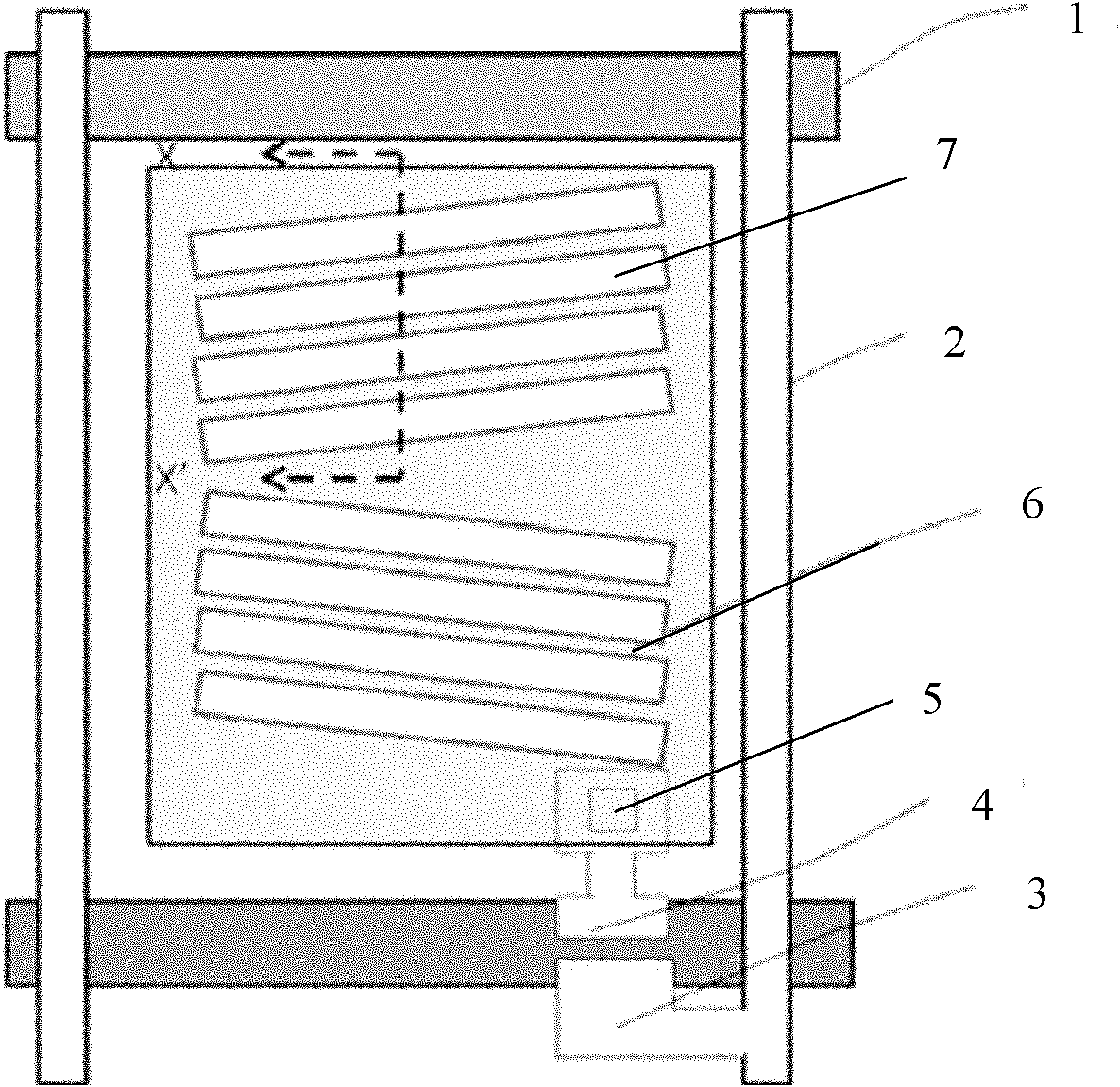

Array substrate and liquid crystal display panel

ActiveUS9041889B2Shorten the timeIncrease the aperture ratioNon-linear opticsSemiconductor devicesLiquid-crystal displayData lines

The disclosed technology discloses an array substrate and a liquid crystal display panel. The array substrate comprises: a base substrate; a gate line and a data line formed on the base substrate, the gate line and the data line defining a plurality of pixel regions; and a first electrode layer and a second electrode layer formed in each pixel region; and an insulating layer provided between the first electrode layer and the second electrode layer. The first electrode layer, the insulating layer and the second electrode layer are laminated on the base substrate in this order. The first electrode layer is provided with a plurality of first apertures therein, and the first electrode layer comprises a plurality of first electrode portions located between the plurality of first apertures.

Owner:BOE TECH GRP CO LTD

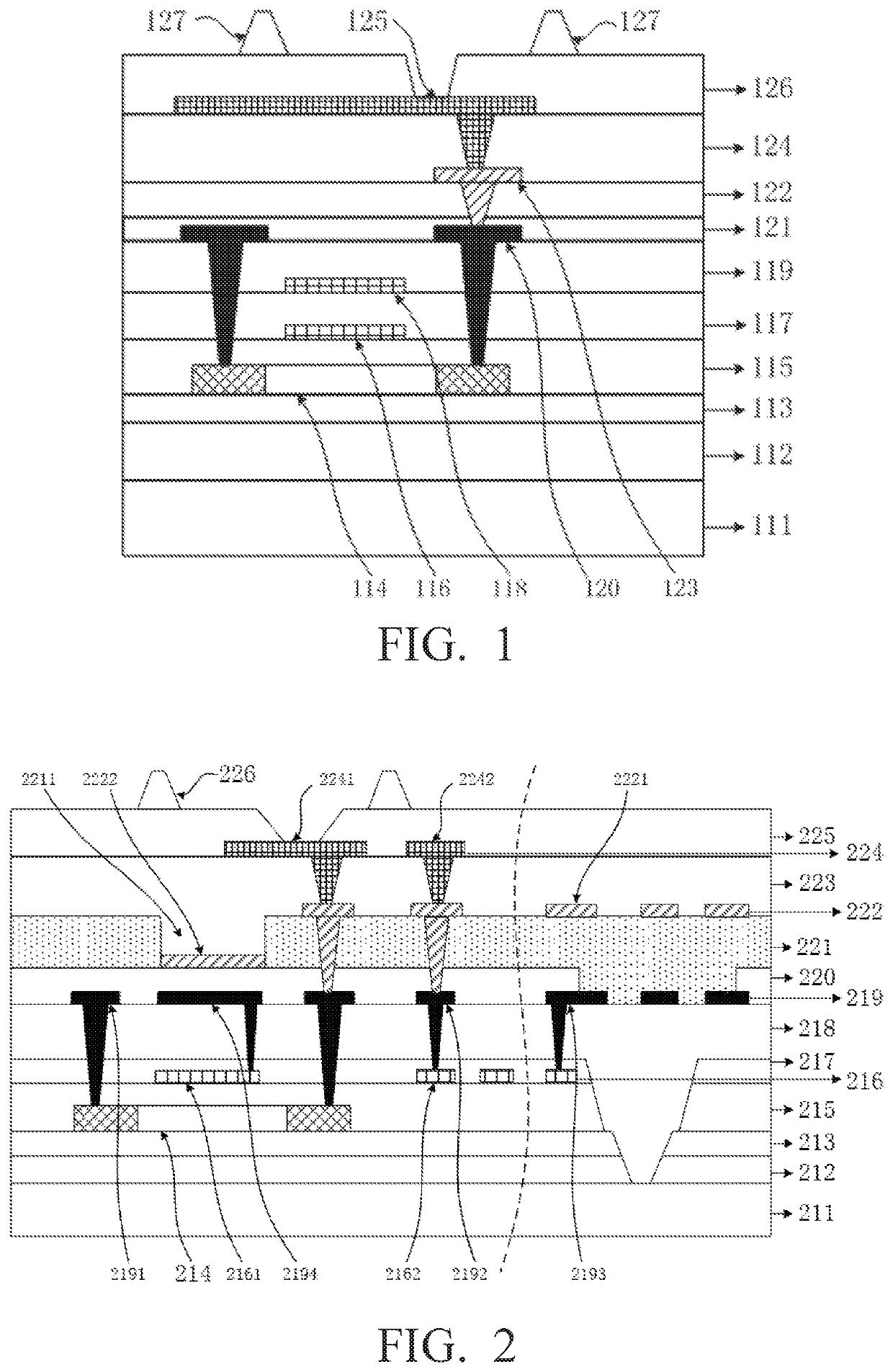

Array substrate and OLED display device

ActiveUS10916613B1Improve display uniformityLarge capacitanceSolid-state devicesSemiconductor devicesCapacitanceDisplay device

An array substrate and an OLED display device are provided. A trace system of the array substrate is designed in a structure with three layers of metal. By providing one layer of inorganic insulation film and one layer of organic insulation film between two layers of metal, a coupling effect between two layers of trace can be reduced. By exposing all or part of an organic insulation film in a region, which will form a second electrode plate of a storage capacitor, a storage capacitor with larger capacitance can be formed. By forming a third metal layer as a mesh structure, it is possible to reduce IR drop without increasing mask and improve display uniformity of the display device.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

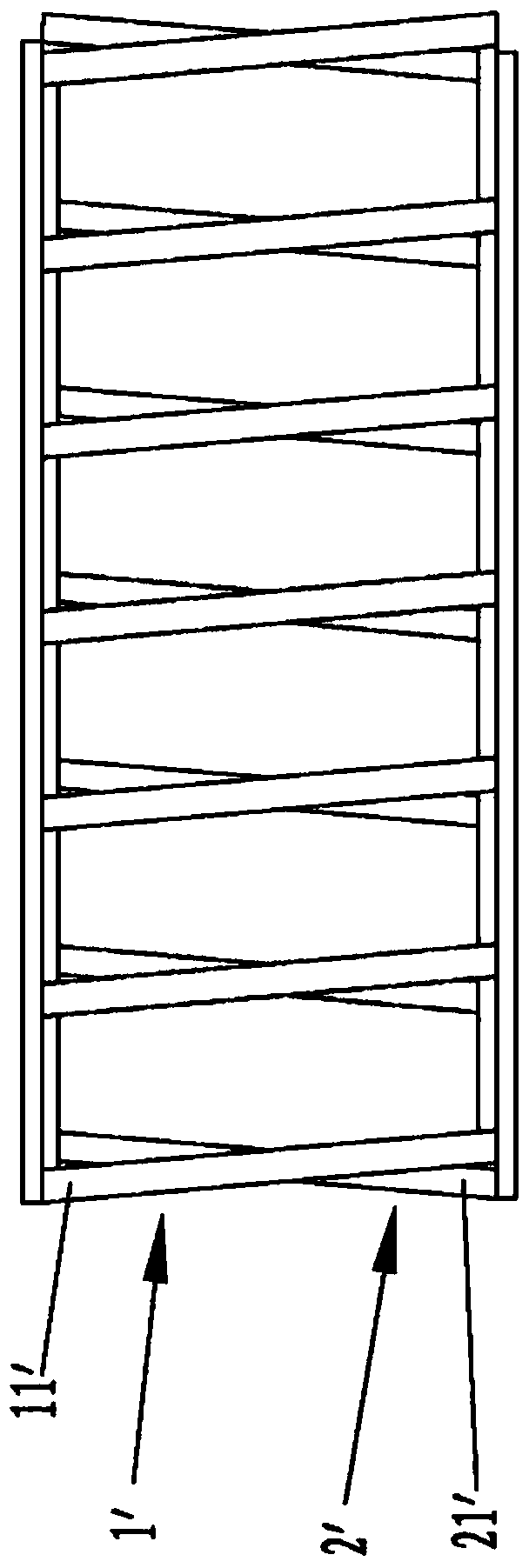

Array substrate and liquid crystal display panel

ActiveUS20130162936A1Shorten the timeIncrease the aperture ratioNon-linear opticsSemiconductor devicesLiquid-crystal displayData lines

The disclosed technology discloses an array substrate and a liquid crystal display panel. The array substrate comprises: a base substrate; a gate line and a data line formed on the base substrate, the gate line and the data line defining a plurality of pixel regions; and a first electrode layer and a second electrode layer formed in each pixel region; and an insulating layer provided between the first electrode layer and the second electrode layer. The first electrode layer, the insulating layer and the second electrode layer are laminated on the base substrate in this order. The first electrode layer is provided with a plurality of first apertures therein, and the first electrode layer comprises a plurality of first electrode portions located between the plurality of first apertures.

Owner:BOE TECH GRP CO LTD

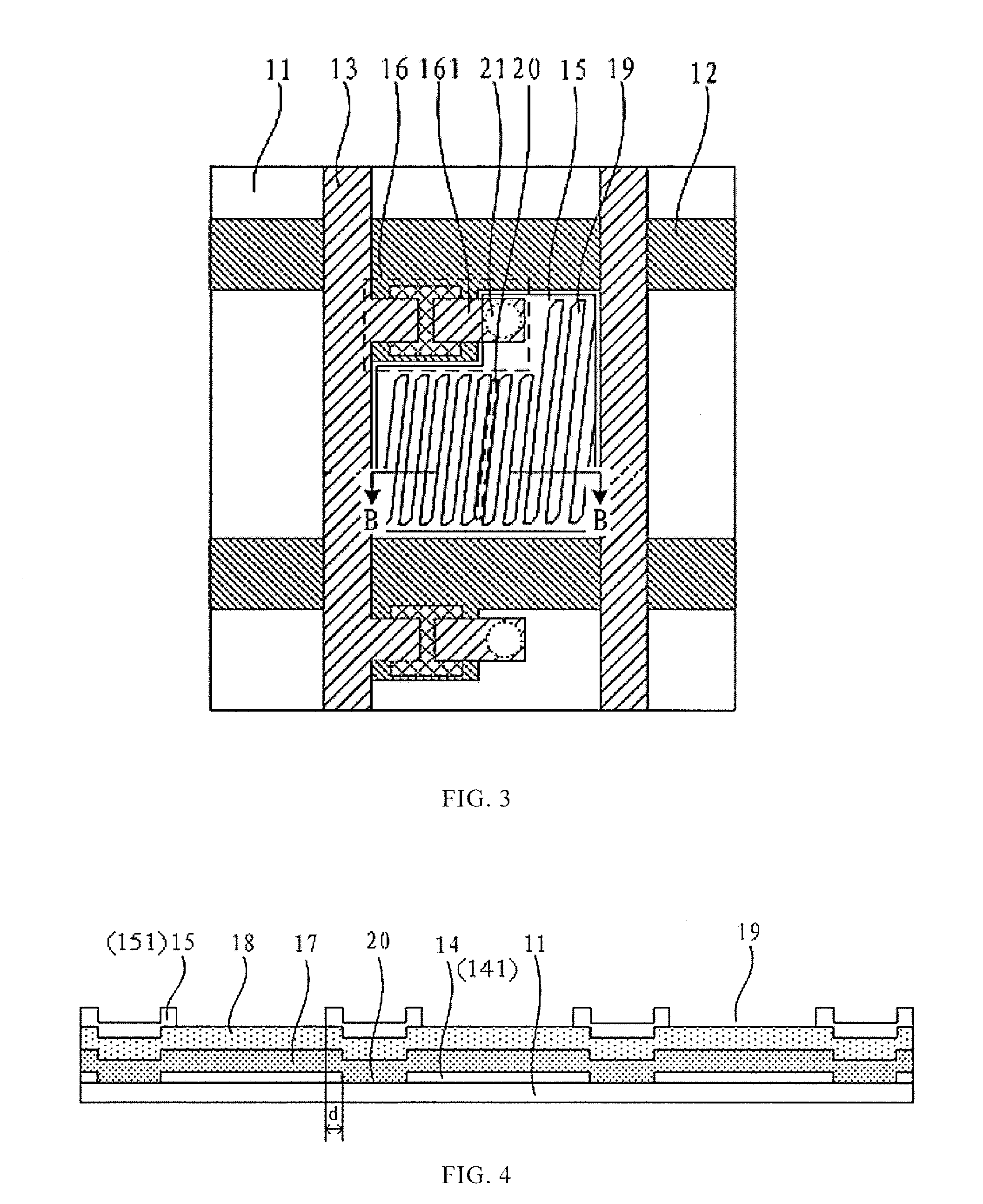

Array substrate, manufacturing method thereof, and display device

ActiveCN106783895BReduce brightness differenceWeaken the effect of quality effectsSolid-state devicesSemiconductor/solid-state device manufacturingComputer hardwareDisplay device

The invention discloses an array substrate and a manufacturing method of the array substrate as well as a display device. The array substrate comprises a pixel array composed of pixel units which are arrayed in a matrix manner, and a plurality of grid electrode wires which extend along the transverse direction of the pixel array; a routing region is arranged between every two adjacent rows of the pixel units; types of each routing region comprise a first routing region, a second routing region and a third routing region; each routing region is provided with a data line; at most one grid electrode output line is arranged in each second routing region, and is connected with the corresponding grid electrode line; each third routing region is provided with two data lines located on different thin film layers; the distance between the two data lines of each third routing region along the transverse direction of the pixel units is less than or equal to 0. According to the array substrate disclosed by the invention, the distance between the grid electrode output line and each data line can be increased, voltage coupling on the data lines is reduced, and the bright spot problem is solved; meanwhile, the distance between the two data lines of each third routing region is reduced, and influences on the picture quality effect can be weakened.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

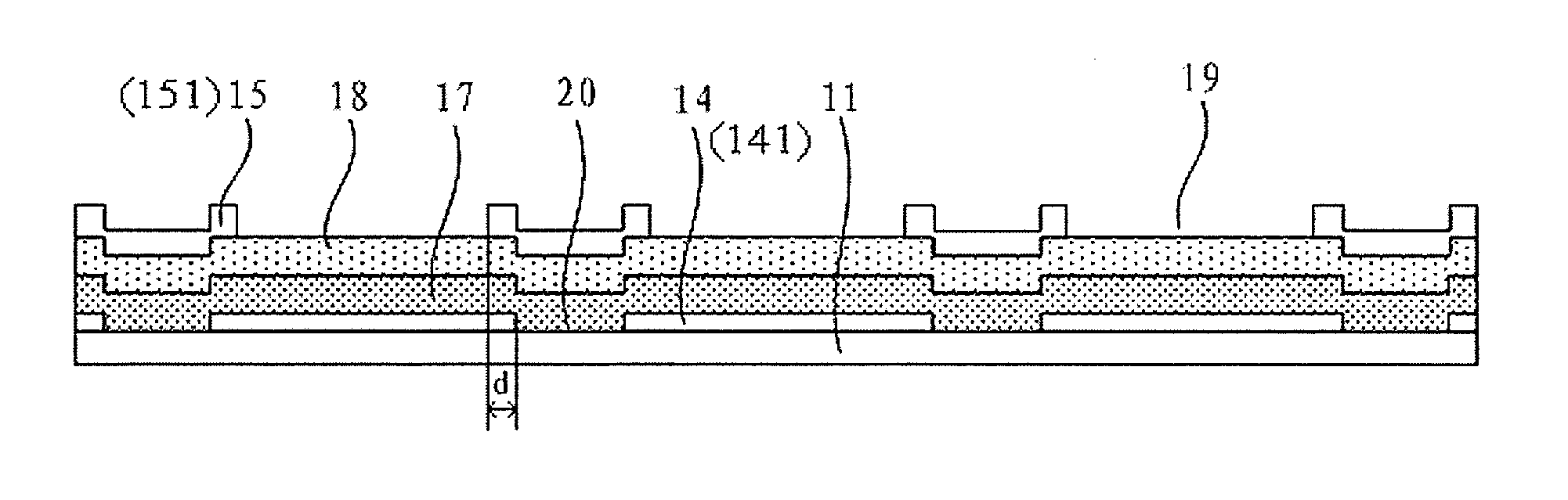

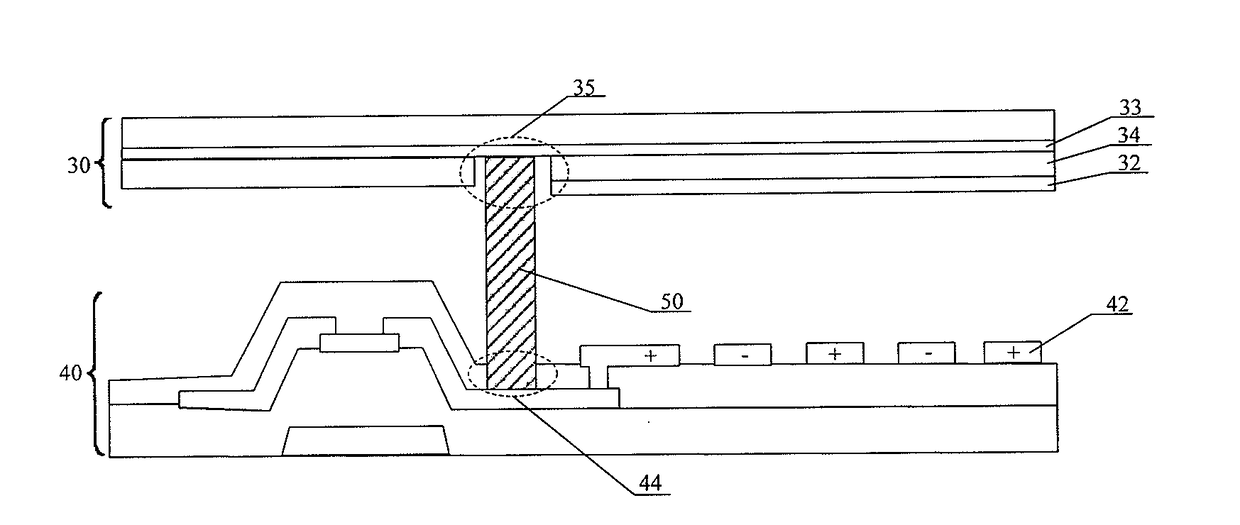

Display device

ActiveUS9804453B2Prevent aperture ratioIncrease storage capacityNon-linear opticsElectricityInsulation layer

The embodiment of the present invention discloses a display device, which relates to the field of display, may realize low-frequency (low-standing-wave) driving and may prevent the aperture ratio from being reduced as a result of ensuring the charge rate during high-frequency driving. The display device provided by the present invention comprises a first substrate and a second substrate which are assembled with each other to form a cell, wherein the first substrate comprises a first electrode layer, the second substrate comprises a second electrode layer, the first substrate further comprises a third electrode layer arranged on one side, far from the second substrate, of the first electrode layer, and an insulation layer is arranged between the third electrode layer; and the first electrode layer, and the third electrode layer is electrically connected with the second electrode layer. The display device is suitable for being driven at low frequency.

Owner:BOE TECH GRP CO LTD

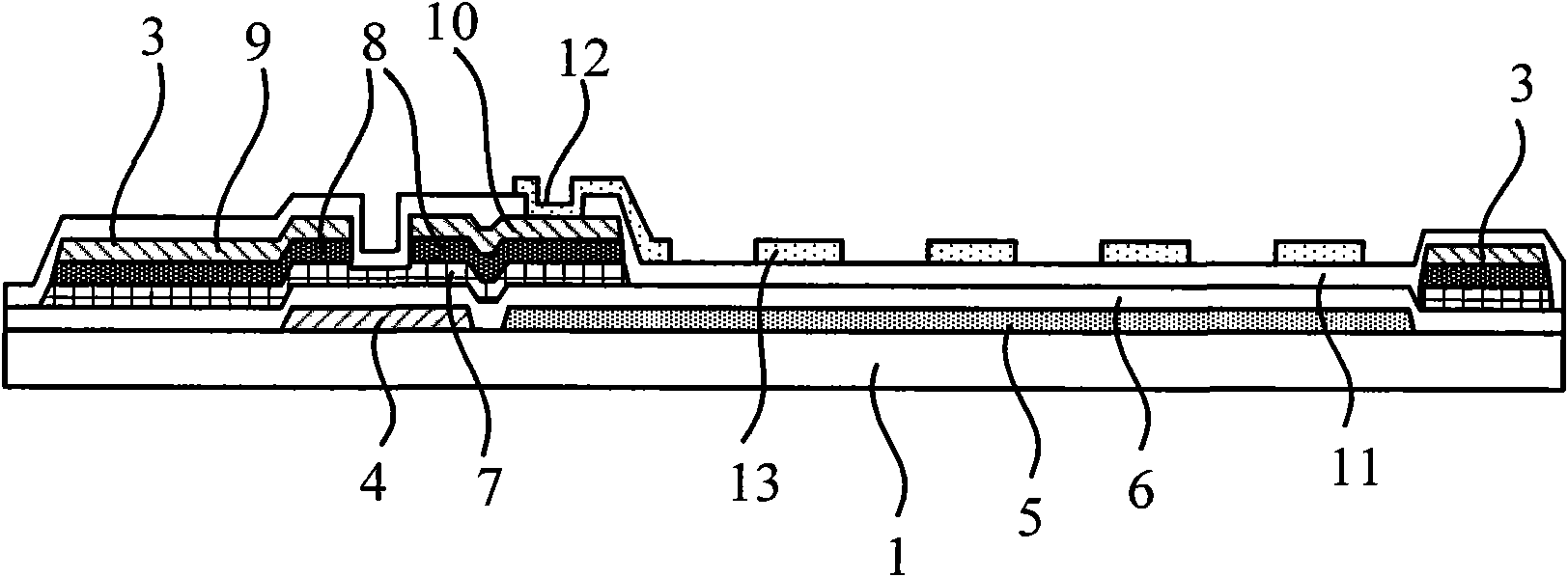

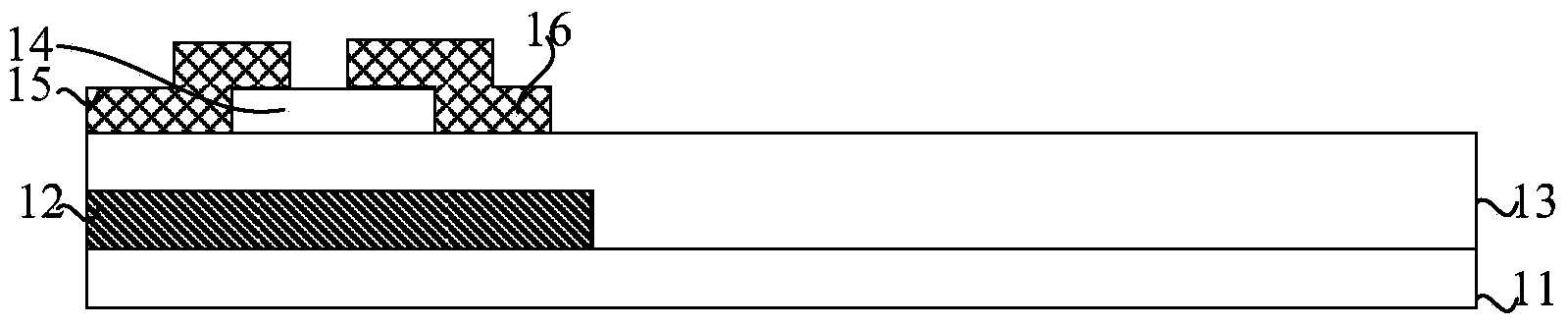

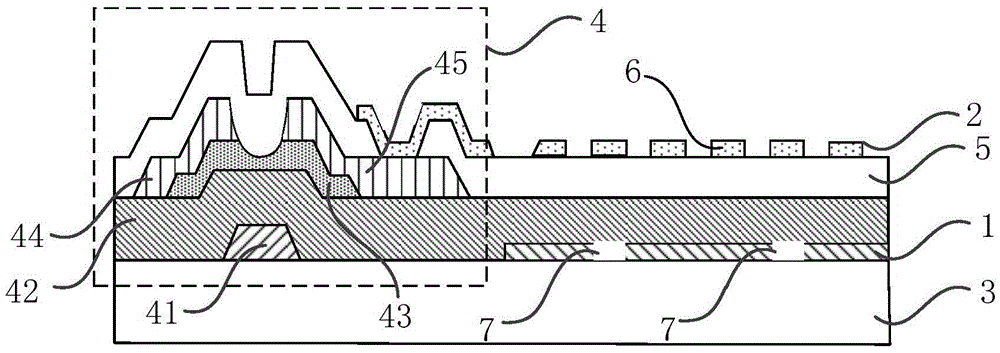

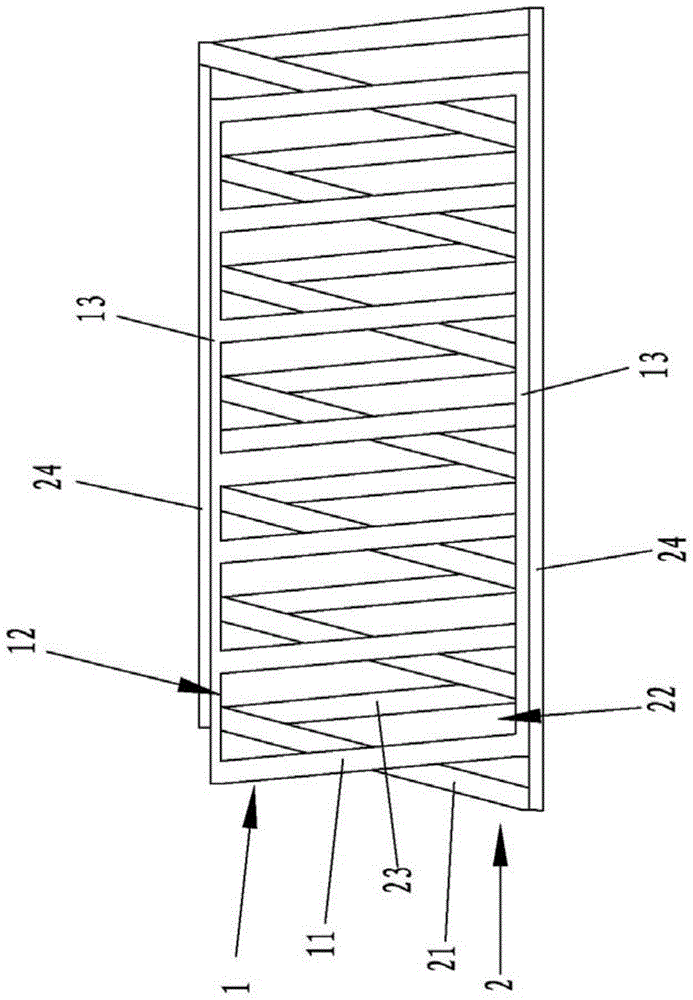

Array substrate, display device, and method for manufacturing the array substrate

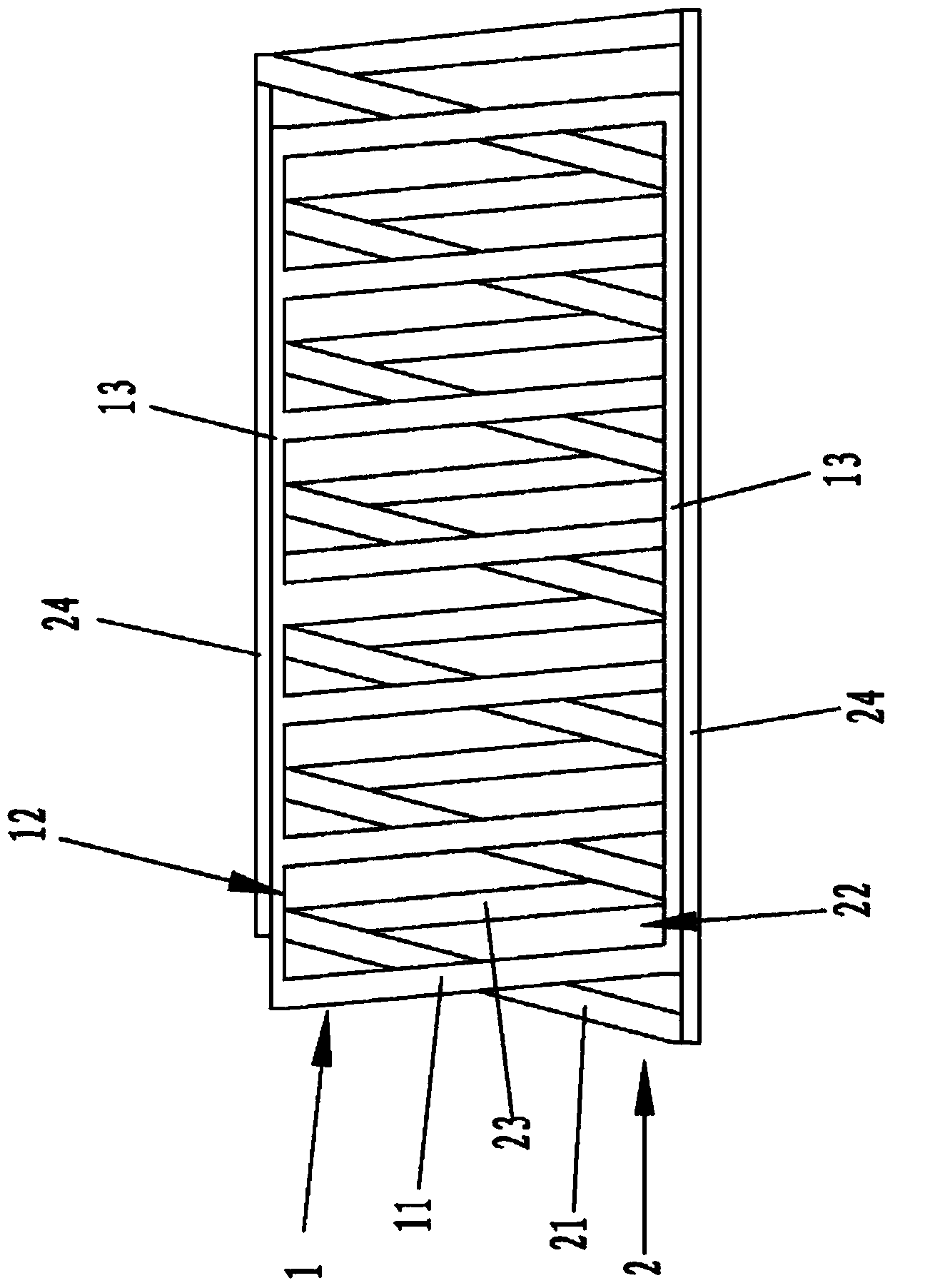

ActiveCN103278986BReduce line widthShorten charging timeSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerOptoelectronics

An array substrate, a display apparatus, and a manufacturing method for the array substrate are provided. The array substrate comprises: an underlayer substrate (1); scanning lines (12) and data lines (11) that cross each other and are located on the underlayer substrate (1), the scanning lines (12) and the data lines (11) defining multiple pixel areas; multiple thin film transistors, arranged in an array and respectively located in each pixel area; pixel electrodes (10), located in the pixel areas, and a common electrode (3); an insulation layer (13), located between the common electrode (3) and the scanning lines (12), an projection of the scanning lines (12) on the underlayer substrate (1) at least partially overlapping an projection of a common electrode line (2) on the underlayer substrate (1).

Owner:BOE TECH GRP CO LTD +1

Array substrate, manufacturing method thereof, and wide viewing angle liquid crystal display

ActiveCN101847641BIncreasing the thicknessReduce storage capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceLiquid-crystal display

The invention relates to an array substrate, a manufacturing method thereof and a liquid crystal display with a wide viewing angle. The array substrate includes a base substrate and a plurality of pixel regions, and also includes an organic transparent insulating layer formed between the passivation layer and the pixel electrodes. The manufacturing method includes: forming a common electrode, a common electrode line, and a pattern of a thin film transistor switch on a base substrate; depositing a passivation layer; forming an organic transparent insulating layer on the passivation layer, and forming an organic layer via hole and a passivation layer A via hole: a pattern of the pixel electrode is formed on the organic transparent insulating layer, the pattern of the pixel electrode has a plurality of gaps, and the pixel electrode is connected to the thin film transistor switch through the organic layer via hole and the passivation layer via hole. The liquid crystal display of the present invention includes the array substrate of the present invention. The invention adopts the technical means of adding an organic transparent insulating layer between the pixel electrode and the passivation layer, increases the thickness of the film layer between the pixel electrode and the common electrode, can effectively reduce the storage capacitance and reduce afterimages.

Owner:BOE TECH GRP CO LTD

Array substrate of TFT-LCD (Thin Film Transistor-Liquid Crystal Display) and manufacturing method thereof

ActiveCN102566156BReduce overlap areaIncrease chromatic aberrationSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceLiquid-crystal display

The present disclosure provides an array substrate for a thin film transistor liquid crystal display (TFT-LCD), comprising: a base substrate having gate lines and data lines intersecting with each other to define sub-pixel units, each comprising a thin film transistor, a common electrode, a first pixel region and a second pixel region, wherein the first pixel region includes a first pixel electrode connected to the common electrode and a second pixel electrode connected to a drain electrode of the thin film transistor, and the first pixel electrode is on a same layer as and insulated from the second pixel electrode, and wherein the second pixel region includes a third pixel electrode connected to the common electrode and a fourth pixel electrode connected to the drain electrode, which are on a same layer and spaced apart from each other by a second local opening.

Owner:BOE TECH GRP CO LTD +1

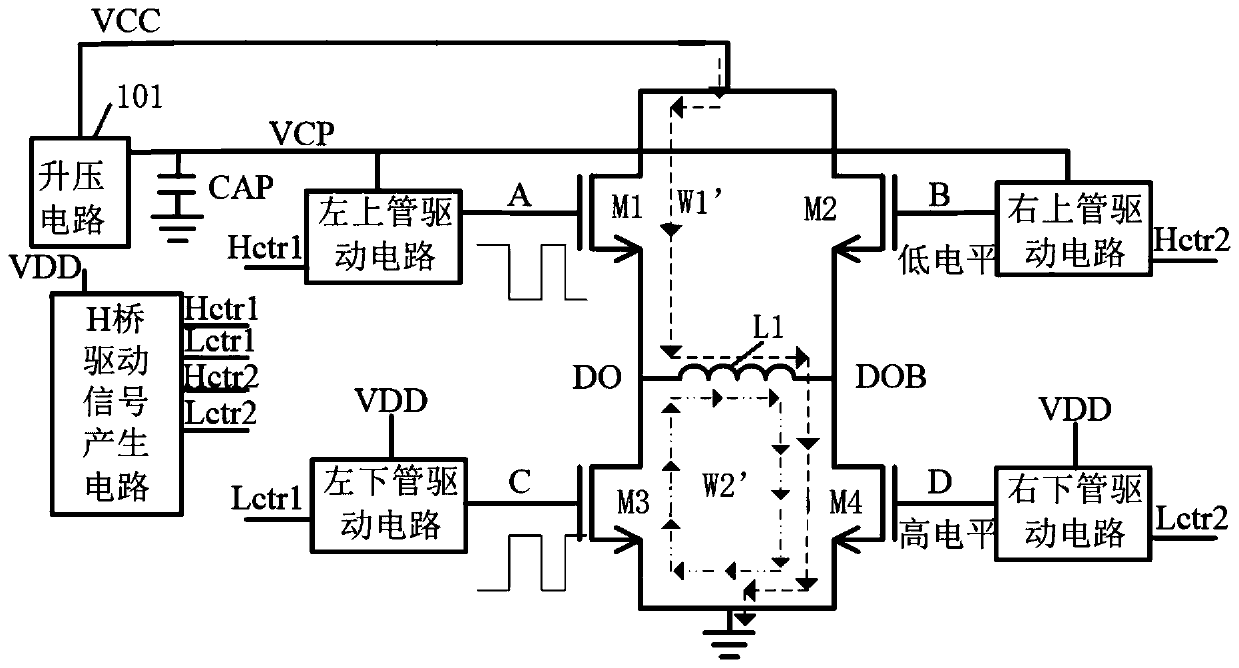

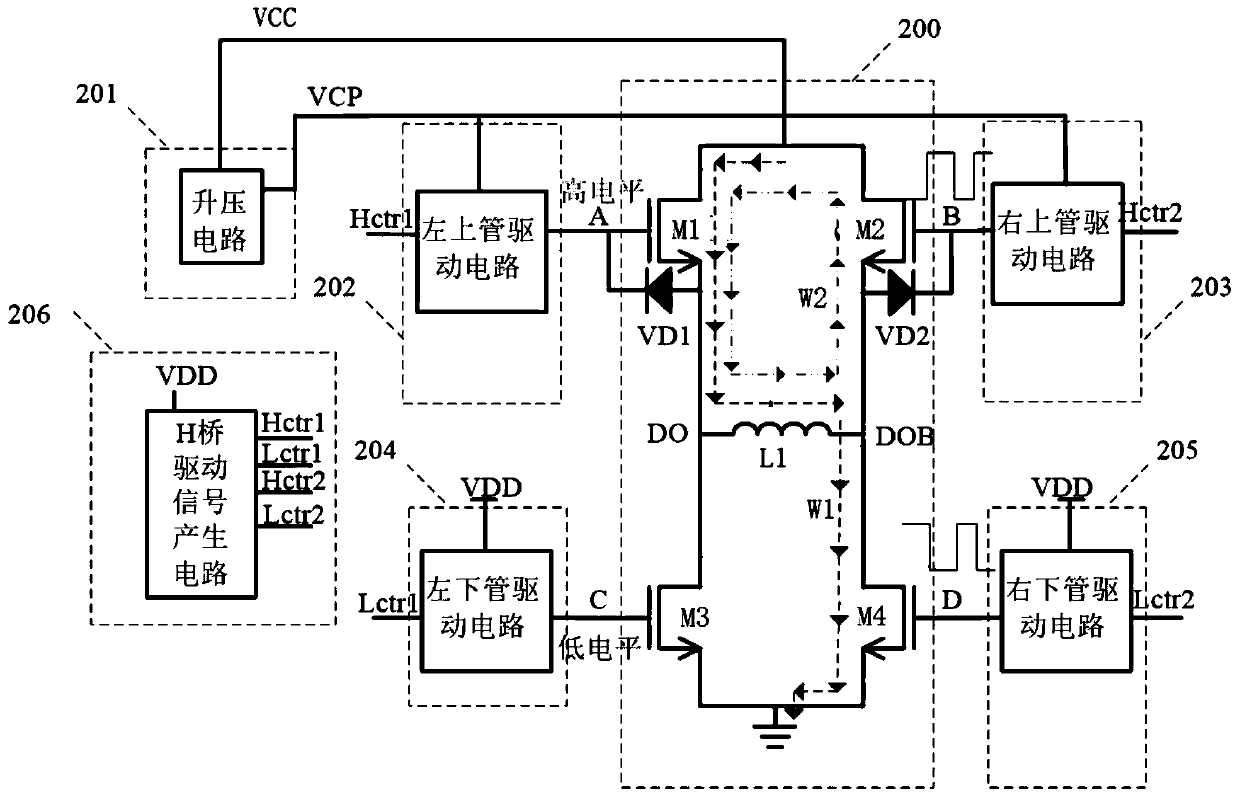

PWM modulation assembly of H-bridge drive circuit

PendingCN111490706AReduce storage capacitanceReduce difficultyField or armature current controlParasitic capacitanceHemt circuits

The invention provides a PWM modulation assembly of an H-bridge drive circuit. Four switch tubes of the H-bridge drive circuit are NMOS tubes. Gates of the switch tubes are respectively connected withthe drive circuit; the input end of the drive circuit is connected with the signal output end of an H-bridge drive signal generation circuit; the H-bridge drive signal generation circuit continuouslyoutputs a conduction signal to the drive circuit corresponding to an upper tube on one side, continuously outputs a cut-off signal to the drive circuit corresponding to a lower tube on the other side, and alternately outputs cut-off and conduction signals to the drive circuits corresponding to an upper tube and a lower tube on the other side. According to the modulation assembly, the upper tube on the first side is always in a conduction state, and large parasitic capacitance exists between the grid electrode of the upper tube on the first side and the power supply voltage, so that the storage capacitance of a boost circuit is greatly reduced; and the upper tube on the first side is conducted, and the lower tube on the first side is cut off, so that the output end of the H-bridge drive circuit cannot generate negative voltage, and the circuit works more reliably than before.

Owner:SHANGHAI ORIENT CHIP TECH CO LTD +1

A cmos image sensor

ActiveCN104269418BSpeed up the flowReduce storage capacitanceRadiation controlled devicesCMOSSemiconductor

The embodiment of the invention provides a CMOS image sensor and relates to the technical field of semiconductors. The CMOS image sensor can achieve high-sensitivity and high-speed responses. Each pixel unit of the CMOS image sensor comprises a P type semiconductor substrate, a first N type ion layer on the upper portion of the P type semiconductor substrate, a P trap surrounding the first N type ion layer, a second N type ion layer, a third N type ion layer, a first P type ion layer and a second P type ion layer, wherein the second N type ion layer, the third N type ion layer, the first P type ion layer and the second P type ion layer are arranged on the upper portion of the first N type ion layer; the first P type ion layer and the second P type ion layer are spaced by the second N type ion layer, the second N type ion layer and the third N type ion layer are spaced by the second P type ion layer, the doping concentration of the second N type ion layer and the doping concentration of the third N type ion layer are larger than the doping concentration of the first N type ion layer, and the doping concentration of the first P type ion layer and the doping concentration of the second P type ion layer are between the doping concentration of the P trap and the doping concentration of the P type semiconductor substrate. The CMOS image sensor is used for sensor manufacturing.

Owner:BOE TECH GRP CO LTD

Pixel structure, array substrate and display device

InactiveCN103676353BReduce storage capacitanceImprove transmittanceNon-linear opticsCapacitanceDisplay device

The invention discloses a pixel structure, an array substrate and a display device. The pixel structure comprises a first electrode and a second electrode, wherein the first electrode comprises a plurality of first electrode parts and a plurality of first gaps located between the adjacent first electrode parts, the second electrode comprises a plurality of parallel strip-shaped second electrode parts and a plurality of second gaps located between the adjacent second electrode parts, the downward perpendicular projection of each first electrode part is overlapped with the downward perpendicular projection of each second electrode part, the second electrode comprises third electrode parts, and each second electrode part is connected with the adjacent electrode part through one third electrode part. The array substrate comprises the pixel structure. The display device comprises the array substrate. According to the technical scheme, storage capacitance is reduced, the second electrode is designed in a narrow gap patterning mode, and on the basis of reducing the storage capacitance, high transmittance and high technological yield are maintained.

Owner:BOE TECH GRP CO LTD

Display panels and display devices

ActiveCN111999946BWill not affect the normal displayImprove charging effectNon-linear opticsCapacitanceScan line

The invention discloses a display panel and a display device, which belong to the technical field of display. The display panel includes scanning lines, data lines, pixel electrodes and a black matrix. The black matrix includes an externally expanded black matrix. The first black matrix is connected, the scan line and the data line intersect to define the sub-pixel, the pixel electrode is arranged in the sub-pixel, the pixel electrode includes a first part and a second part that are connected to each other, and the first part includes a plurality of parts extending along the third direction. The first strip electrodes, the plurality of first strip electrodes are not connected, the first strip electrodes include the first subtype strip electrodes and the second subtype strip electrodes, the first subtype strip electrodes and the second subtype strip electrodes One of the strip-like electrodes overlaps with the externally expanded black matrix, and the other does not overlap with the expanded black matrix. The invention reduces the storage capacitance between the pixel electrode and the common electrode, improves the charging capability of the pixel, and improves the display effect.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

OLED array substrate and OLED display device

ActiveUS11195897B2High densityFacilitate designing a circuitSolid-state devicesSemiconductor devicesDisplay deviceHemt circuits

An organic light-emitting diode (OLED) array substrate and an OLED display device are provided. The OLED array substrate includes a plurality of driving circuits of a plurality of sub-pixels using a mirror symmetrical structure, and a plurality of reset signal lines and a plurality of power signal lines extending along a same direction. By sharing each of the reset signal lines and each of a plurality of first vias, and sharing each of the power signal lines and each of a plurality of second vias, about half of lines of power signal lines, reset signal lines, and vias are saved. Therefore, room for increasing pixels per inch (PPI) is provided, facilitating realizing high PPI panel designs.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD