Memory and memorizing method thereof

A memory, phase change memory technology, applied in static memory, instruments, etc., can solve the problems of low code density and lack of testing flexibility for customers, and achieve the effect of high customer code density, providing quality and stability, and flexible testing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described in detail in conjunction with the following specific embodiments and accompanying drawings. The process, conditions, experimental methods, etc. for implementing the present invention, except for the content specifically mentioned below, are common knowledge and common knowledge in this field, and the present invention has no special limitation content.

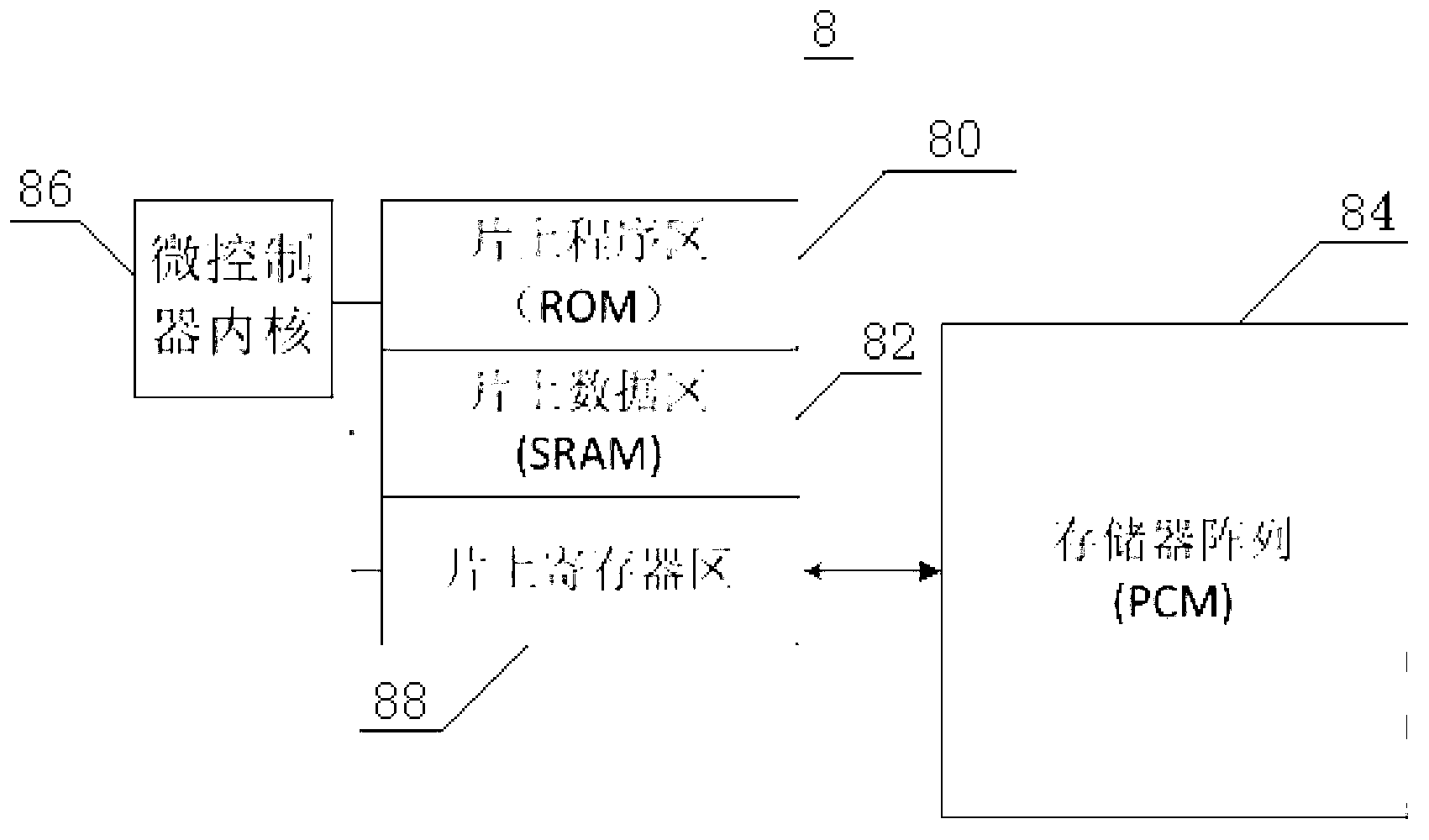

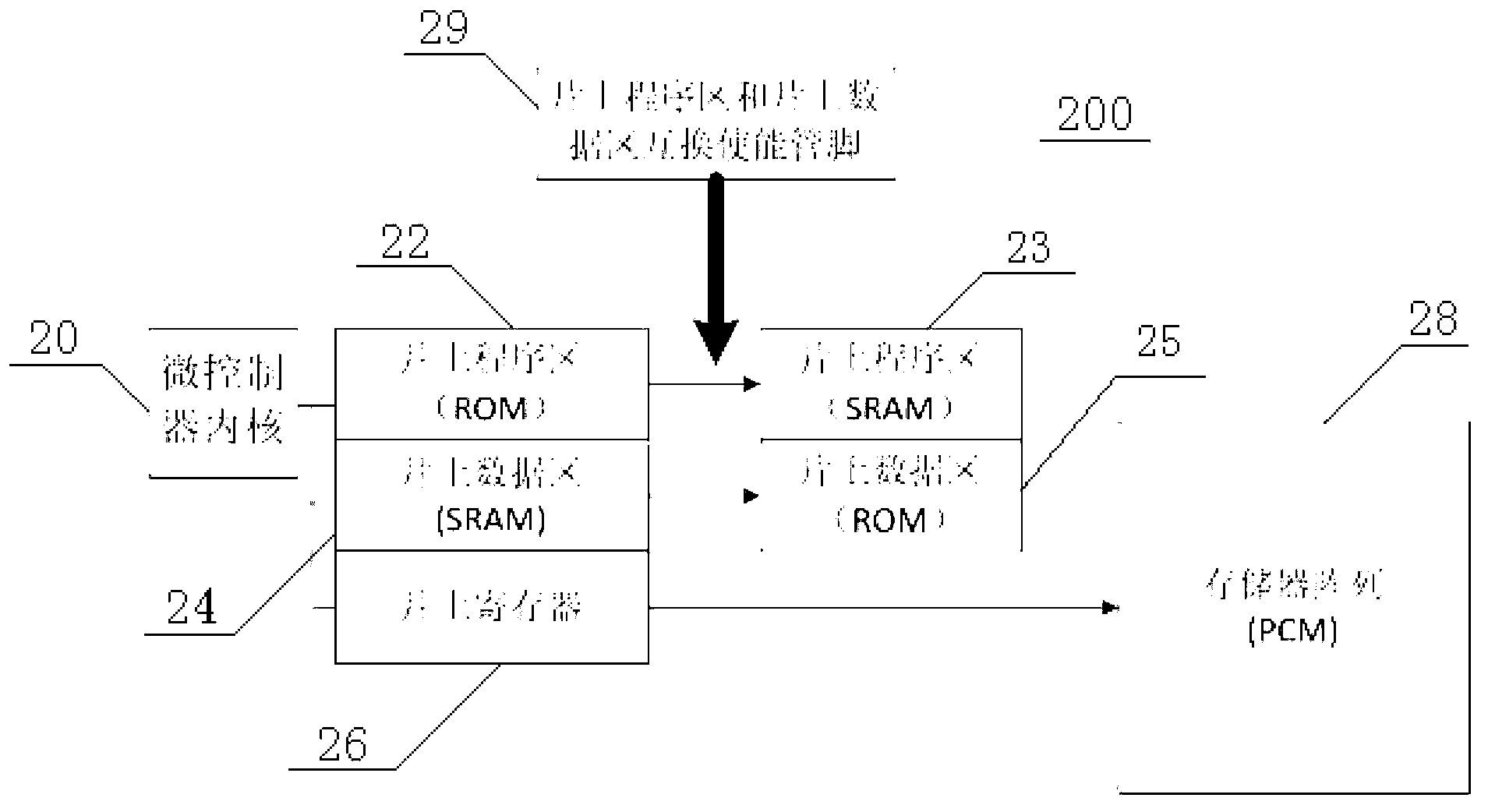

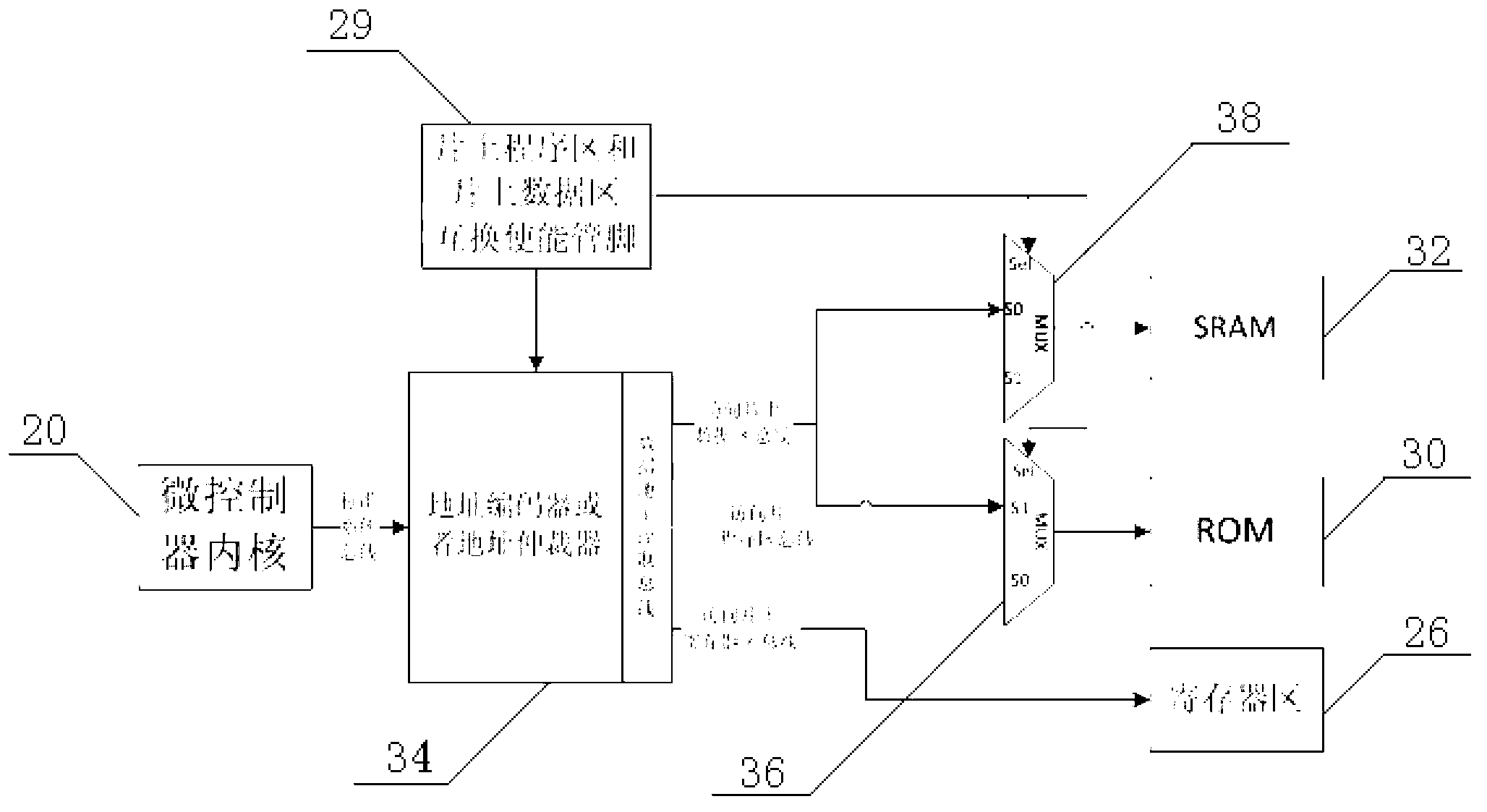

[0029] In the stage of large-scale testing and verification of chips, such as memory, the test factory will download a large number of test codes to the on-chip program area of the chip, and the test code will be executed by the chip core, and the memory array will be directly accessed through the register output to achieve the purpose of testing . The main test contents include Read Window Budget, aging test of phase change memory area, and data retention test. Most of the existing on-chip program areas are ROM or PCM in material selection, but these two configurations...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More