Process for producing semiconductor

A manufacturing process and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as poor quality, reduced electrical quality of semiconductor structures, and uneven surfaces

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

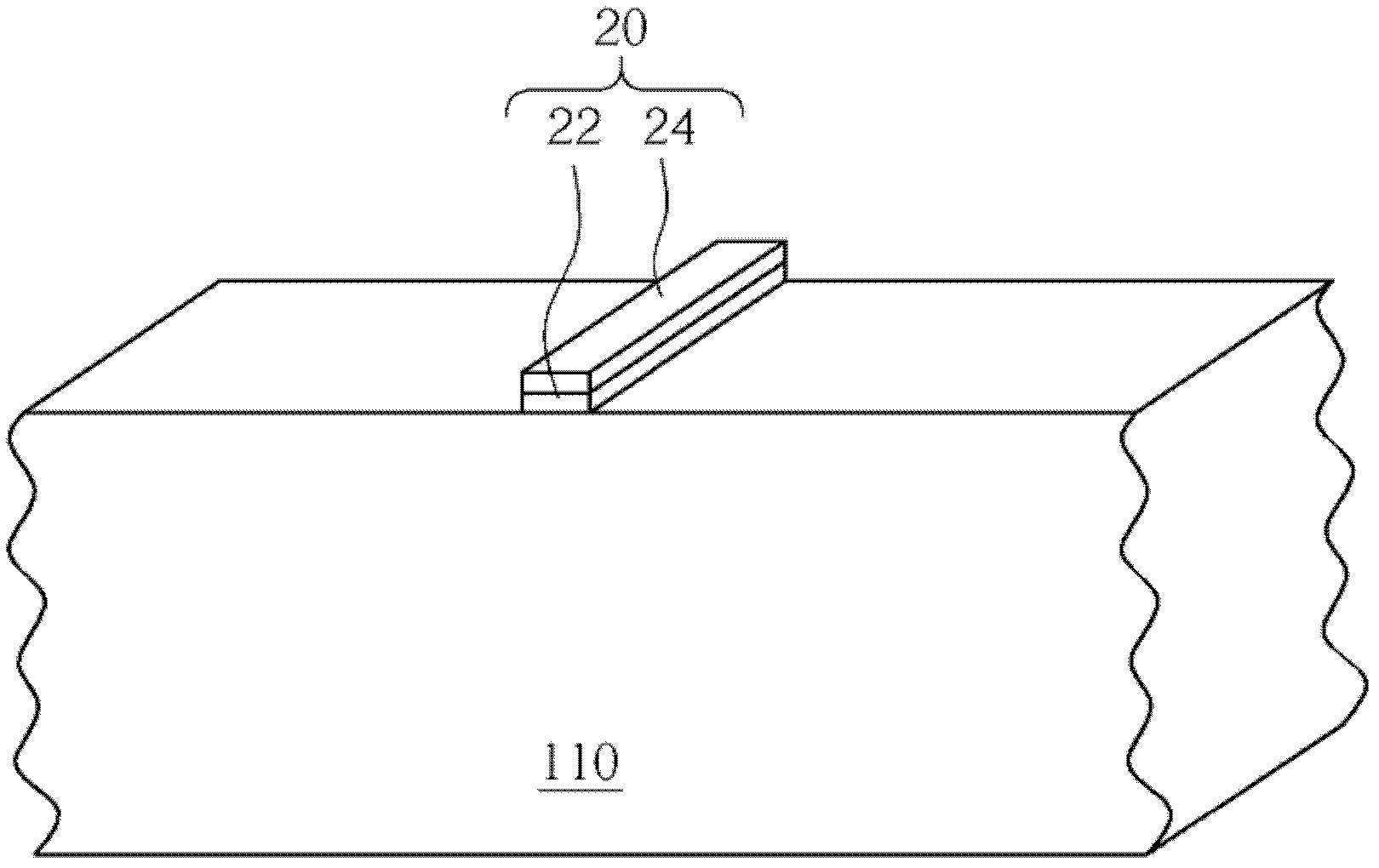

[0030] Figure 1-Figure 10 A schematic cross-sectional view of a semiconductor fabrication process according to an embodiment of the present invention is shown. Such as figure 1 As shown, a base 110 is provided, and the base 110 in this embodiment is a monolithic base. Certainly, the substrate 110 may include a silicon substrate, a silicon-containing substrate, a group III-V silicon-on-silicon substrate (such as GaN-on-silicon), a graphene-on-silicon substrate (graphene-on-silicon), or a silicon-on-insulator substrate. and other semiconductor substrates. Next, a mask layer 20 is formed on the substrate 110 , wherein the mask layer 20 may include a pad oxide layer 22 and a nitride layer 24 on the pad oxide layer 22 . Then, an etching and photolithography process is performed to pattern the mask layer 20 and expose part of the substrate 110 .

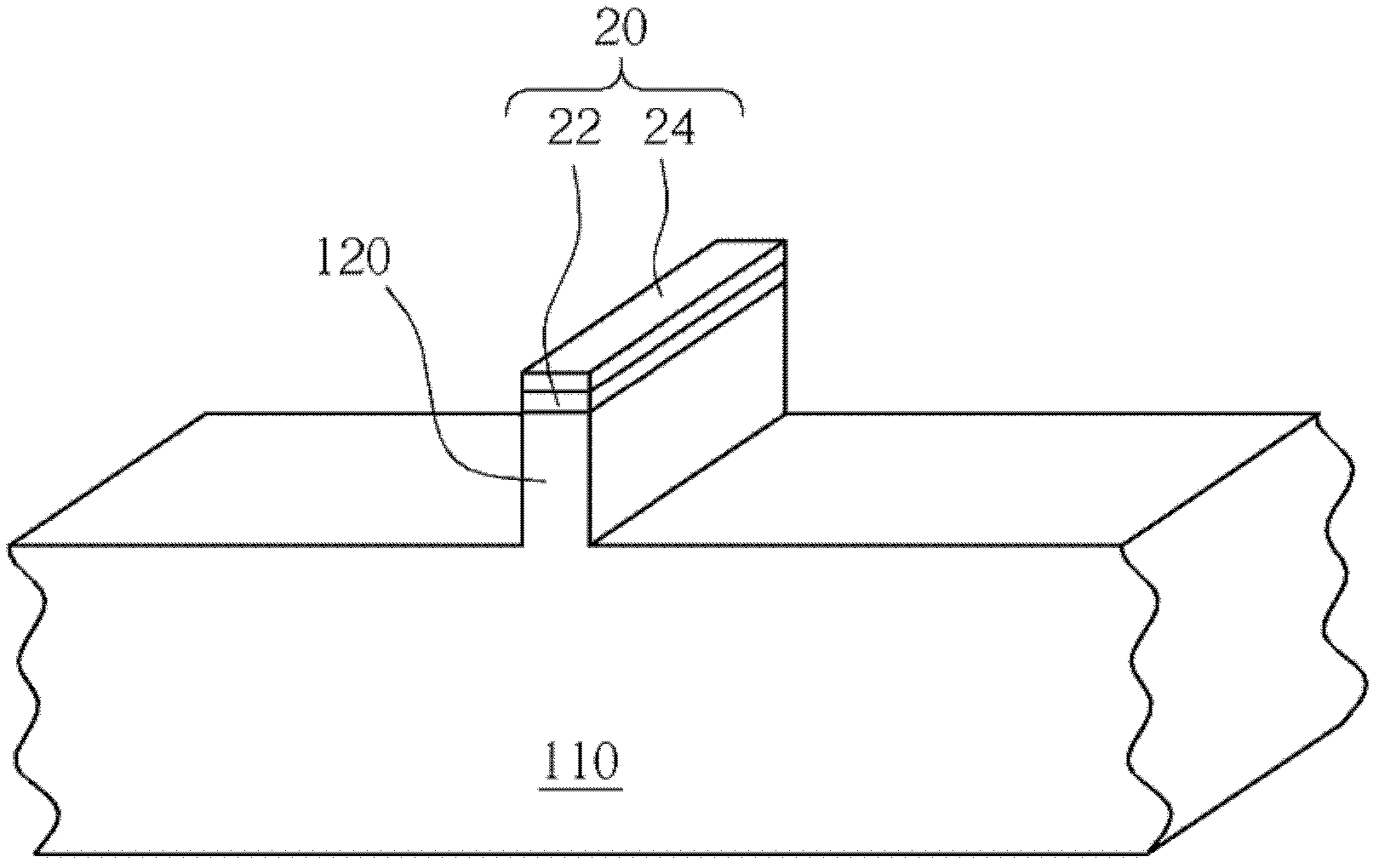

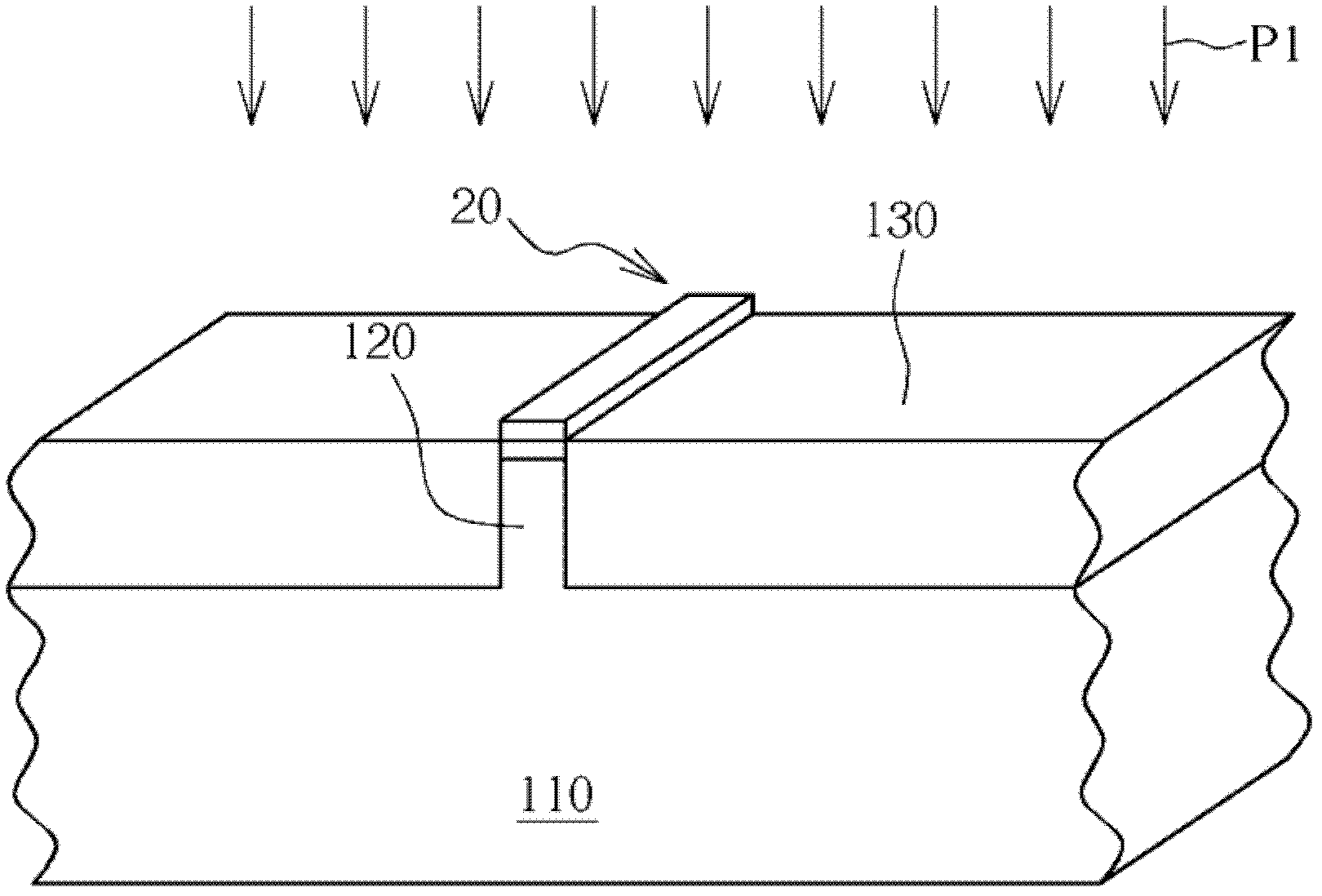

[0031] Such as figure 2 As shown, the substrate 110 is etched using the mask layer 20 as a hard mask to form a fin structure 120 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More