Test structure used for evaluating organic photo conductor (OPC) effects

A technology for testing structures and devices, applied to electrical components, electrical solid devices, circuits, etc., can solve problems that cannot be directly reflected on the influence of filleting effects on device characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

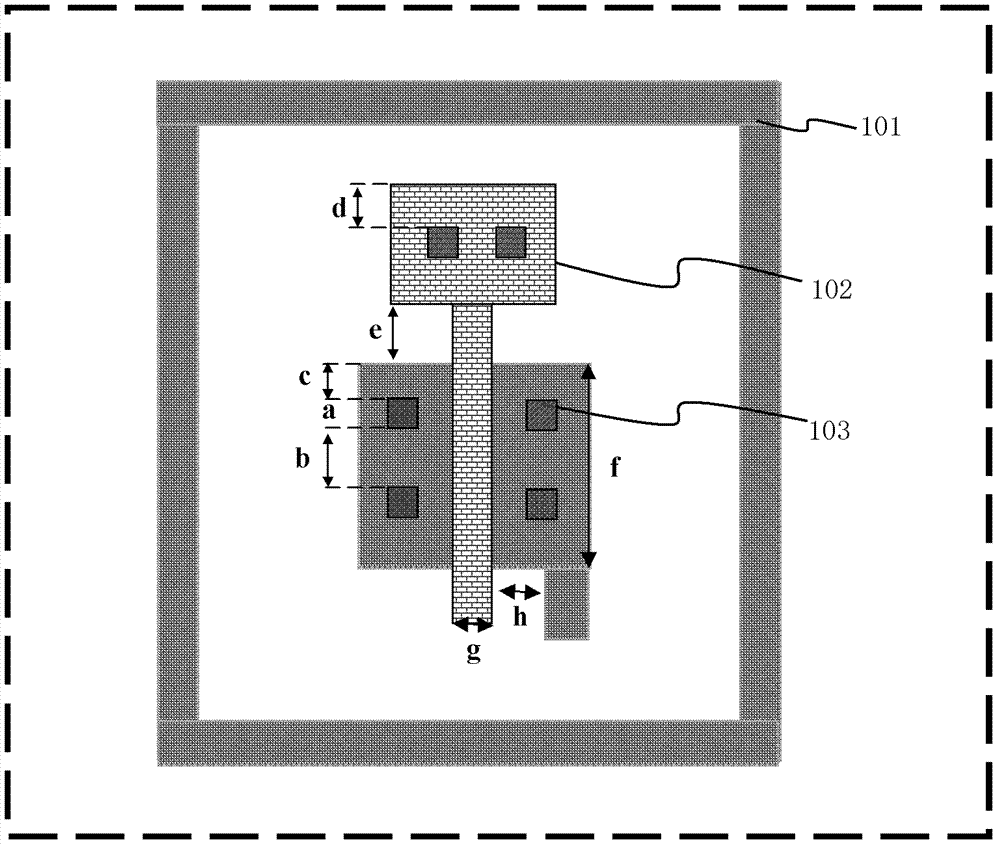

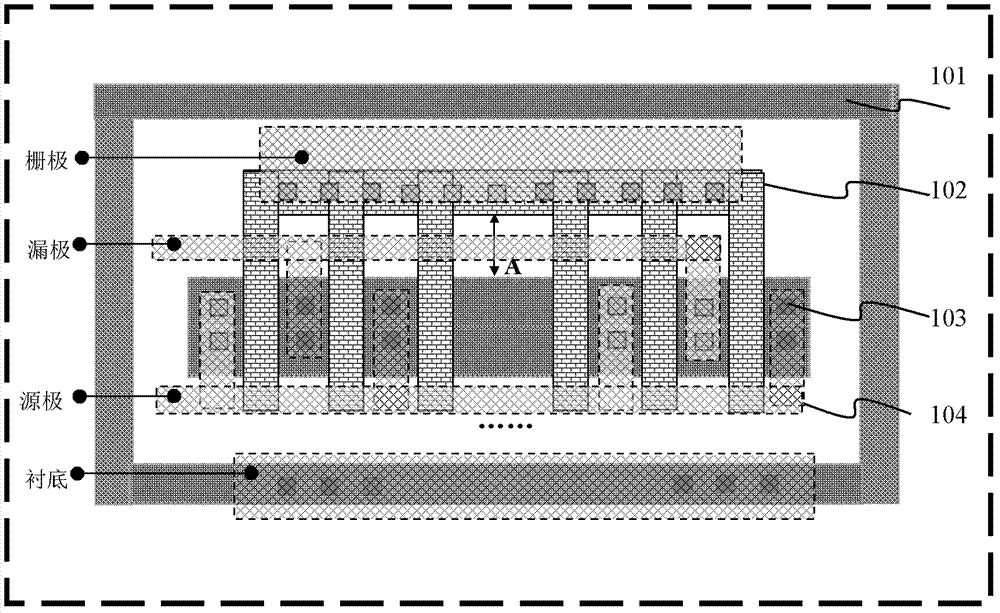

[0046] The first embodiment of the present invention is a test structure for evaluating the effect of CMOS polysilicon layer OPC (Optical Proximity Correction), the test structure includes 2*N CMOS devices (NMOS or PMOS), and N is greater than or equal to 3 According to the set size, it is produced by a corresponding set of CMOS semiconductor process including OPC process. The size is set based on the corresponding design rules of this set of CMOS semiconductor process. The specific value of the size is different due to different sets of CMOS semiconductor process. same;

[0047] N CMOS devices in the 2*N CMOS devices are used as an inspection group;

[0048] N CMOS devices in the 2*N CMOS devices are used as a reference group;

[0049] For the CMOS devices in the inspection group, the distance between the L-shaped polysilicon 102 and the single crystal silicon active region 101 (such as figure 2 A) marked above is equal to e;

[0050] For the CMOS devices in the reference...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More