Method of improving planarization of surface of shallow trench isolation silicon oxide film

A technology for surface planarization and silicon oxide film, which is used in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., and can solve the limitations of process flexibility, limited help for surface planarization of silicon oxide film, and poor planarization effect, etc. problems to achieve the effect of increasing flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

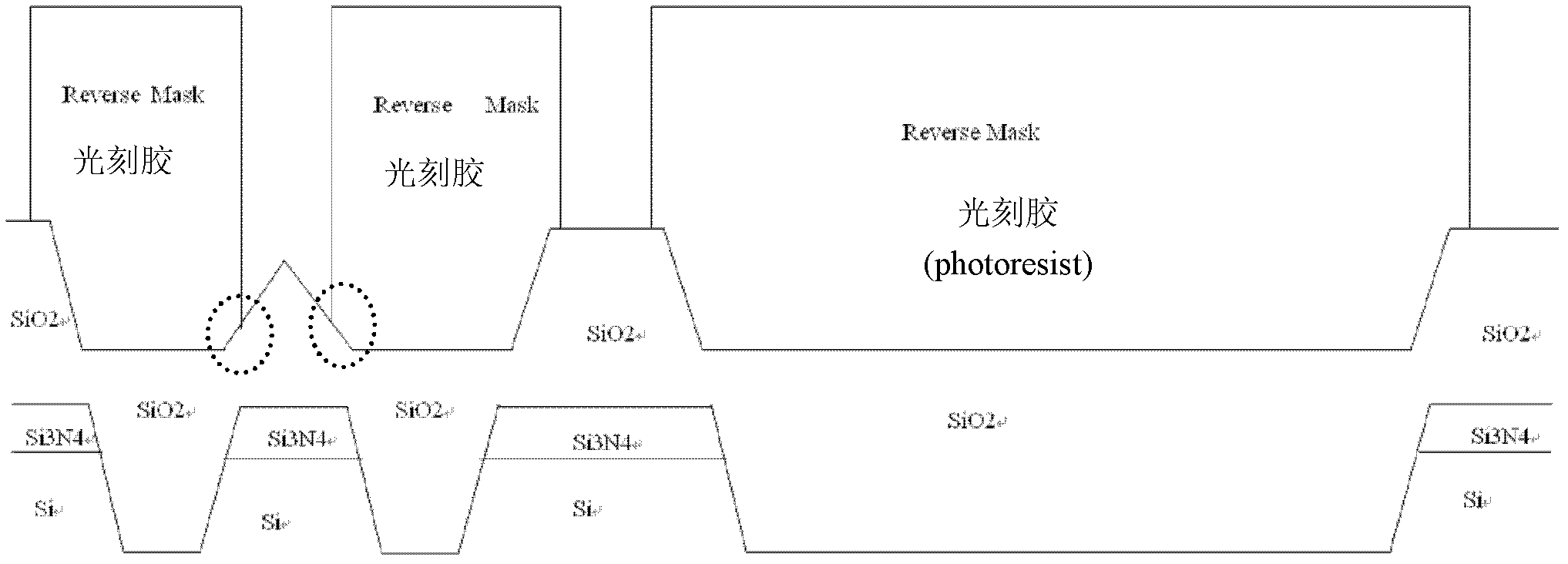

[0022] The method for improving the surface planarization of shallow trench isolation silicon oxide film of the present invention, its process diagram is as follows figure 2 As shown, the steps include:

[0023] (1) According to the existing STI process flow, after silicon oxide and silicon nitride deposition on the silicon substrate, STI silicon groove etching, HDP silicon oxide filling (filling), and then after STI CMP, carry out Lithography that opens in AA-dense regions (such as image 3 As shown), in the photolithography process, the thickness of the photoresist is about 1 μm, and the I-line photolithography machine is used for exposure;

[0024] Among them, the AA-intensive area can be: within any range of 10 μm×10 μm inside the chip, the area occupied by AA exceeds 40% or more of the total area;

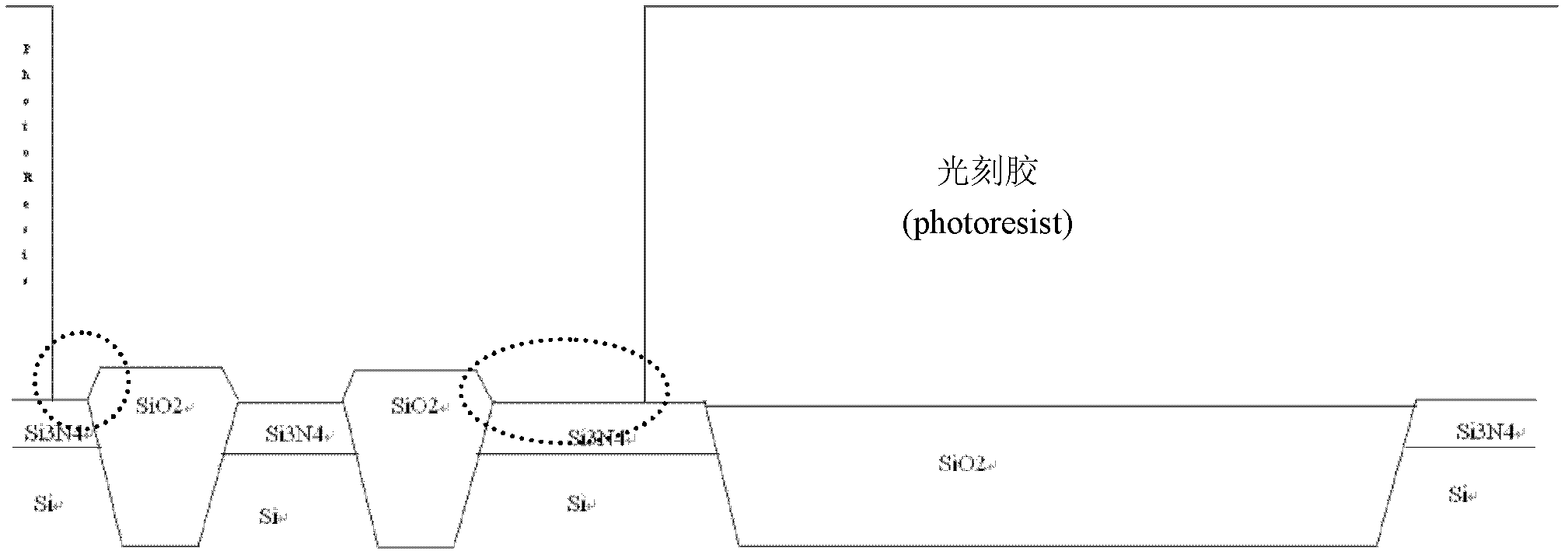

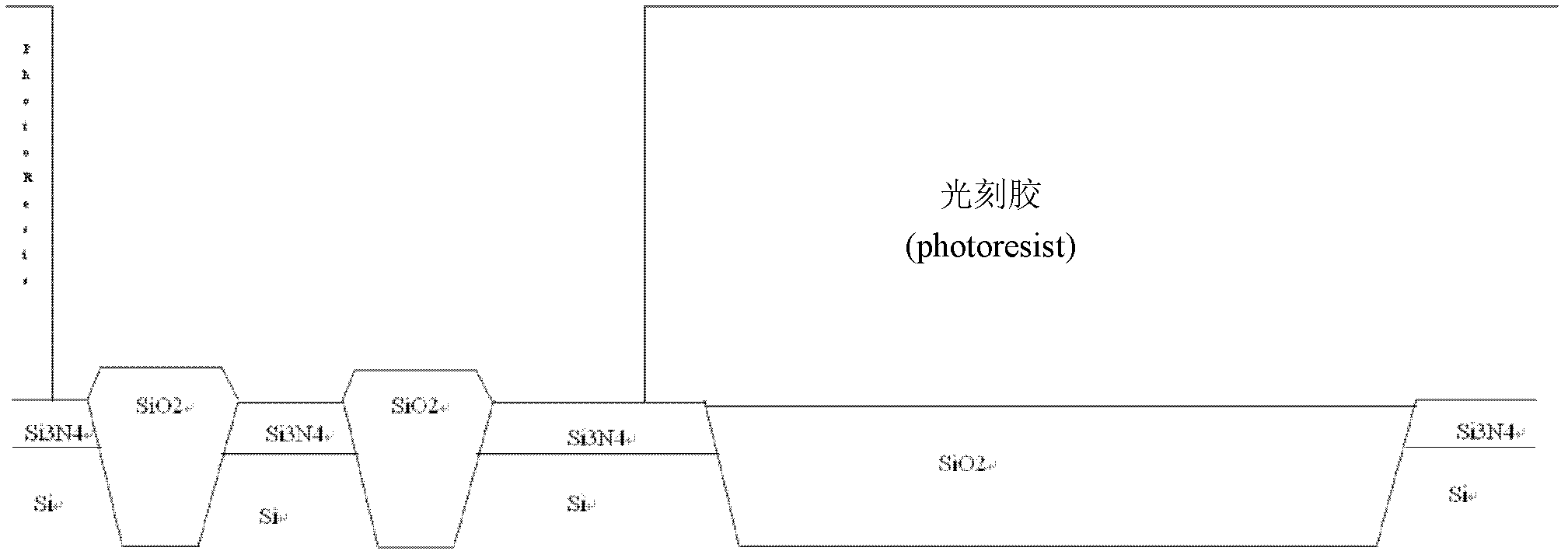

[0025] (2) Use SiO with a high selectivity ratio (greater than 10:1) to silicon nitride for a fixed time 2 Wet etching or dry etching, such as Figure 4 As shown, making ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More