Wafer back face thinning method

A backside thinning and wafer technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as excessive thickness, increased internal stress, and slow thinning rate, so as to reduce the probability of fragmentation and increase the number of finished products rate, reducing the effect of internal stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

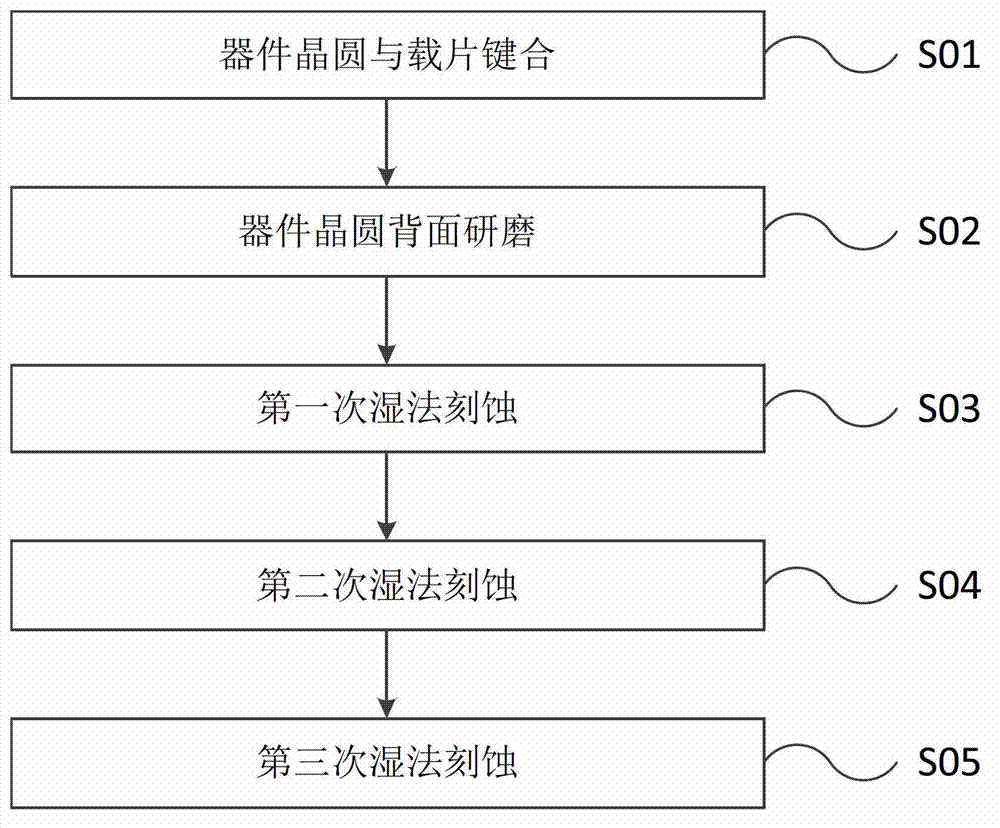

[0028] Such as figure 2 Shown is the prior art process flow chart, comprises the following steps:

[0029] Step S01, bonding the device wafer to the carrier;

[0030] Step S02, performing a second grinding on the back of the device wafer, and grinding the thickness of the device wafer to 50um-25um;

[0031] Step S03, performing a second wet etching on the device wafer, and etching the device wafer to 8um-6um;

[0032] Step S04, performing a third wet etching on the device wafer to etch away the remaining device wafer body substrate 3;

[0033] In step S05, the device wafer is wet-etched to 5.4um for the fourth time.

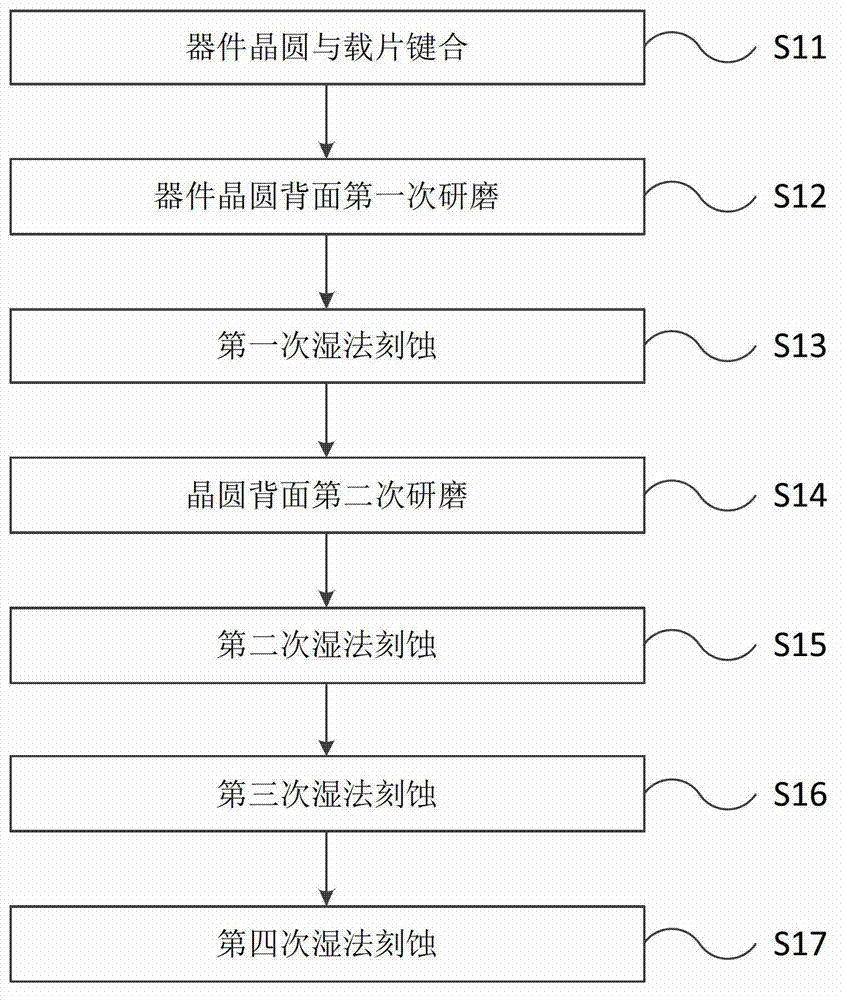

[0034] The present invention adopts the process of multi-step grinding and etching. The more t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com