Super junction structure semiconductor wafer with insulating layer isolation and preparation method thereof

A semiconductor and insulating layer technology, applied in the field of superjunction semiconductor wafers, can solve the problems affecting the shape of the columnar semiconductor structure, affecting the withstand voltage characteristics and reliability of the wafer, etc., and achieve the effects of compact product structure, lower resistance, and lower production costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

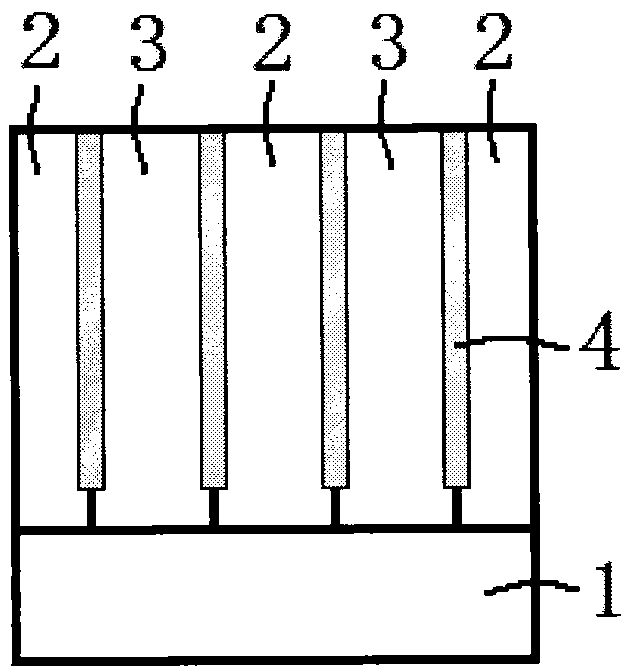

[0030] figure 1 It is a schematic cross-sectional view of a semiconductor wafer with an insulating layer-isolated superjunction structure of the present invention, combined below figure 1 The semiconductor device of the present invention will be described in detail.

[0031] A semiconductor wafer with a super junction structure isolated by an insulating layer, comprising: a substrate layer 1, which is an N conductivity type semiconductor silicon material, and the doping concentration of phosphorus atoms is 1E20cm -3 ; N-type semiconductor silicon material 2, located on the substrate layer 1, is an N-type semiconductor silicon material with a width of 2 μm and a thickness of 10 μm, and the doping concentration of phosphorus atoms is 1E16cm -3 ; The P-type semiconductor silicon material 3, located between the N-type semiconductor silicon materials 2, is an N-conduction type semiconductor silicon material with a width of 2 μm and a thickness of 10 μm, and the doping concentratio...

Embodiment 2

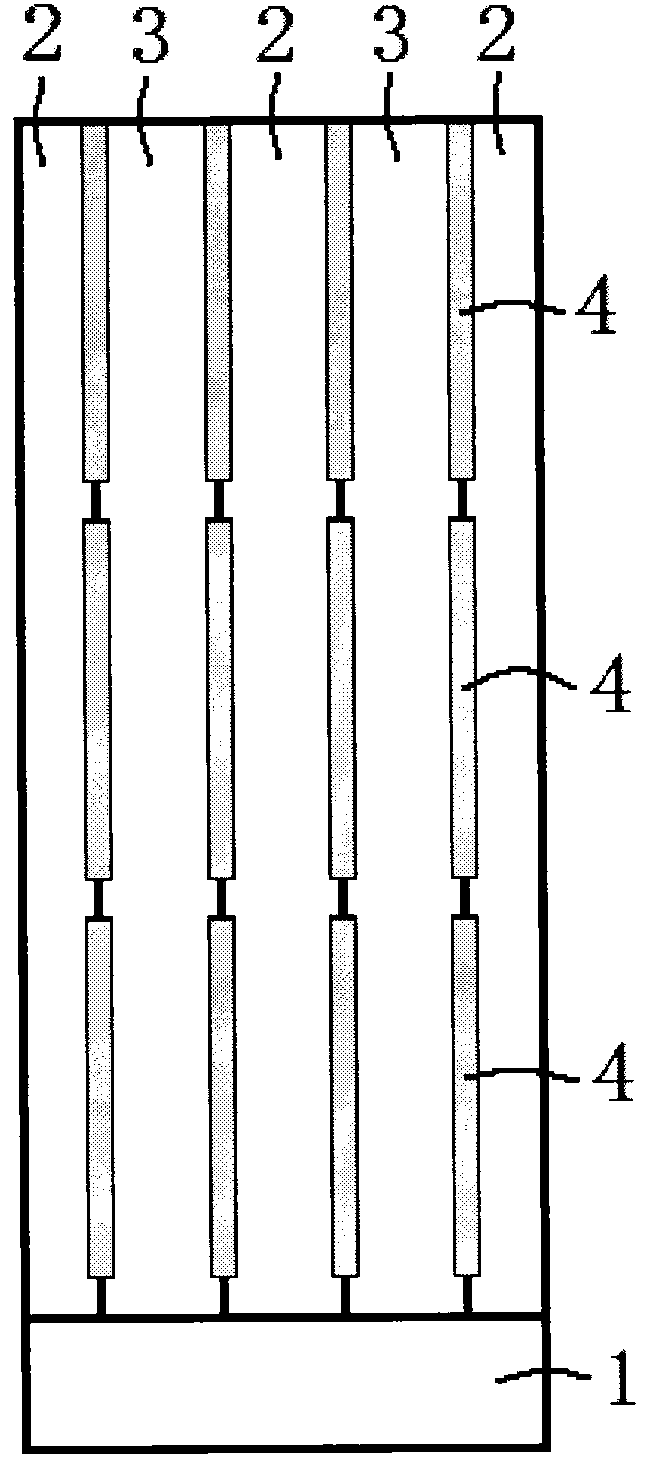

[0040] figure 2 It is a schematic cross-sectional view of a semiconductor wafer with an insulating layer-isolated superjunction structure of the present invention, combined below figure 2 The semiconductor device of the present invention will be described in detail.

[0041] A semiconductor wafer with a super junction structure isolated by an insulating layer, comprising: a substrate layer 1, which is an N conductivity type semiconductor silicon material, and the doping concentration of phosphorus atoms is 1E20cm -3 ; N-type semiconductor silicon material 2, located on the substrate layer 1, is an N-conduction type semiconductor silicon material with a width of 2 μm and a thickness of 30 μm, and the doping concentration of phosphorus atoms is 1E16cm -3 ; The P-type semiconductor silicon material 3, located between the N-type semiconductor silicon materials 2, is an N-conduction type semiconductor silicon material with a width of 2 μm and a thickness of 30 μm, and the doping...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More