Optimization design method of low-noise amplifier based on genetic algorithm

A low-noise amplifier, optimized design technology, applied in instrumentation, computing, special data processing applications, etc., can solve problems such as multi-objective optimization of LNA design

Active Publication Date: 2013-06-12

BEIHANG UNIV

View PDF2 Cites 18 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

[0007] The present invention overcomes the deficiencies in the prior art, discloses an optimal design method of a low noise amplifier based on a genetic algorithm, and solves the problem of multi-objective optimization in LNA design

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment

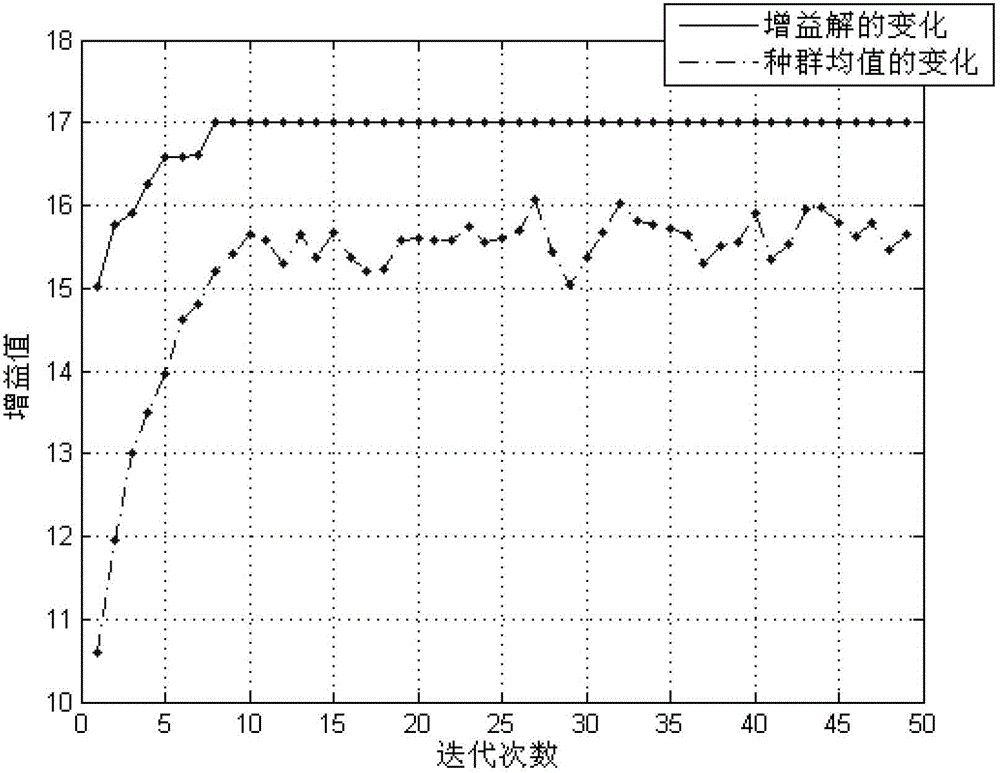

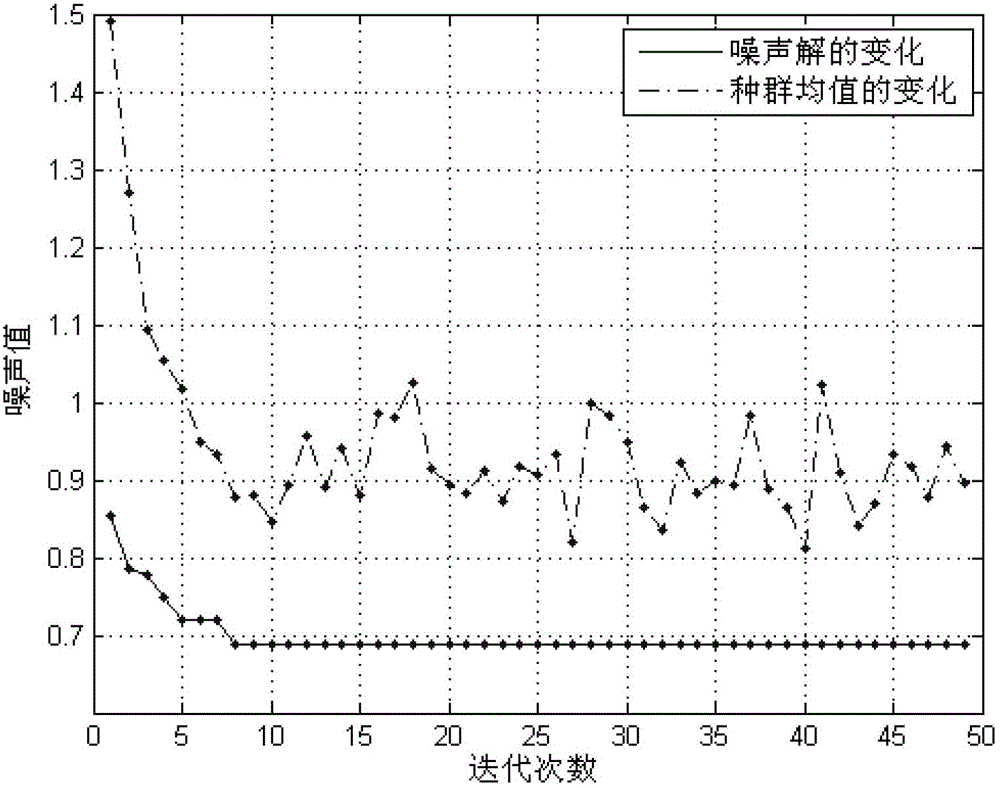

[0106] In this example, the multi-objective optimization of the design parameters of the LNA is carried out using a parallel genetic algorithm with an elitist strategy, such as figure 2 As shown, after 50 generations of iterations, the gain of the LNA is stable at about 17dB, and as image 3 As shown, the gain of LNA is stable at about 0.67dB. Both gain and noise figure have achieved good design results.

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

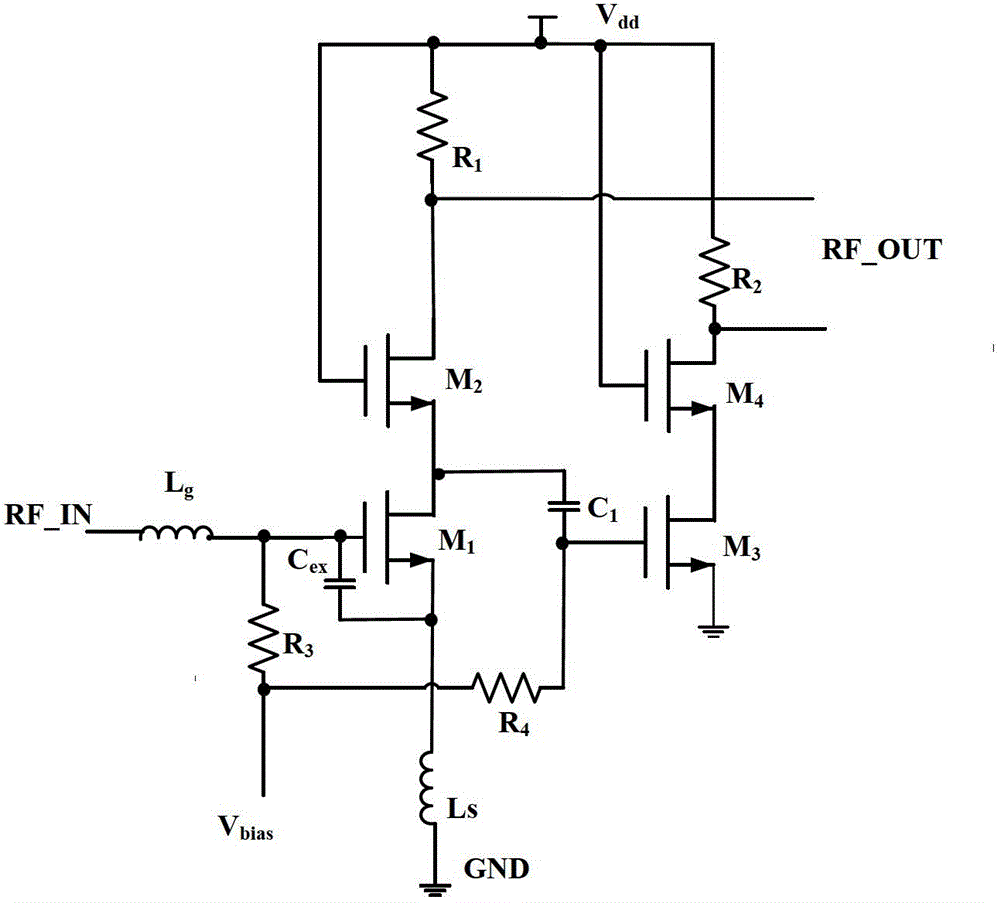

The invention discloses an optimization design method of a low-noise amplifier (LNA) based on a genetic algorithm, and solves the problem of multi-objective optimization in LNA design. Circuit parameters in the LNA such as transistor sizes and passive device values are used as variable quantities, impedance matching of the LNA and a current equation of transistors are used as constraint conditions, a circuit performance evaluation technology based on the equation is used as a circuit performance evaluation method, a parallel genetic algorithm with elitist strategy is used as a global search algorithm, and the gain, noise coefficient and power consumption of the LNA are optimized simultaneously. Through the optimization method, the optimization result of the circuit can be quickly obtained, and the method is extremely suitable for circuit design with particular restriction, performance and function. The method can be used for deep sub-micron radio frequency CMOS (Complementary Metal Oxide Semiconductor) integrated circuit, and is widely applied to electronic systems in the aviation and aerospace fields.

Description

technical field [0001] The invention belongs to the field of deep submicron RF CMOS integrated circuits, and in particular relates to the optimal design of a low noise amplifier (LNA). Background technique [0002] The low-noise amplifier is generally at the forefront, so its performance has a significant impact on the performance of the receiver. Its main function is mainly to provide gain to amplify the signal and suppress the overall noise of the system with a small noise figure, and at the same time need to match with the front-end antenna or antenna filter and maintain low power consumption. However, these parameters are closely related to each other and cannot be optimized individually. For example, increasing the gain usually leads to an increase in power consumption, and it is also difficult to realize noise optimization and input matching at the same time. Therefore, these parameter compromises are generally optimized as a whole to meet the overall performance requ...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G06F17/50

Inventor 张晓林申晶

Owner BEIHANG UNIV