Pec biasing technique for LEDs

A light-emitting diode, bias voltage technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problem that the N layer cannot be interconnected with metal interconnects.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

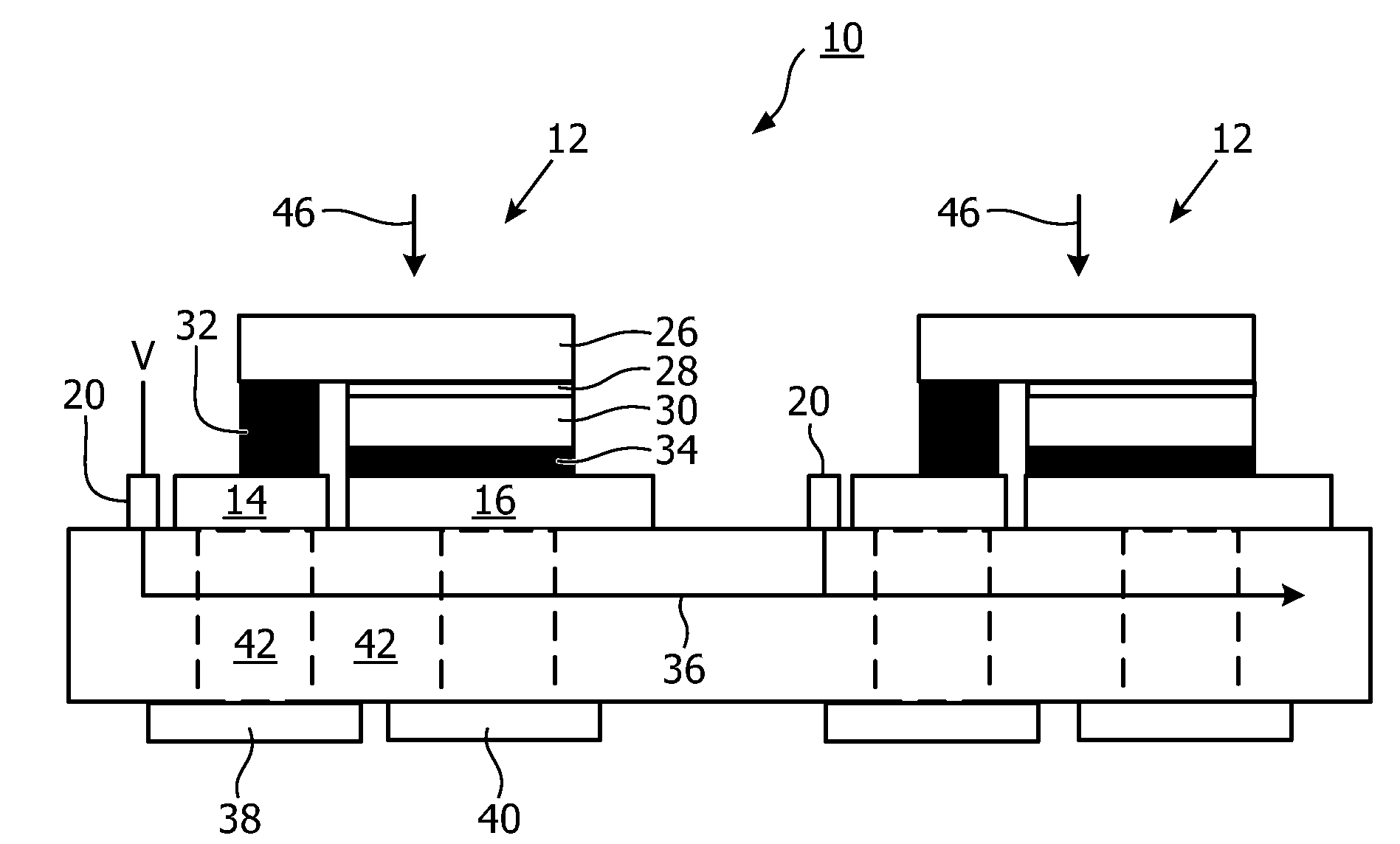

[0027] FIG. 1 shows a substrate wafer 10 populated with an array of LED dies 12 . There may be hundreds of dies 12 bonded to wafer 10 . The substrate base material can be ceramic, silicon, insulating aluminum or other materials.

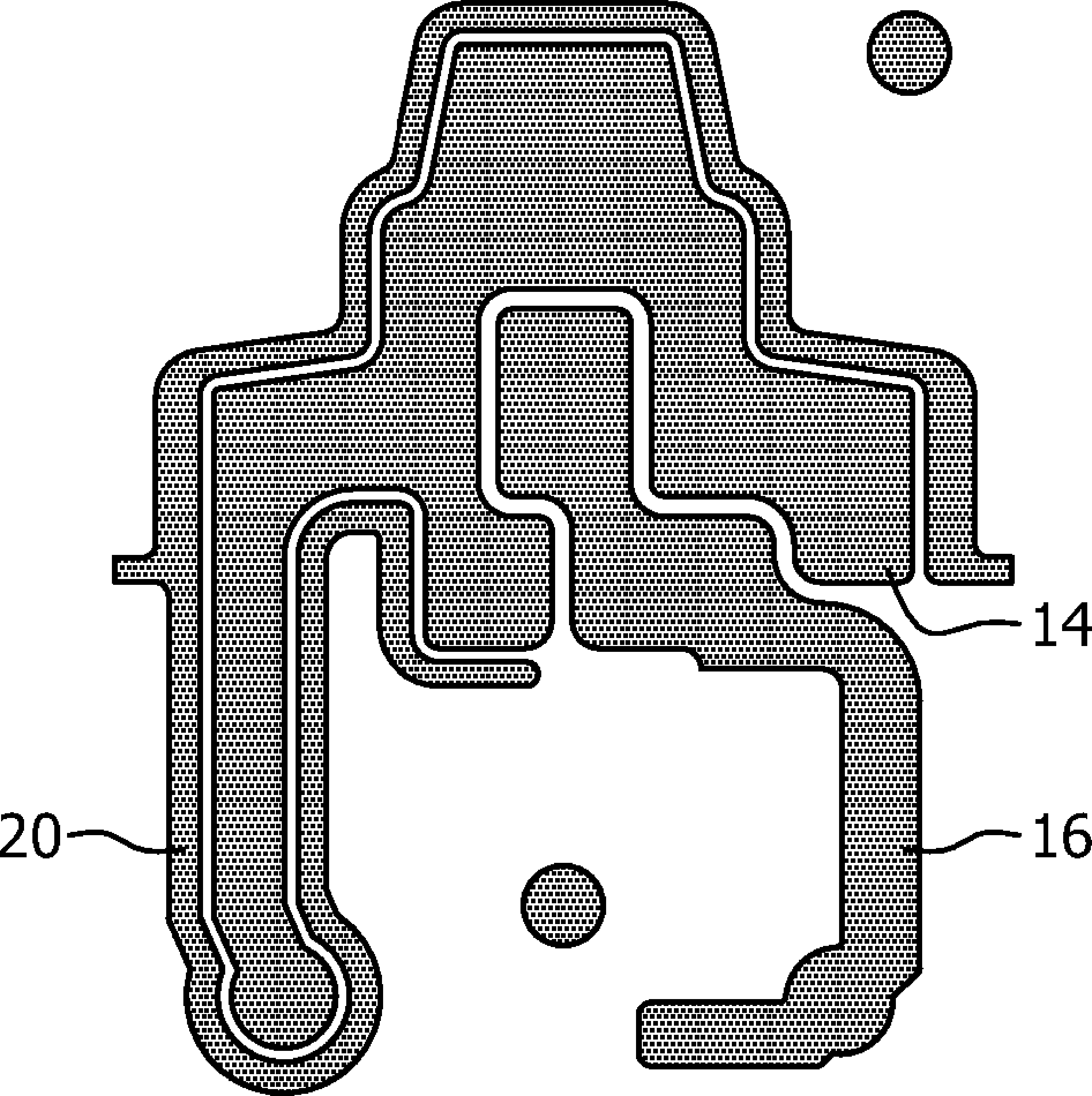

[0028] FIG. 2 is a close-up of four adjacent LED areas on wafer 10 showing N metal 14 and P metal 16 on the surface of wafer 10 . Metal 14 / 16 forms pads for bonding to the electrodes of LED die 12 . LED 12 and metal 14 / 16 can be any size. The metal 14 / 16 may be Ni / Au plated copper for bonding to the cathode and anode Ni / Au electrodes on the bottom surface of the LED die 12 . The LED electrodes can be bonded to the metal 14 / 16 by ultrasonic welding or other methods.

[0029] Metal 14 / 16 may be connected to the bottom pad of each substrate in wafer 10 by vias extending through wafer 10 . After singulation, the bottom pad can then be surface mounted on a printed circuit board.

[0030] Metal pattern 20 is formed very close to N-metal 14 (suc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More