Data communication circuit arranged among a plurality of processors and adopting data driving mechanism

A multi-processor, data communication technology, applied in the combination of a variety of digital computers, etc., to achieve the effect of reducing difficulty, strong scalability, and high parallel communication capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

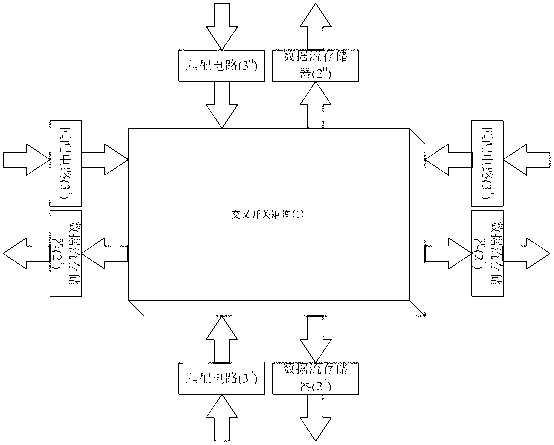

[0029] Such as figure 1 As shown, the inter-processor data communication circuit using the data-driven mechanism proposed by the present invention includes a crossbar switch matrix (1), 4 data stream memories (2 0 ,2 1 ,2 2 ,2 3 ), four matching circuits (3 0 、3 1 、3 2 、3 3 ). Its characteristics are: when sending data, the source CPU passes through the matching circuit (3 0 、3 1 、3 2 、3 3 ) to send data to the crossbar matrix (1) to realize data transmission; when receiving data, firstly, the source data is sent to the corresponding output port of the crossbar matrix (1) after the path is selected by the crossbar matrix (1), and the output data enters data stream memory (2 0 ,2 1 ,2 2 ,2 3 ), through dedicated memory for streaming data (2 0 ,2 1 ,2 2 ,2 3 ) After the integrity check, the function number and data are taken out and sent to the corresponding destination CPU.

Embodiment 2

[0031] This embodiment is basically the same as Embodiment 1, and the special features are as follows:

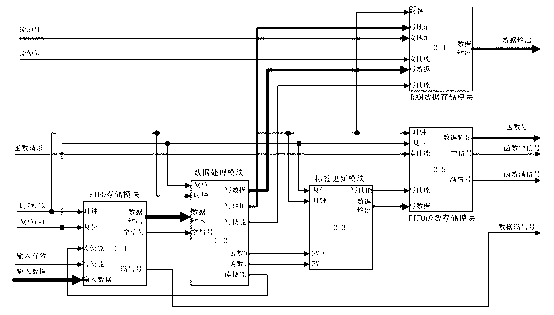

[0032] , data flow memory

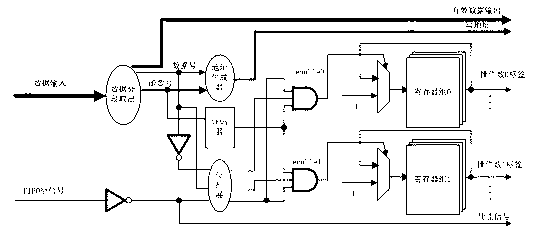

[0033] see figure 2 , the data flow memory is a special memory, mainly composed of FIFO storage, data processing module, label update module, RAM data memory and FIFO function memory. Among them, FIFO storage is mainly used to store the input data, so that the data can be received and transmitted correctly; the data processing module is composed of data segment extraction, address generator, decoder, bit expansion and control logic, and takes out the input data. The function number, data number and data, and the corresponding address is generated by the address generator, so that the data is transmitted to the relevant function module for corresponding operation, and the corresponding operand label is generated; the label update module is generated by the label device, tag function data table registers and other control logic. Its main functi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More