Low delay filter design method for sampling rate conversion in electronic transformer

A technology for designing electronic transformers and filters, which is applied in the fields of instruments, computing, and electrical digital data processing, etc., and can solve the problems of large group delay of digital low-pass FIR filters, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

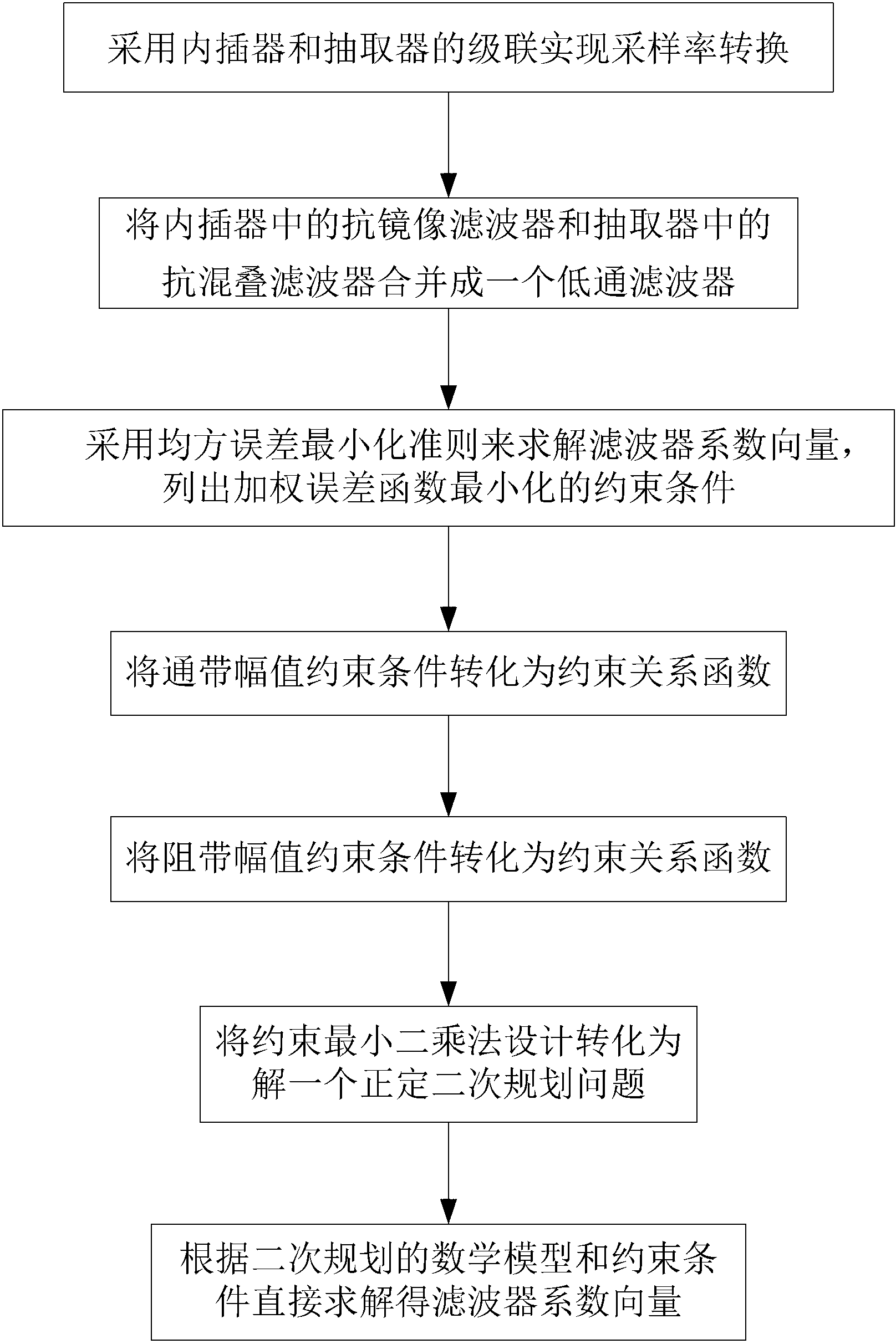

Method used

Image

Examples

Embodiment

[0148] Perform simulation analysis of various situations on a 500kV two-turn transformer, and the system model is as Figure 5 As shown, the line length is 330km, the transformer adopts Yn / D-11 wiring, the transformation ratio is 500 / 13.8kV, the angle of rotation is the phase current differential mode of subtracting zero sequence, and the angle of the star side to the triangle side is adopted.

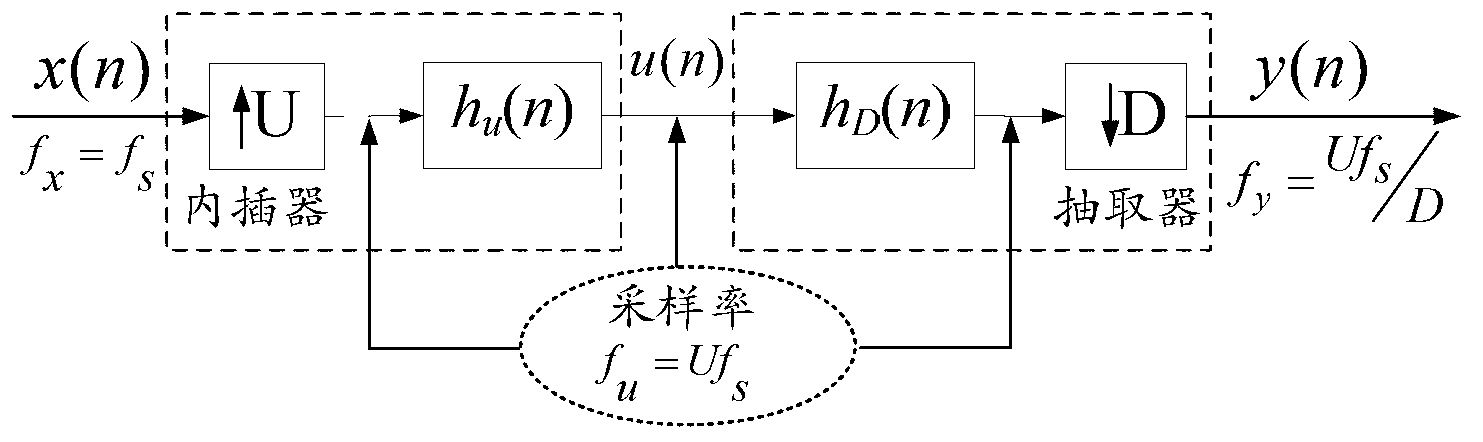

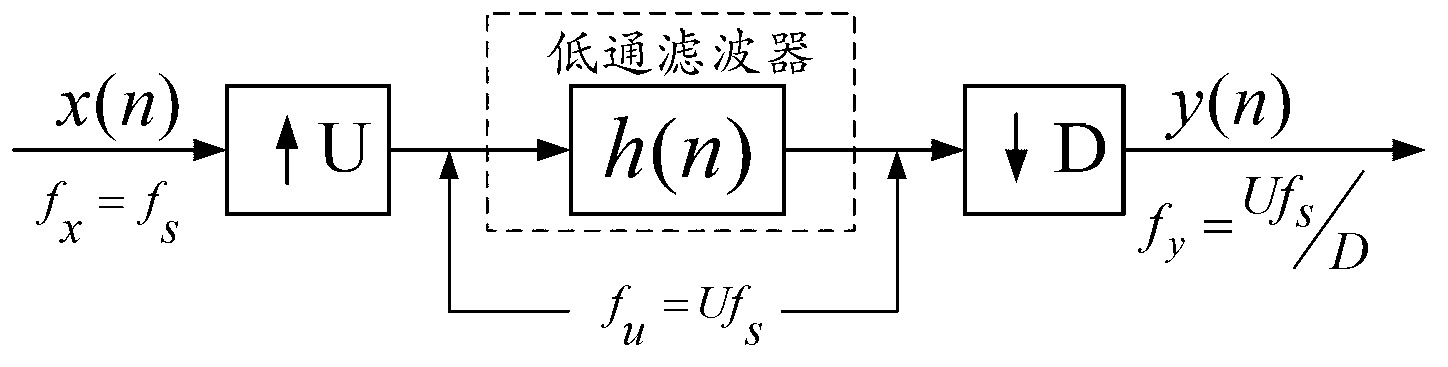

[0149] The IEC60044-8 standard stipulates that the rated sampling frequency of ECT can be any of 20 times, 48 times, and 80 times the power frequency. In order to make the sampling frequency of the current sampling values of each branch consistent, the corresponding decimation factor and interpolation can be determined Factor, its structure is like Image 6 Shown. Therefore, the designed low-pass filter may work at two frequencies, namely 4kHz and 12kHz.

[0150] ECT1 and ECT2 are electronic current transformers respectively installed at the head and end of the transformer to provide sa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More