Explicit multi-core Cache consistency active management method facing flow application

A technology of active management and consistency, applied in electrical digital data processing, instruments, computers, etc., can solve the problems of unreasonable waste of system resources, lengthy processing time, large area, and power consumption overhead due to the blindness of broadcast requests. Internet communication and layout and routing pressure, alleviation of Internet network pressure, and low hardware implementation cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

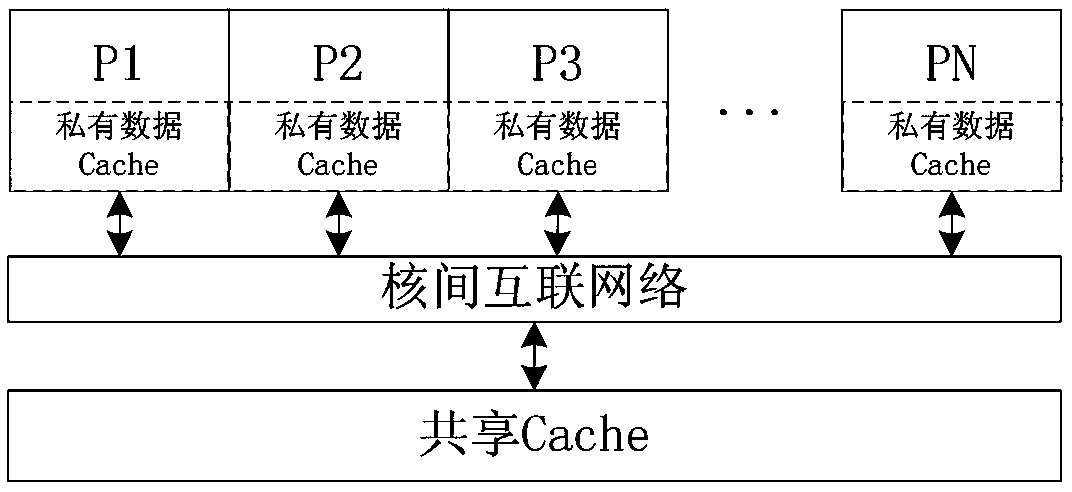

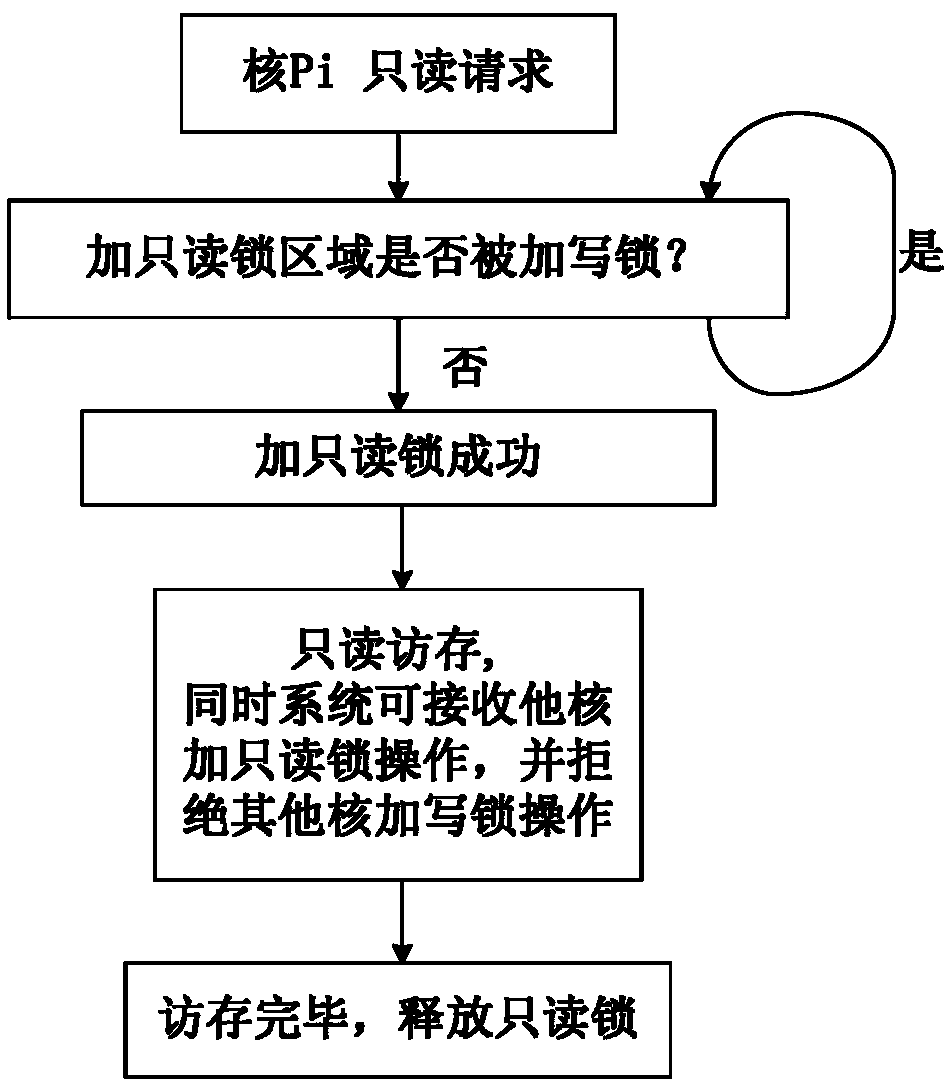

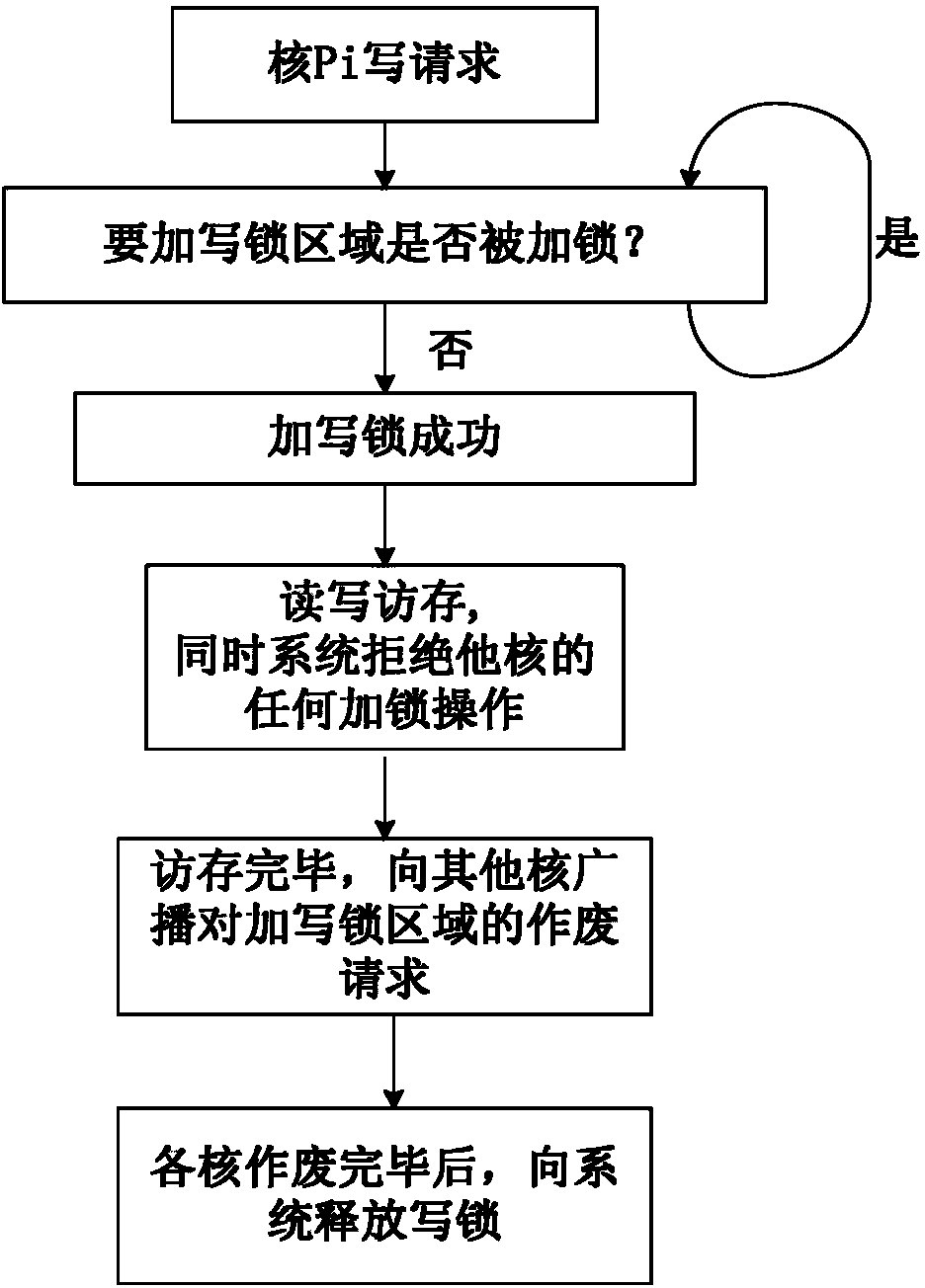

[0034] The present invention is aimed at the huge hardware overhead brought by the Cache consistency protocol adopted by the current mainstream multi-core microprocessor, and its large amount of maintenance data consistency transaction delay reduces the streaming application performance, etc., and designs a stream application data partial Cache coherency active management method for multi-core processors that can better adapt to the locality of its producers and consumers. In this method, each single-core private data cache in a multi-core processor only needs to autonomously manage the shared data in its private data cache line as needed, without broadcasting request operations, which greatly reduces the hardware and communication required to maintain cache consistency Overhead reduces a large amount of data consistency transaction d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More