Silicon wafer surface topography reconstruction method based on B-spline

A technology of silicon wafer surface and spline surface, applied in image data processing, instrumentation, calculation, etc., can solve the problems of low responsiveness and low precision, achieve the effect of improving speed and precision, ensuring effective recovery, and eliminating burr phenomenon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

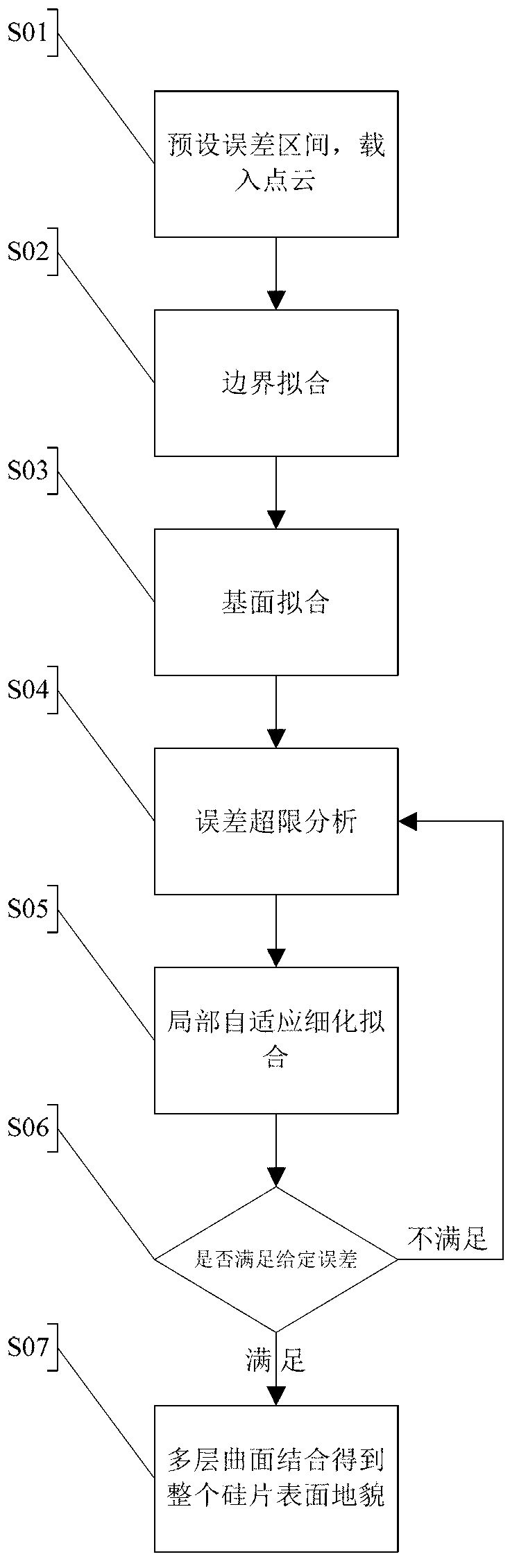

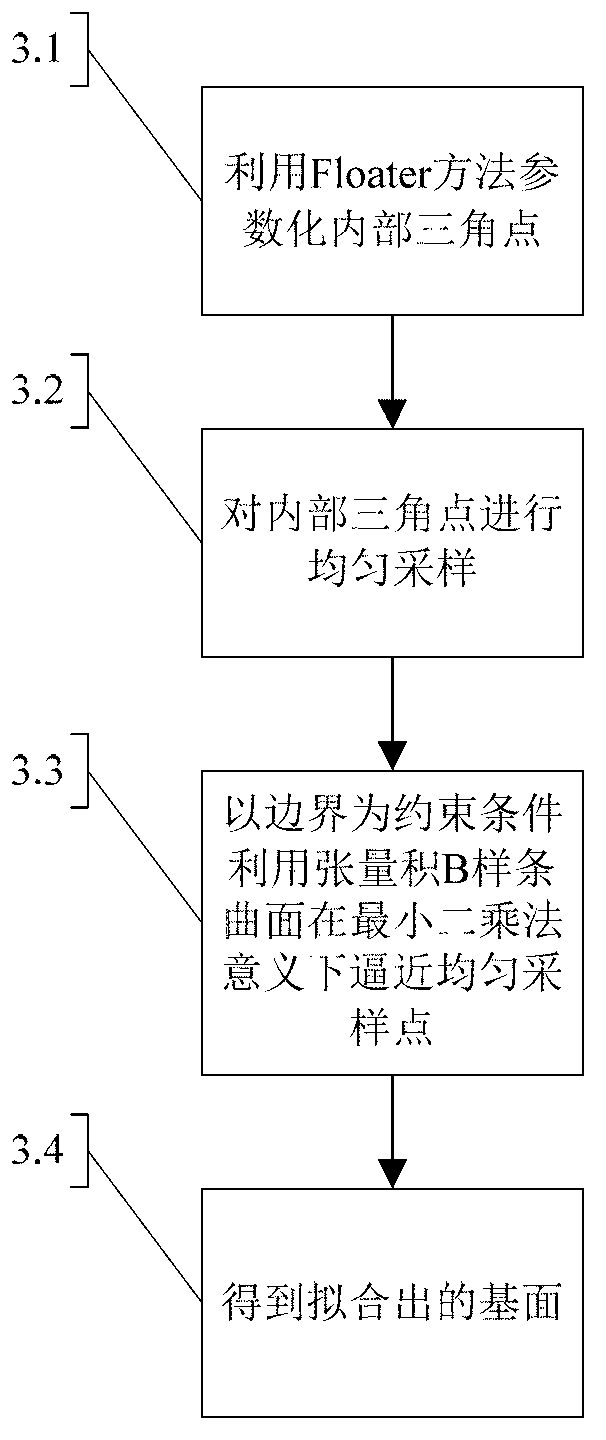

[0048] In order to make the purpose, technical solution and advantages of the present invention clearer, the overall algorithm flow of the present invention, the boundary synchronous fitting flow, the base surface fitting flow, and the local refinement fitting algorithm flow are described below in conjunction with the accompanying drawings and specific embodiments. Further introduction.

[0049] Such as figure 1 As shown, the overall algorithm flow is as follows:

[0050] Step S01: First preset the error interval ε 0 , and then load the point cloud of the surface topography of the silicon wafer, connect each point in the point cloud with two adjacent points, and triangulate the entire point cloud into triangular points;

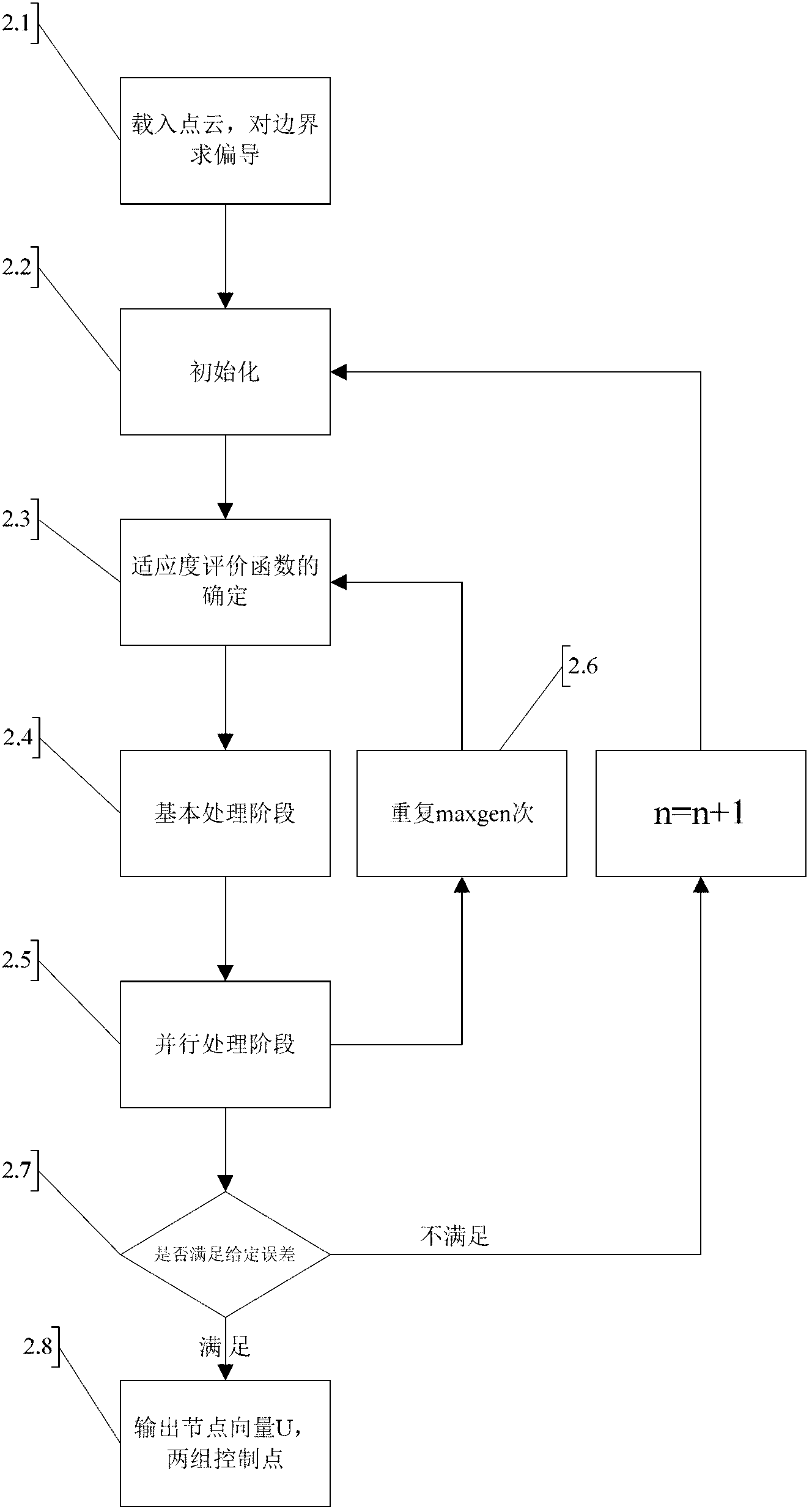

[0051] Step S02: Then parameterize the boundary points of the triangular mesh, and then use the genetic algorithm to perform two simultaneous boundary curve fittings on the boundary to obtain four B-spline boundary curves interpolated at the four corner poi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More