Grid electrode LELE dual graph forming method based on DARC mask structure

A double image and mask technology, applied in the field of microelectronics, can solve the problems of not being commonly used, spending a lot of time and energy, and increasing the difficulty of controlling the uniformity of critical dimensions, so as to save costs and improve maturity and stability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

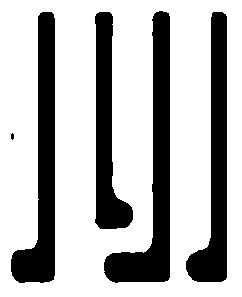

[0035] Figure 2-8 It is a schematic diagram of the process structure of an embodiment of the gate LELE double pattern forming method based on the DARC mask structure of the present invention; as Figure 2-8 As shown, a gate LELE double patterning method based on DARC mask structure is preferably applied to the gate line tail cutting process of 28 / 20 nanometers and below technology nodes on a 193nm immersion optical lithography platform , the above methods include:

[0036] First, if figure 2 As shown, on a silicon substrate (Silicon) 1, a gate oxide layer 2, a polysilicon layer (poly) 3, a silicon nitride layer (SiN) 4, an advanced pattern film layer (APF) 5 and a dielectric anti-reflection layer ( Dielectric Anti_Reflectivity Coating, referred to as DARC) 6, to form such as figure 2 The structure shown; wherein, the gate oxide layer 2, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More