Semiconductor wafer and method for manufacturing same

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, manufacturing tools, etc., to achieve the effect of improving productivity and yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

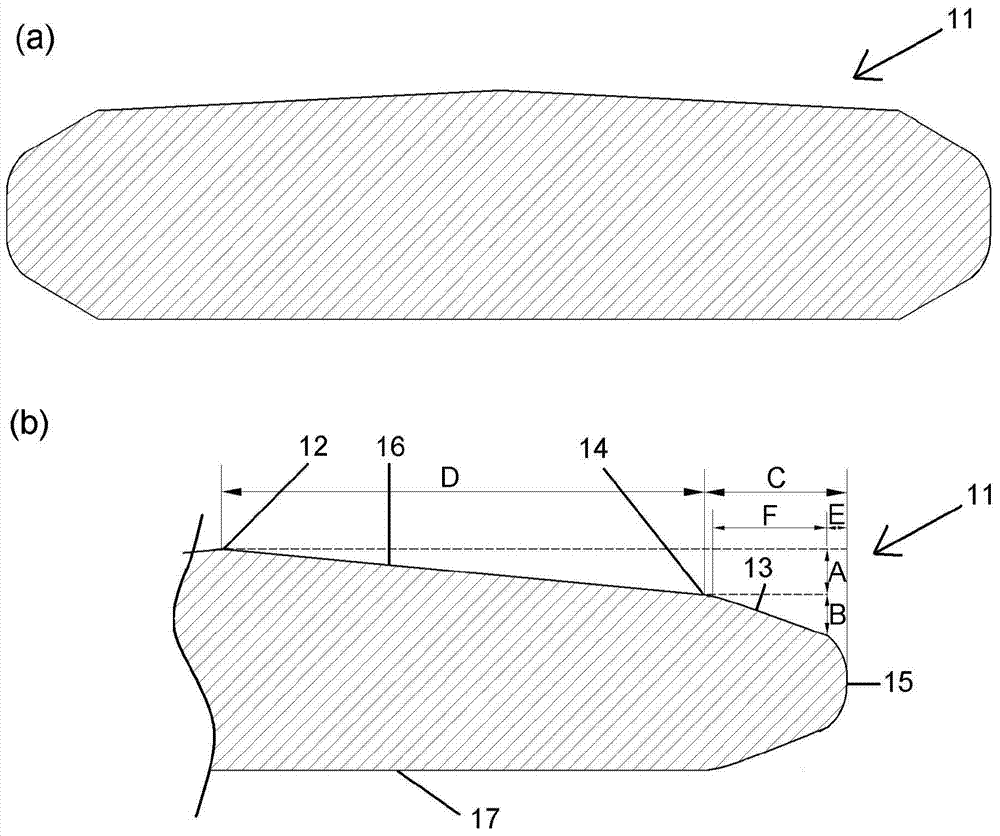

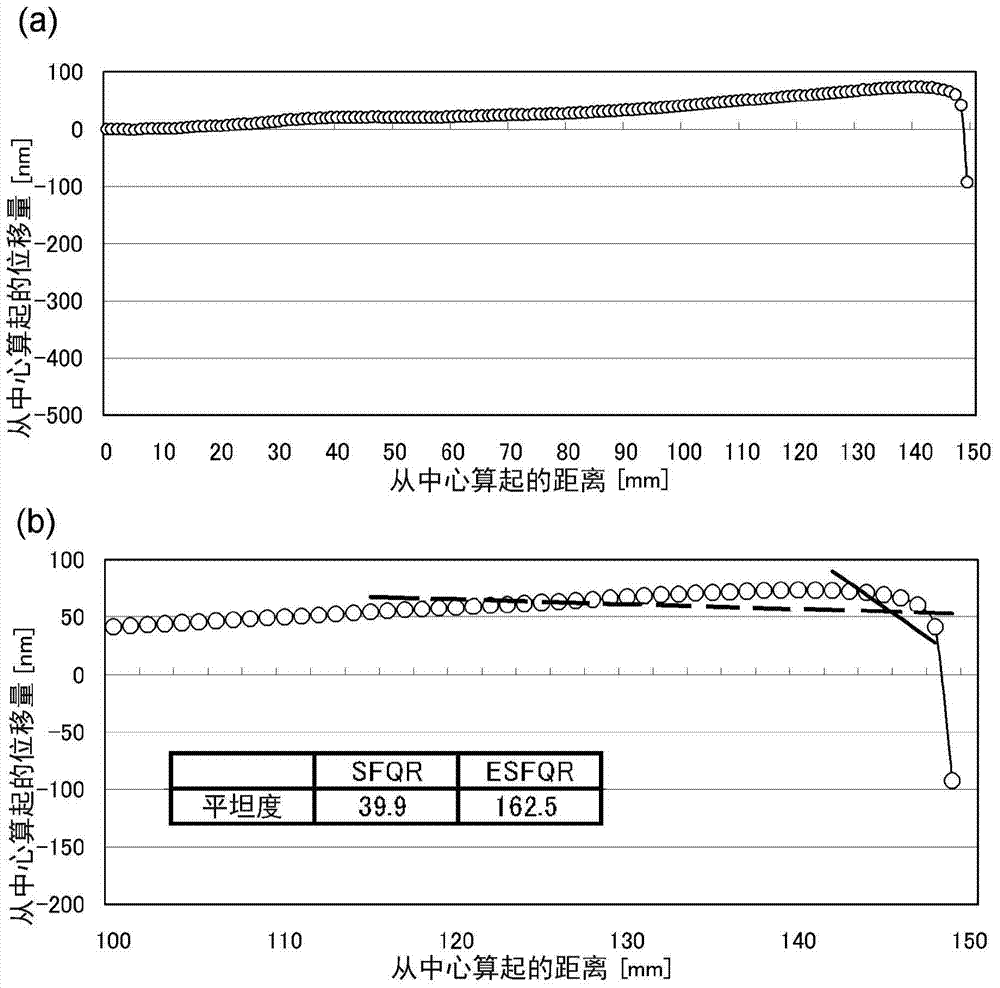

[0106] The single crystal rod was sliced into silicon wafers with a diameter of 300 mm, and the silicon wafers were chamfered (chamfered) and planarized. Then, use the double-sided grinding machine described in Japanese Patent Application Laid-Open No. 2003-285262 and adjust to the following conditions to perform double-sided grinding: between the center of the semiconductor wafer and the peripheral sag start position, the thickness direction of the semiconductor wafer The amount of displacement is 100 nm or less, and the center of the semiconductor wafer has a convex shape. At this time, since it is not preferable to cause peripheral sagging due to double-sided polishing, a hard foamed urethane pad was used as a polishing cloth, specifically, MH-S15A manufactured by Nitta Haas was used. The abrasive slurry is made of colloidal silica with a particle size of 0.05 μm adjusted to pH 10.5, and the abrasive load is 200 g / cm 2for grinding. In order to stably obtain wafers with ...

Embodiment 2

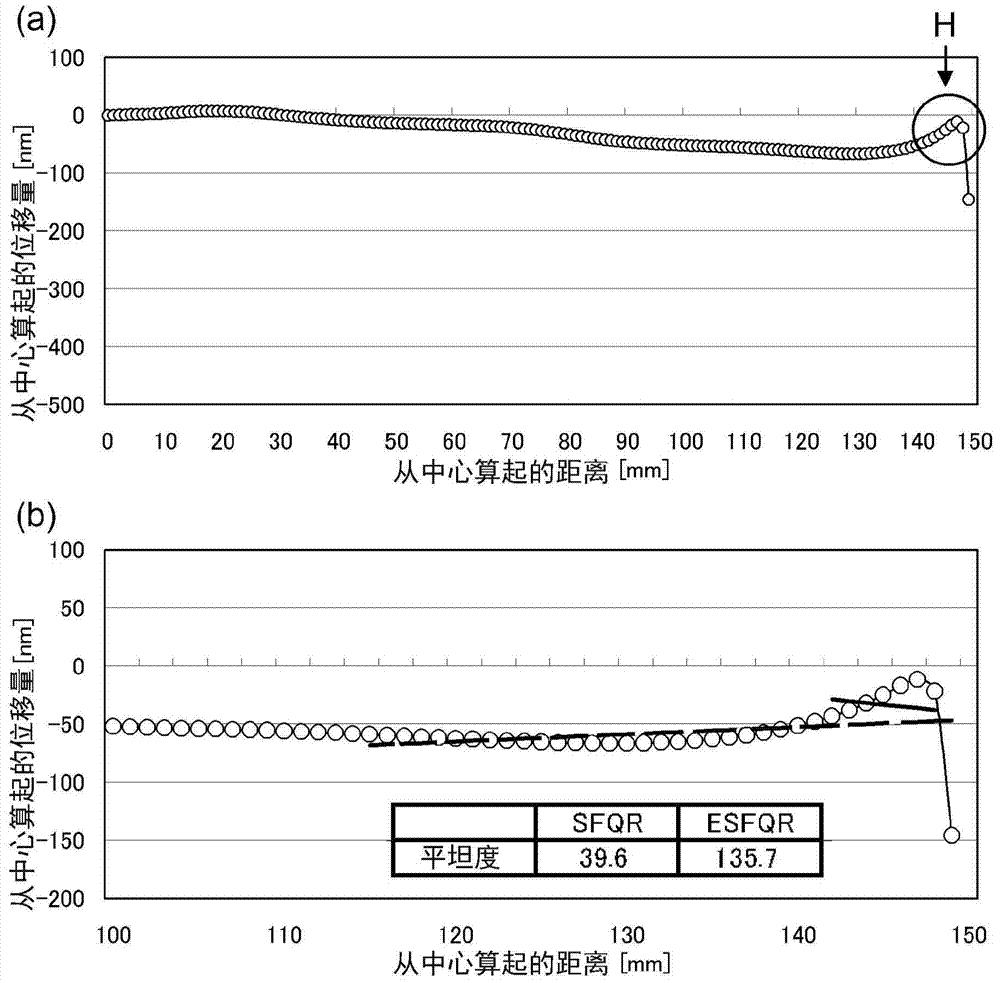

[0108] The surface temperature of the polishing cloth during polishing is relatively high in temperature at the central part of the polishing cloth compared with the outer peripheral part because heat is accumulated during polishing. This temperature difference will affect the grinding rate, so by controlling the range of this area, the starting position of sag can be controlled. In Example 2, in addition to adjusting the grinding load, the number of revolutions of the grinding head, and the slurry supply temperature in a manner that does not change the average in-plane grinding amount of the wafer, and increasing the area of high temperature to be greater than that of Example 1, and to make The start position of the peripheral sag is closer to the center side (35mm from the outer peripheral end to the center side) than the outer peripheral portion of the semiconductor wafer that is the measurement object of ESFQR, except that one side of the silicon wafer is chemically mecha...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com