Formation method of metal gate

A metal gate, metal layer technology, applied in electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of easy leakage current, affect transistor stability, high temperature, reduce the occupied space, The effect of improving speed and efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0045] refer to Figure 4 , Figure 4 It is a schematic flowchart of a method for forming a metal gate according to the first embodiment of the present invention, including the steps:

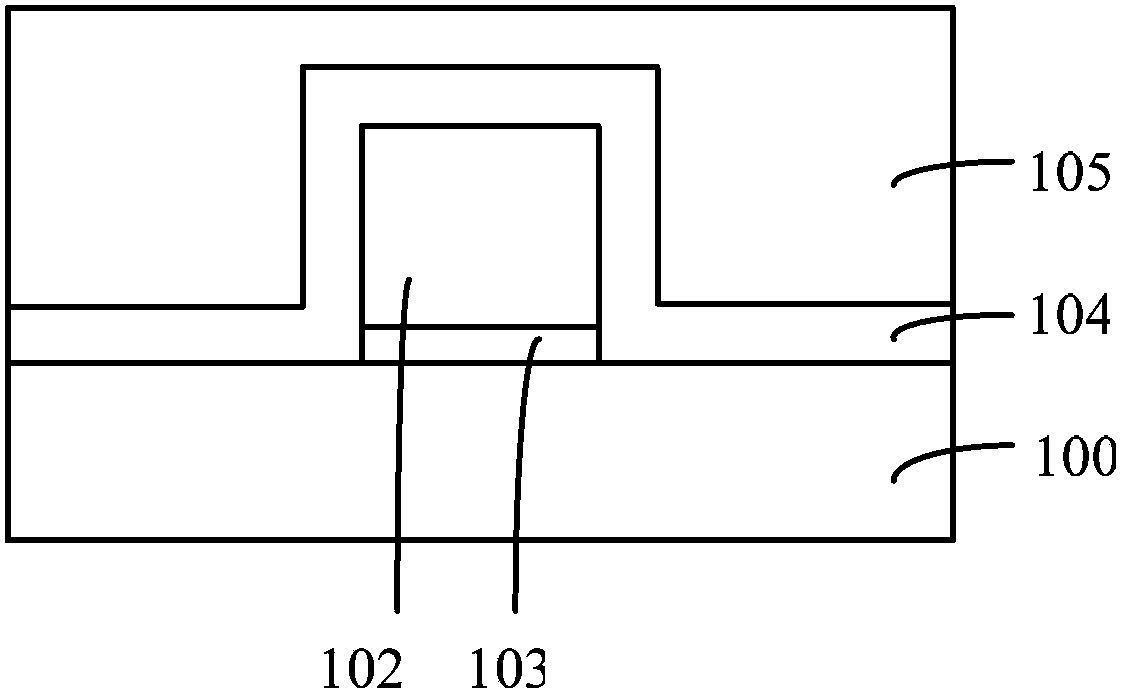

[0046] Step S21, a semiconductor substrate is provided, a dummy gate is formed on the semiconductor substrate, a gate dielectric layer is formed between the semiconductor substrate and the dummy gate, and the gate dielectric layer is a stack of an interface layer and a high-K dielectric layer structure;

[0047] Step S22, forming a dielectric layer on the surface of the semiconductor substrate, and the surface of the dielectric layer is flush with the surface of the dummy gate;

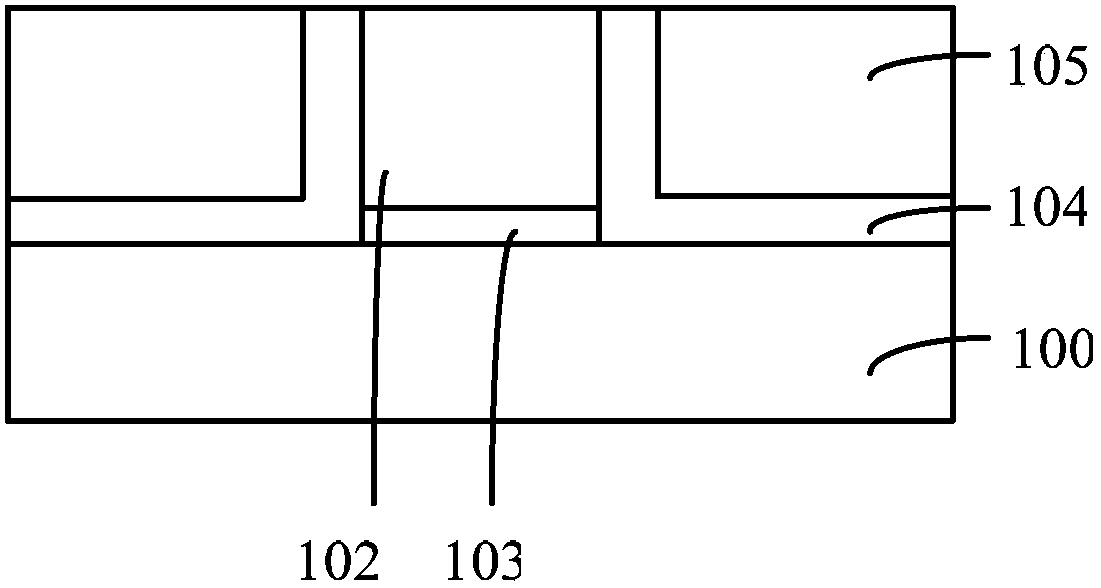

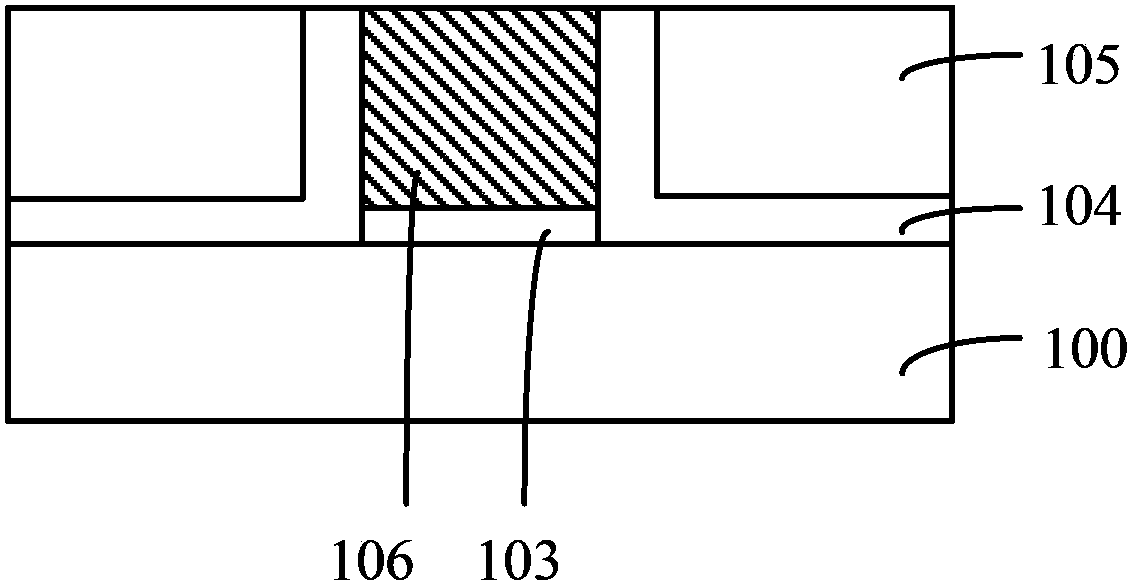

[0048] Step S23, removing the dummy gate, forming a groove, and forming a functional layer on the bottom and sidewalls of the groove;

[0049] Step S24, a silicon material layer is formed on the surface of the functional layer in the groove, and the surface of the silicon material layer is flush with the surface of ...

no. 2 example

[0085] refer to Figure 13 , Figure 13 It is a schematic flowchart of a method for forming a metal gate according to the second embodiment of the present invention, including the steps:

[0086] Step S31, providing a semiconductor substrate, the semiconductor substrate includes a first region and a second region, a first dummy gate is formed on the first region of the semiconductor substrate, and a first dummy gate is formed on the second region of the semiconductor substrate There is a second pseudo gate;

[0087] Step S32, forming a dielectric layer on the surface of the semiconductor substrate, and the surface of the dielectric layer is flush with the surfaces of the first dummy gate and the second dummy gate;

[0088] Step S33, removing the first dummy gate, forming a first groove, and forming a first functional layer on the bottom and sidewalls of the first groove;

[0089] Step S34, forming a first silicon material layer on the surface of the first functional layer, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More