A method for forming a shallow trench isolation structure

A technology of isolation structure and shallow trench, which is applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problem of poor isolation performance of shallow trench isolation structures, leakage of semiconductor devices, and influence on the stability of semiconductor devices, etc. problems, to achieve the effect of eliminating Q-time effect, improving the uniformity of film thickness, and not easy to leak

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

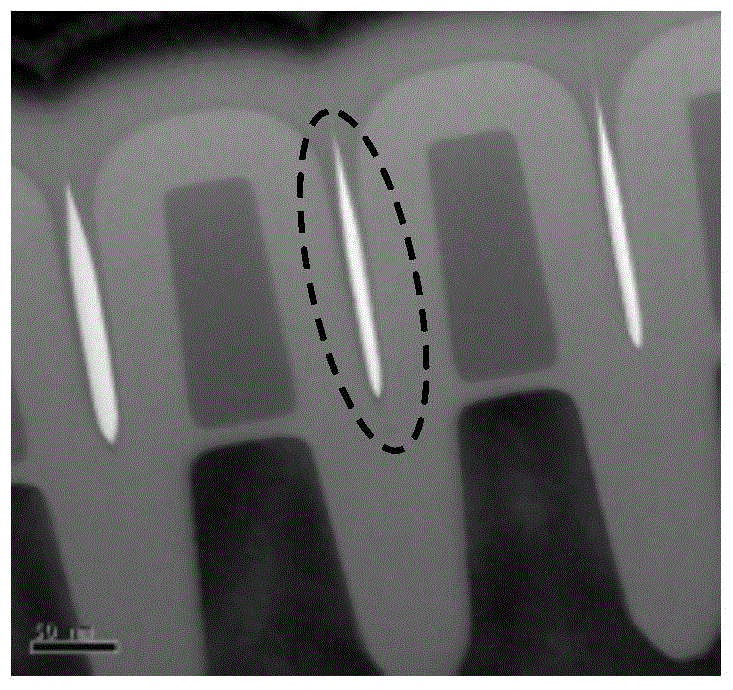

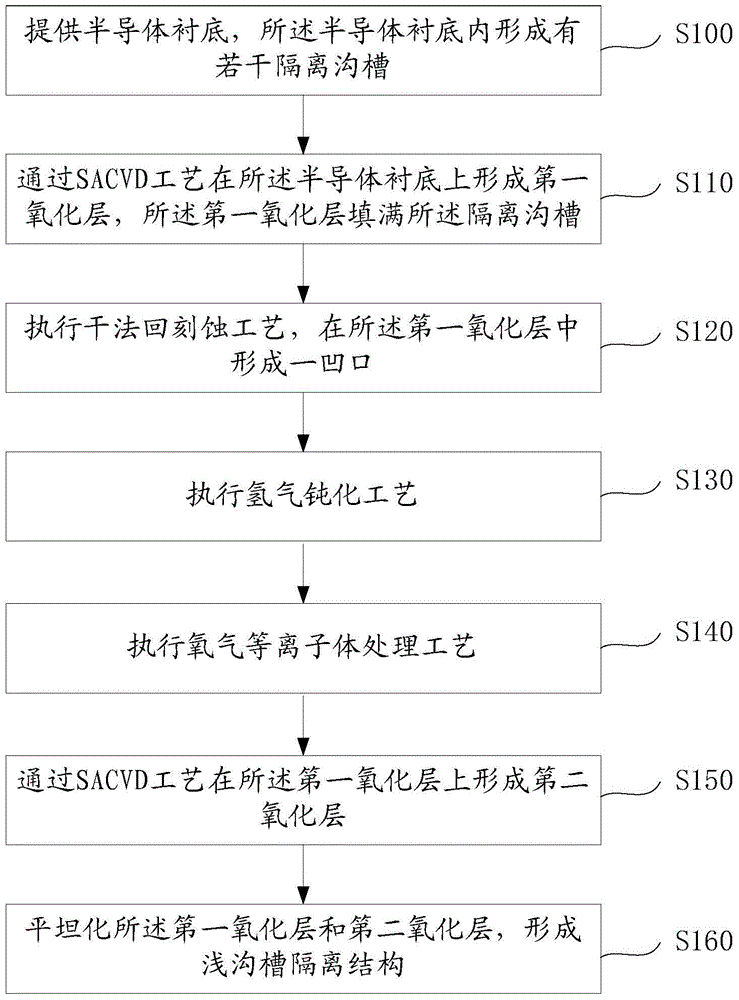

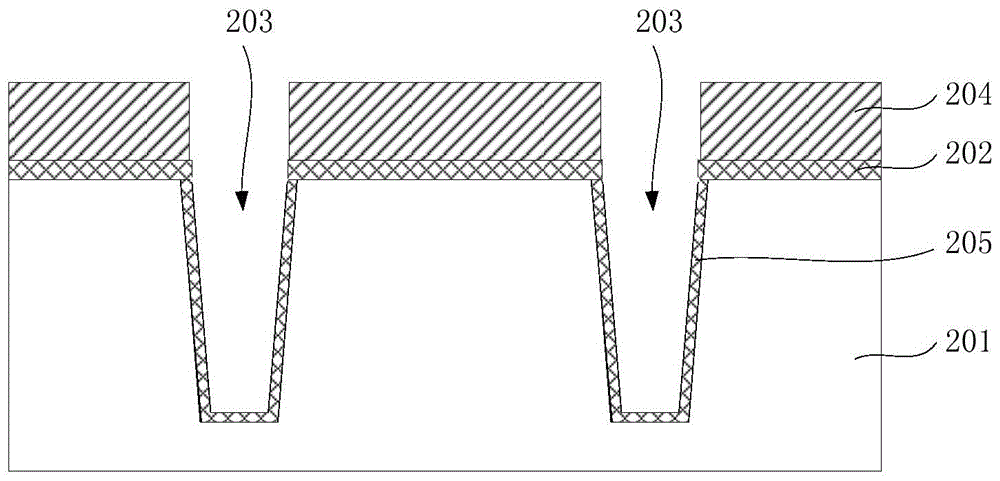

[0030] As mentioned in the background, with the continuous reduction of the feature size of semiconductor devices, the size of the shallow trench isolation structure used for device isolation is also reduced, and the aspect ratio of the isolation trench used to form the shallow trench isolation structure becomes smaller. Large, when the oxide layer is filled and formed in the isolation trench by the SACVD process, a fragile surface is likely to appear, resulting in poor isolation performance of the shallow trench isolation structure, and semiconductor devices including the shallow trench isolation structure are prone to leakage and poor stability. For this reason, after the first oxide layer is formed by the SACVD process in the present invention, the dry etching process is performed to eliminate the fragile surface, and then the second oxide layer is formed by the SACVD process, and then the planarization process is performed, and the shallow trench thus formed The isolation e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More