A three-valued inverter based on CNFETs

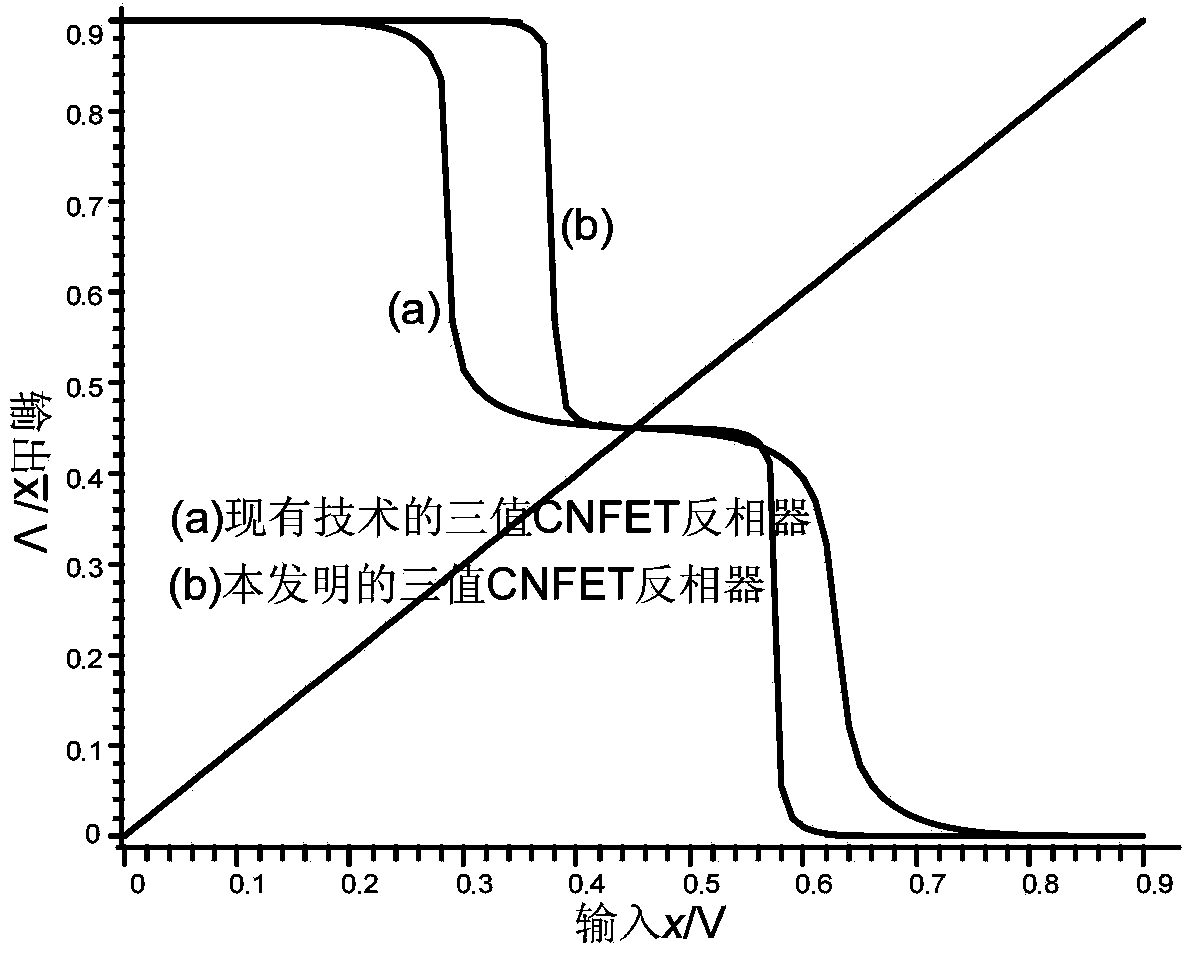

An inverter and base technology, applied in the field of ternary inverters, can solve the problems of voltage fluctuation, large power consumption, and deterioration of the DC characteristic curve.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

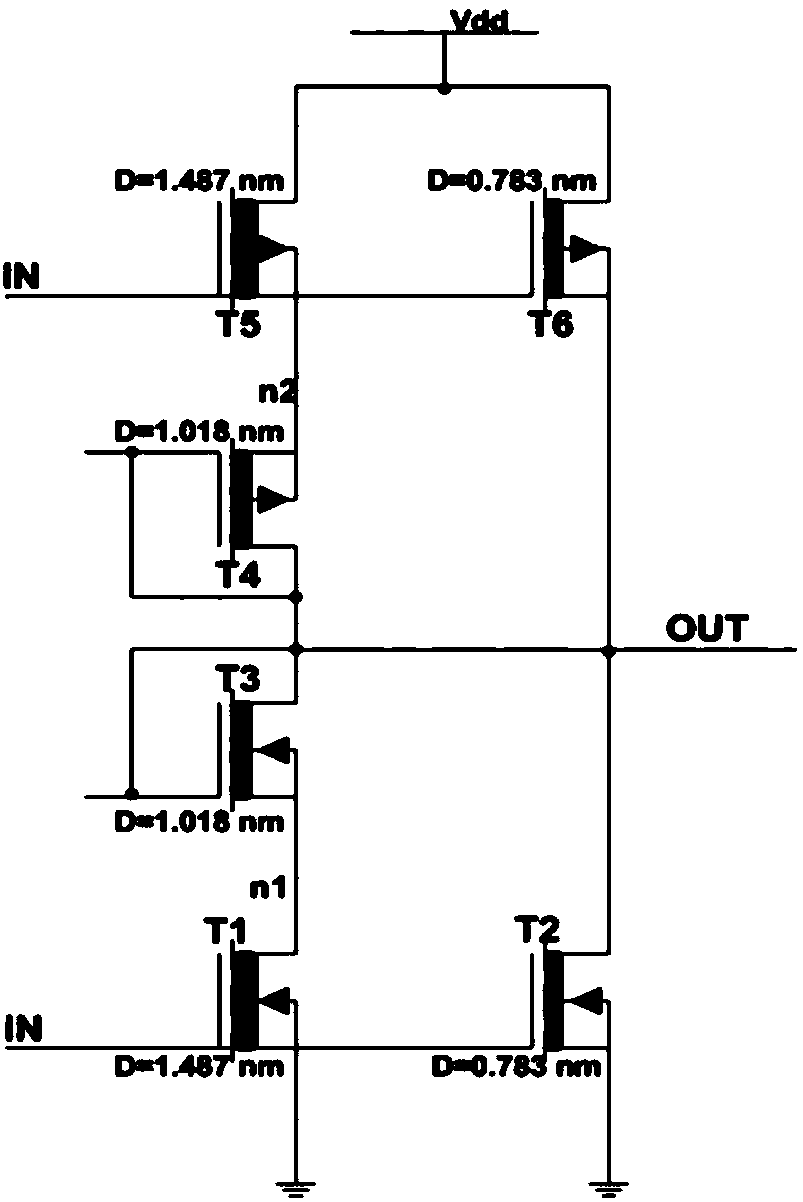

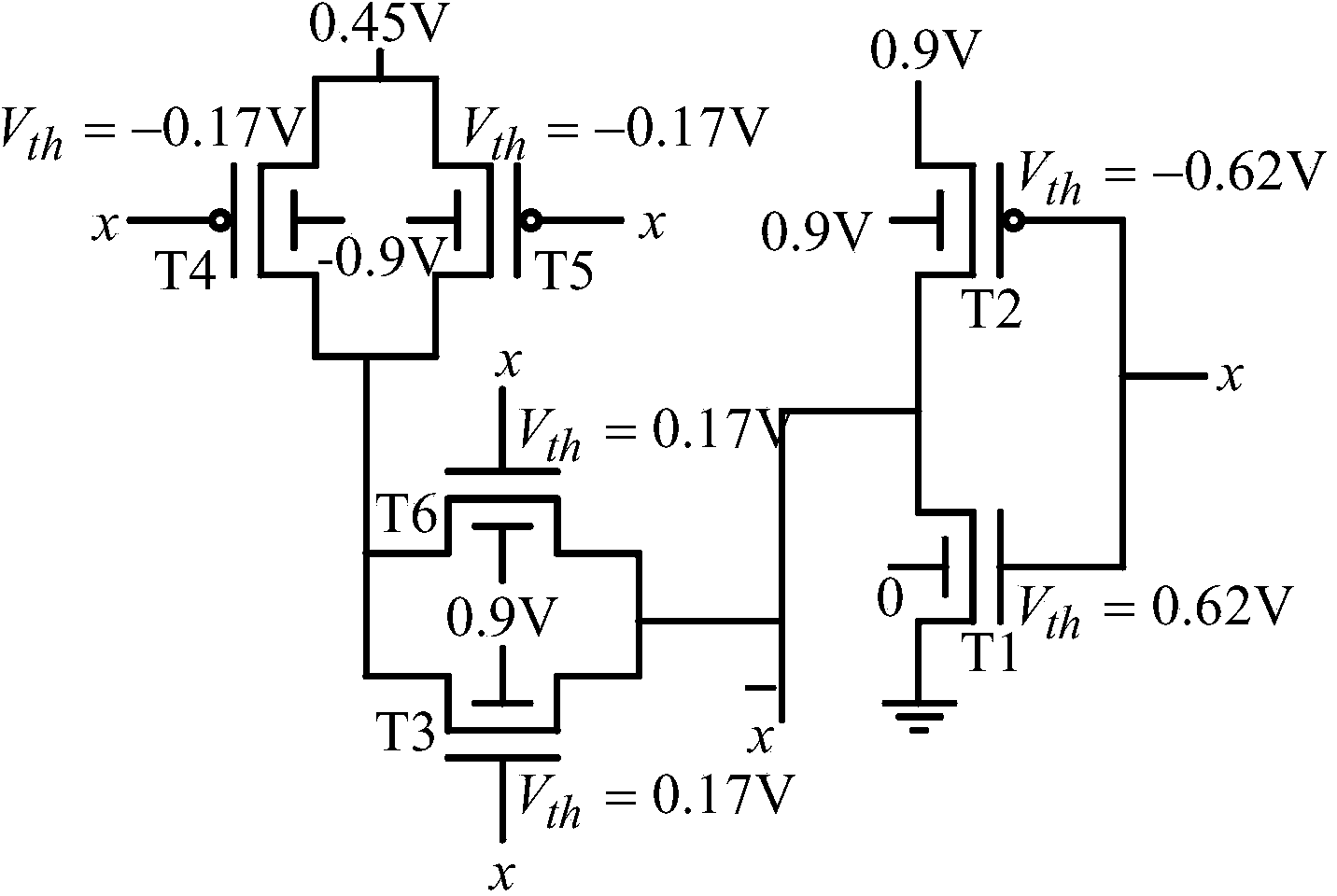

[0013] Example: such as figure 2 As shown, a CNFET-based ternary inverter includes a first CNFET tube T1, a second CNFET tube T2, a third CNFET tube T3, a fourth CNFET tube T4, a fifth CNFET tube T5 and a sixth CNFET tube T6 , the first CNFET tube T1, the third CNFET tube T3 and the sixth CNFET tube T6 are N-type CNFET tubes, the second CNFET tube T2, the fourth CNFET tube T4 and the fifth CNFET tube T5 are P-type CNFET tubes, and the first CNFET tube The threshold voltage of tube T1 is 0.62V, the threshold voltage of the second CNFET tube T2 is -0.62V, the threshold voltage of the third CNFET tube T3 is 0.17V, the threshold voltage of the fourth CNFET tube T4 is 0.17V, and the threshold voltage of the fifth CNFET tube The threshold voltage of T5 is 0.17V, the threshold voltage of the sixth CNFET T6 is -0.17V, the source and base of the first CNFET T1 are grounded, the source of the second CNFET T2, the base of the second CNFET T2 Pole, the base of the third CNFET tube T3 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More