Method for manufacturing semiconductor device

A manufacturing method, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems affecting surface flatness, side wall damage, large porosity, etc., and achieve the effect of ensuring surface flatness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

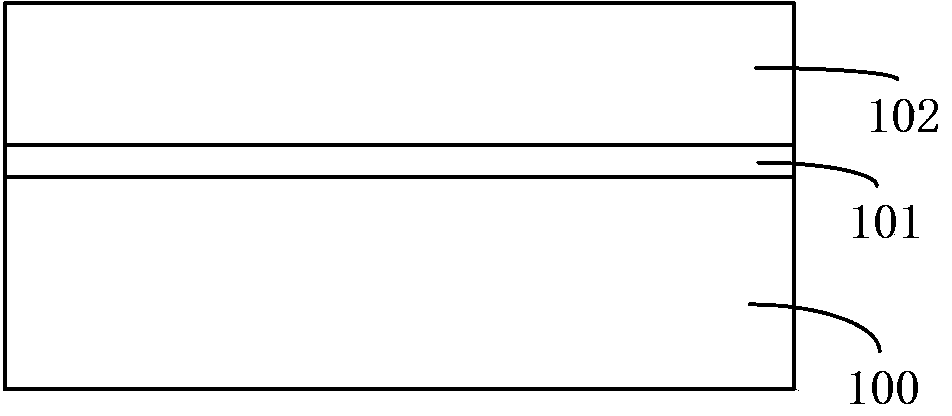

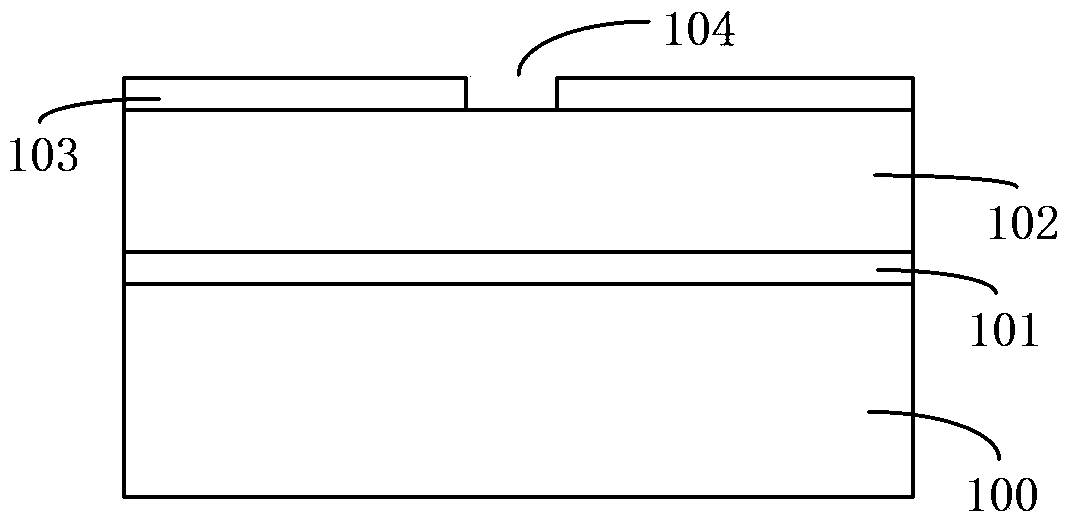

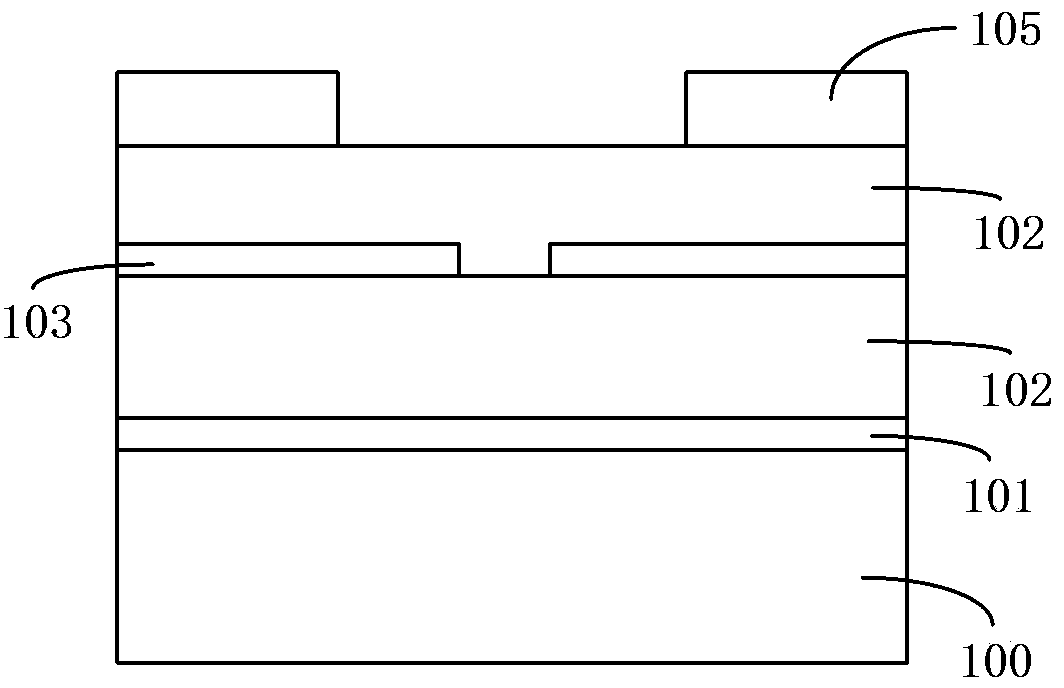

Method used

Image

Examples

Embodiment approach 1

[0039] CF-based 4 and N 2 The etching gas is used to perform the plasma etching; then, a post-etch process is performed to remove the etching residues and impurities formed in the trench 206 and the through hole 207; finally, using CF-based 4 , CO 2 and CO etching gases again perform the plasma etching, wherein the CF 4 The flow rate is 50-500sccm, the N 2 The flow rate is 10-500sccm, the CO 2 The flow rate of CO is 10-500 sccm, the flow rate of CO is 10-500 sccm, the pressure of the two plasma etching is 10-100 mTorr, the power is 100-500 W, and the processing time is 10-60 s.

Embodiment approach 2

[0041] First perform a post-etching process to remove the etching residues and impurities formed in the trench 206 and the through hole 207; then, using CF 4 , CO 2 and CO etching gas to perform the plasma etching, wherein the CF 4 The flow rate is 50-500sccm, the CO 2 The flow rate of the CO is 10-500 sccm, the CO flow rate is 10-500 sccm, the plasma etching pressure is 10-100 mTorr, the power is 100-500 W, and the processing time is 10-60 s.

[0042] So far, all the process steps implemented by the method according to the exemplary embodiment of the present invention are completed. Next, a copper metal diffusion barrier layer and a copper metal layer are sequentially formed in the trench 206 and the through hole 207 . According to the present invention, when etching the etch stop layer under the via hole, the damage to the interlayer dielectric layer is small, and no substance that is difficult to remove by the post-etching process is formed at the bottom of the via hole. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More