Multi-serial port parallel processing framework based on SoC (System on a Chip) FPGA (Field Programmable Gata Array)

A parallel processing and multi-serial port technology, which is applied in the direction of electrical digital data processing and instruments, can solve the problems of increased hardware cost, limited hardware serial interface resources, and long CPU waiting time, so as to reduce design complexity and difficulty and improve Data transmission bandwidth and effect of reducing CPU load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

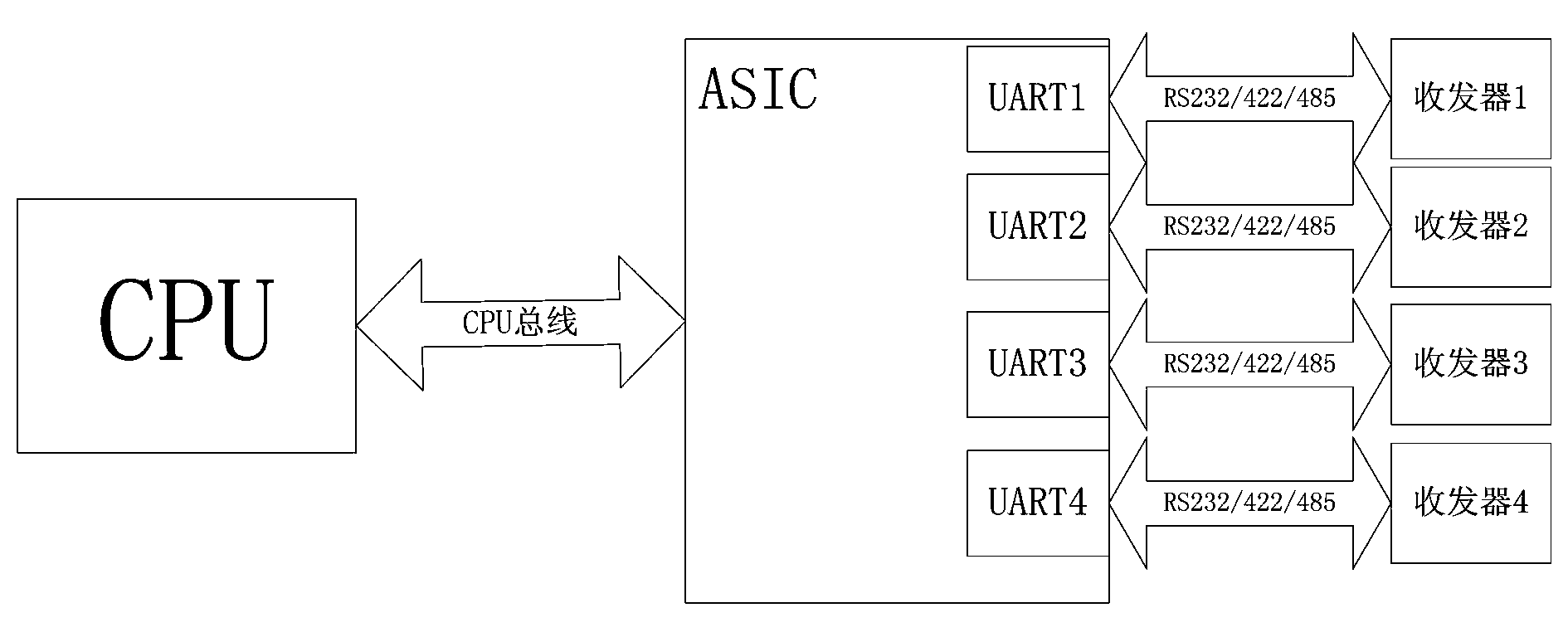

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

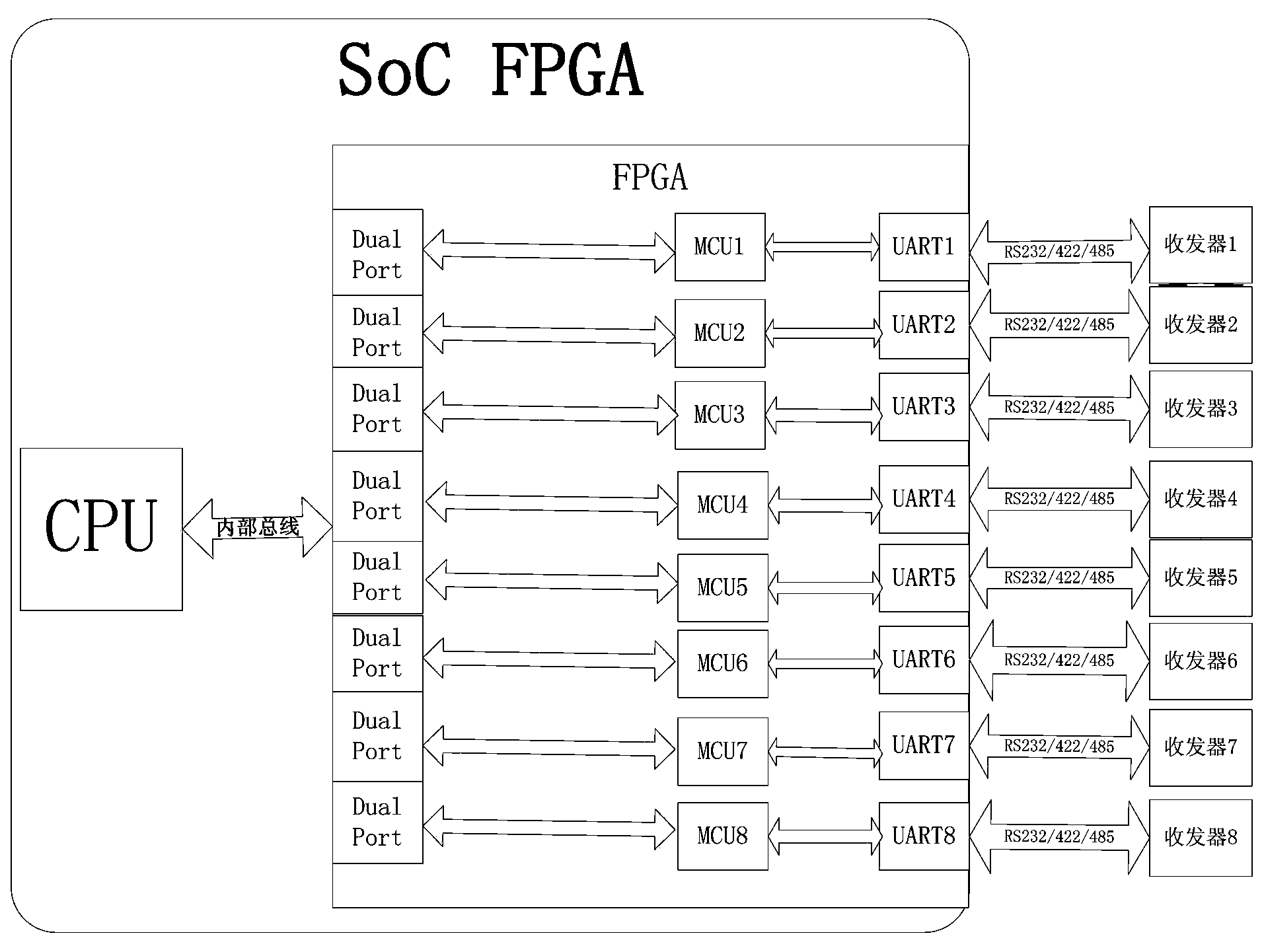

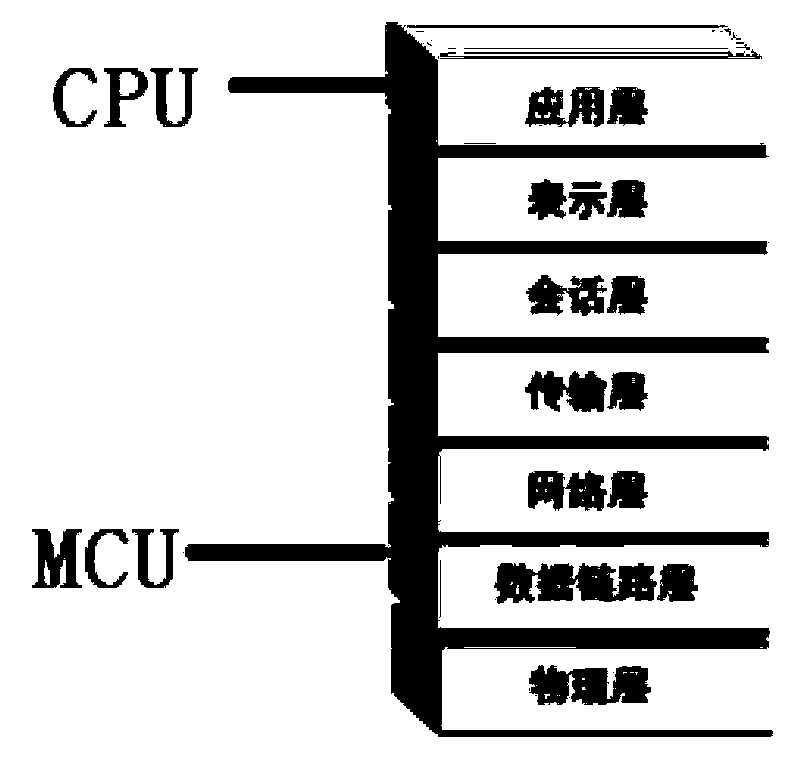

[0013] In order to realize the support of parallel multi-channel serial peripherals, increase the UART bus serial communication bandwidth, reduce the CPU load, improve system integration, and reduce hardware costs, such as figure 2 As shown, the present invention is based on the multi-serial port parallel processing framework of SoCFPGA, comprises transceiver, the SoC FPGA chip that integrated Field Programmable Logic Array FPGA and processor CPU, CPU is connected with FPGA by internal bus, it is characterized in that: described SoC The FPGA in the FPGA chip internally designs a plurality of UART cores and a plurality of coprocessor MCUs corresponding to each UART core through a hardware description language; the FPGA is embedded with a plurality of embedded memories corresponding to each coprocessor MCU, Each embedded memory is configured as a dual-port mode capable of reading and writing operations; the multiple UART cores are connected to multiple corresponding transceivers...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More