Thin film transistor array substrate, preparation method for same and display device of thin film transistor array substrate

A technology of thin film transistors and array substrates, which is applied in the field of liquid crystal display, can solve the problems of complex manufacturing process of thin film transistor array substrates, and achieve the effect of simplifying the manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0045] Based on the same inventive concept, an embodiment of the present invention also provides a method for preparing a thin film transistor array substrate, in which the preparation of the common electrode includes:

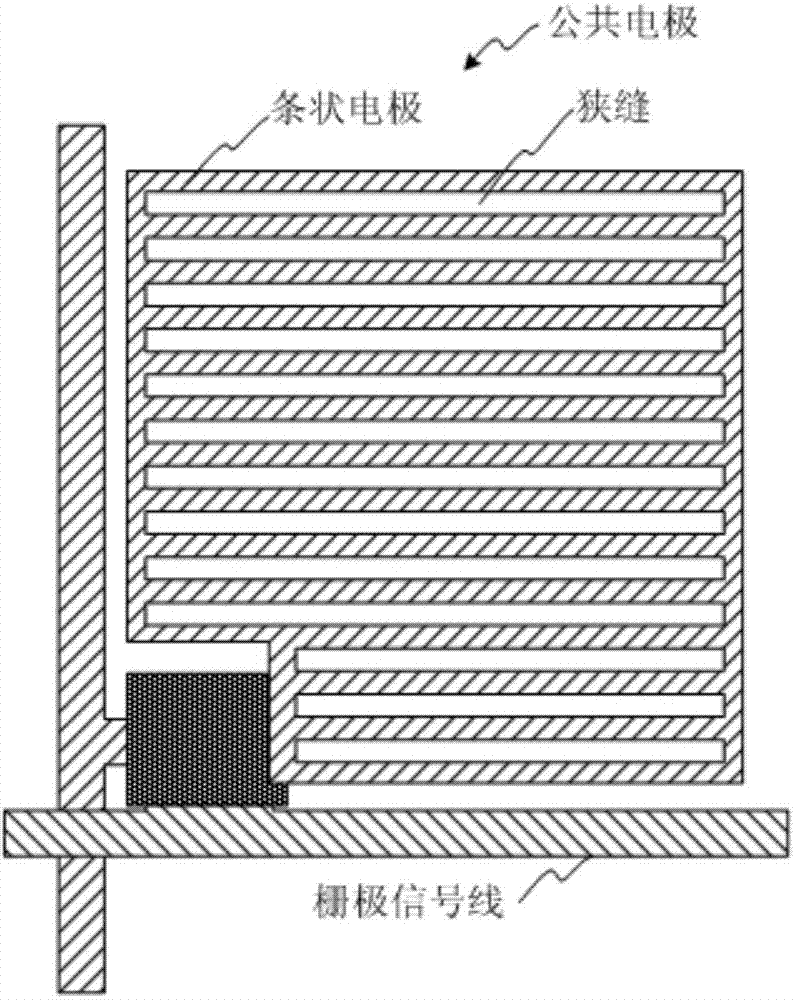

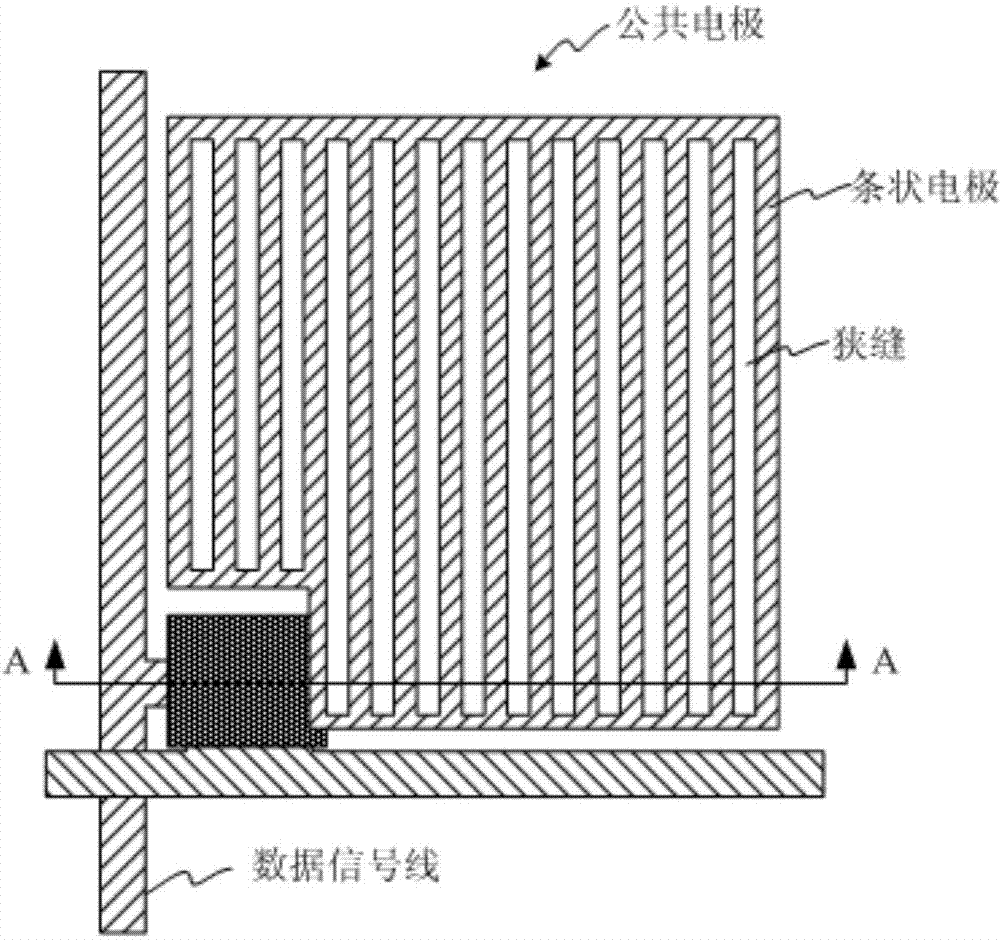

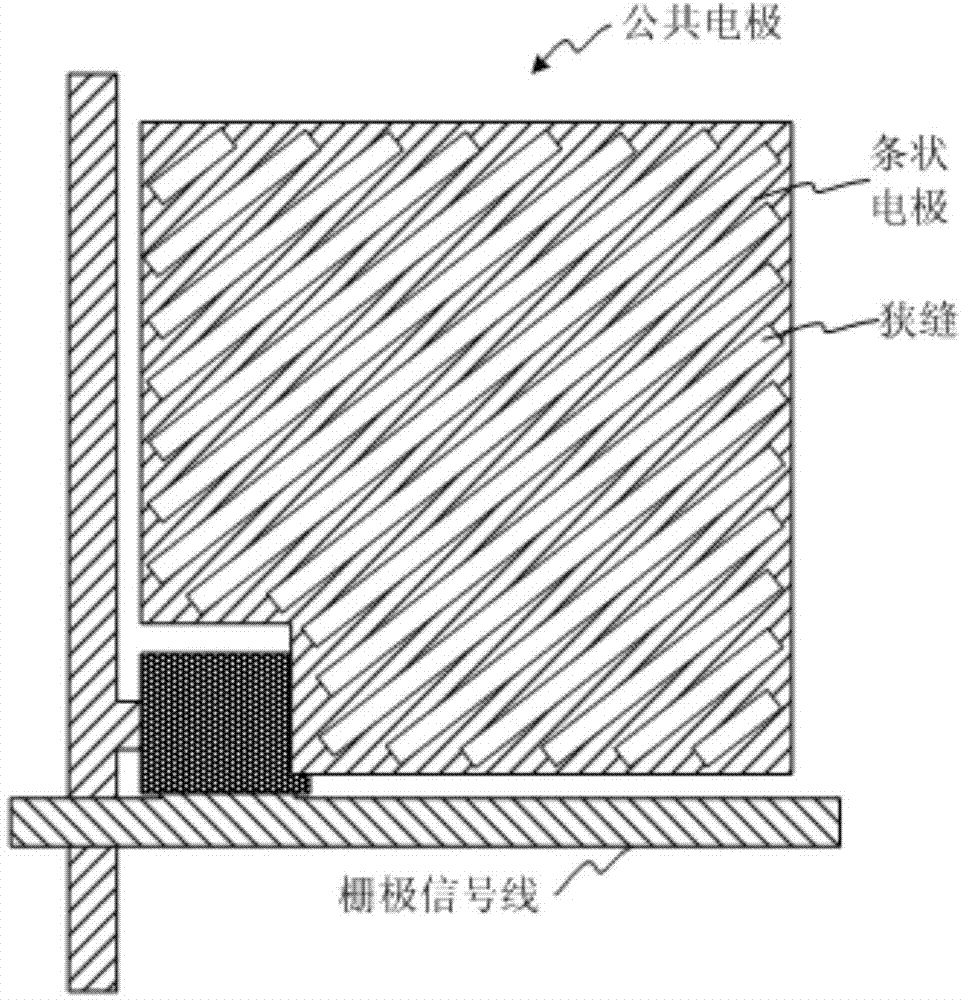

[0046] The pattern of the common electrode with a slit-like structure is formed through a patterning process, wherein the strip-shaped electrodes in the common electrode can reflect the light incident on the strip-shaped electrode, and the slits in the common electrode can transmit the light incident on the strip-shaped electrode. Slits of light.

Embodiment 1

[0048] Embodiment one, see Figure 2A ~ Figure 2G As shown, among them, Figure 2A ~ Figure 2G for Figure 1B In the schematic diagram of the cross-sectional structure in the direction of A-A, the manufacturing process of this embodiment includes the following steps:

[0049] (1) Form the gate 2 on the base substrate 1, such as Figure 2A shown;

[0050] Specifically, a metal layer (such as molybdenum Mo, aluminum Al, etc.) is deposited on a substrate (such as a glass substrate), and a gate pattern is formed by wet etching through the first photolithography technology.

[0051] (2) Forming the gate insulating layer 3 and the active layer 4 on the substrate on which the gate 2 is formed, such as Figure 2B shown;

[0052] Specifically, a gate insulating layer (Gate Insulator, GI) film and an oxide semiconductor film (such as Indium Gallium Zinc Oxide (IGZO) etc.) Secondary photolithography technology, wet etching to form the pattern of the active layer (pattern);

[0053...

Embodiment 2

[0067] Embodiment two, see Figure 3A ~ Figure 3F As shown, among them, Figure 3A ~ Figure 3F for Figure 1B In the schematic diagram of the cross-sectional structure in the direction of A-A, the manufacturing process of this embodiment includes the following steps:

[0068] (1) The gate 2 is formed on the base substrate 1, such as Figure 3A shown;

[0069] Specifically, a metal layer (such as molybdenum Mo, aluminum Al, etc.) is deposited on a substrate (such as a glass substrate), and a gate pattern is formed by wet etching through the first photolithography technology.

[0070] (2) Forming a gate insulating layer 3, an active layer 4, and an etch stop layer 5 on the substrate on which the gate 2 is formed, such as Figure 3B shown;

[0071] Specifically, the GI layer film, the oxide semiconductor film and the etch stop layer film are continuously deposited on the base substrate on which the gate is formed, and the pattern of the etch stop layer is formed by dry etchi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More