Chip packaging method and packaging structure

A technology of chip packaging and packaging structure, which is applied in the direction of electrical components, electrical solid devices, semiconductor/solid device manufacturing, etc., to achieve the effects of improving reliability, improving electrical connection performance, and improving interface quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

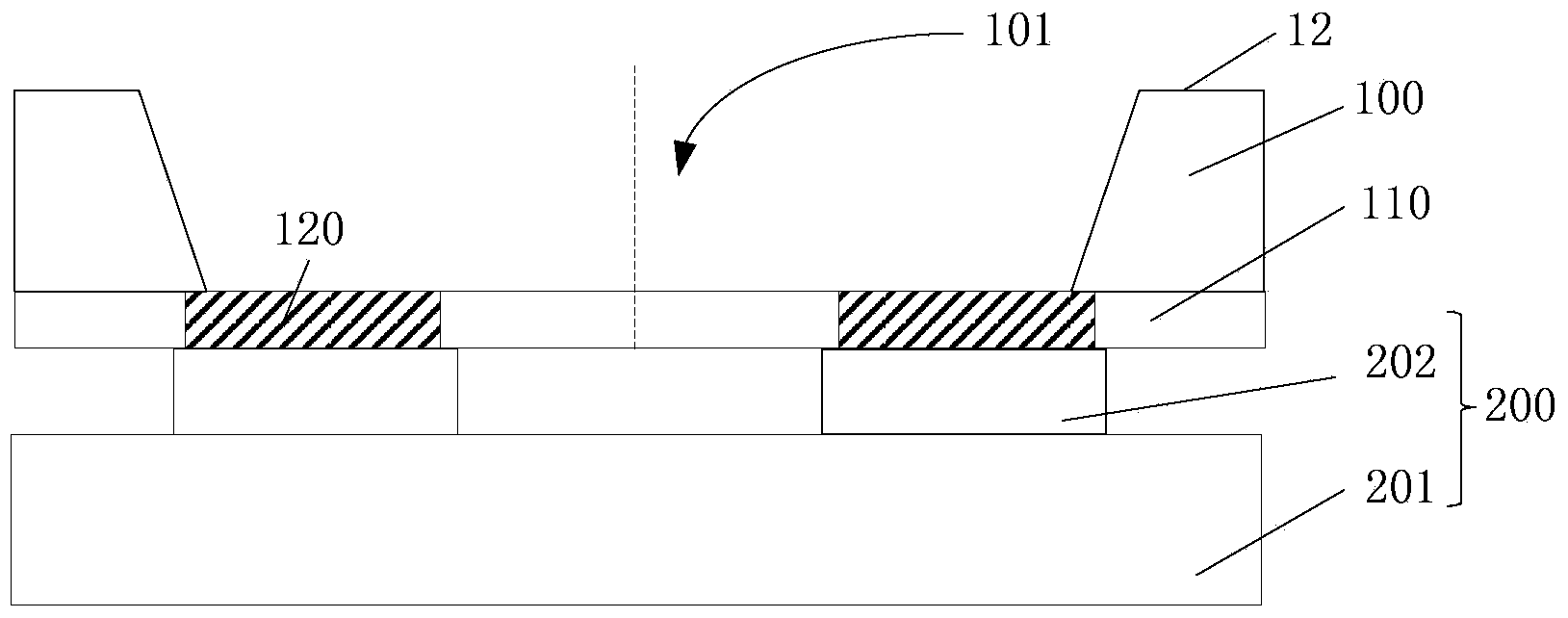

[0034] As mentioned in the background art, the reliability of the packaging structure formed by the existing chip packaging method is low.

[0035] On the one hand, because the thickness of the solder resist layer filled in the groove is relatively large, during the process of thermal curing of the solder resist layer, due to the difference in thermal expansion coefficient between the solder resist layer and the wafer, greater stress will be generated , and passed to the customer layer, generating greater stress in the customer layer; subsequent reflow soldering process is used to form solder balls, and the high temperature in the reflow soldering process will also cause stress in the customer layer. Since the client layer is a complete whole before wafer dicing, the stress in the client layer cannot be completely released. When the chip is cut, the customer layer is no longer a whole. At this time, the thermal curing of the solder mask layer, the residual stress in the solder...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More