CMOS radio frequency power amplifier

A radio frequency power and amplifier technology, applied in the field of semiconductor integrated circuit devices, can solve problems such as difficult design optimization, low gain, and limited improvement in linearity, and achieve the goals of improving gain and noise performance, overall function optimization, and overall function improvement Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

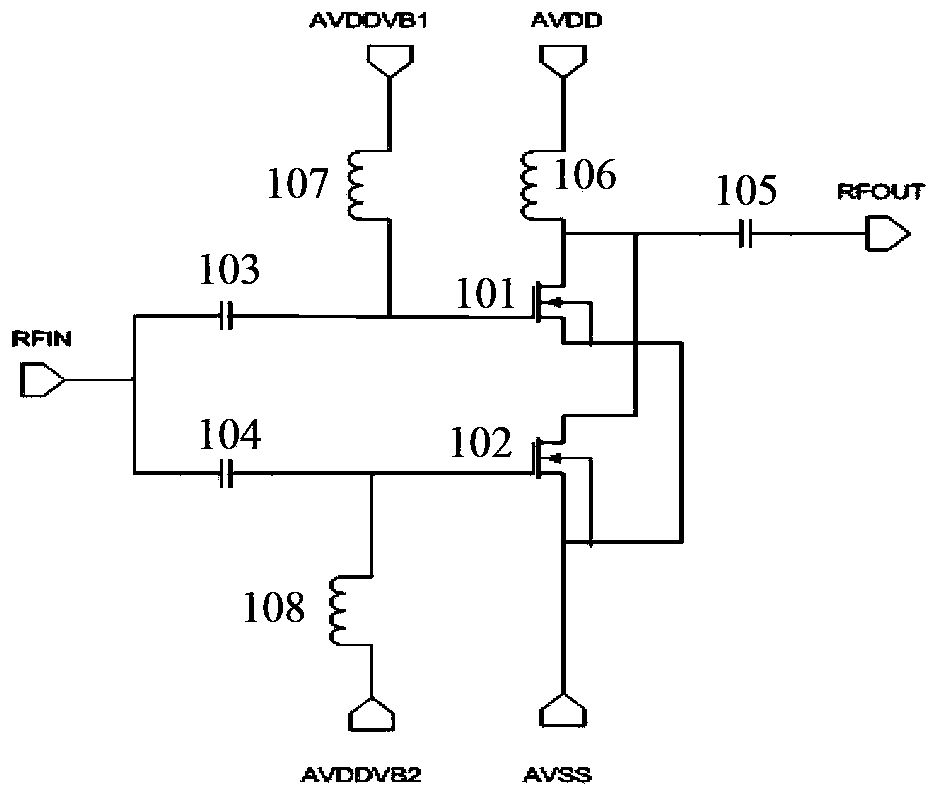

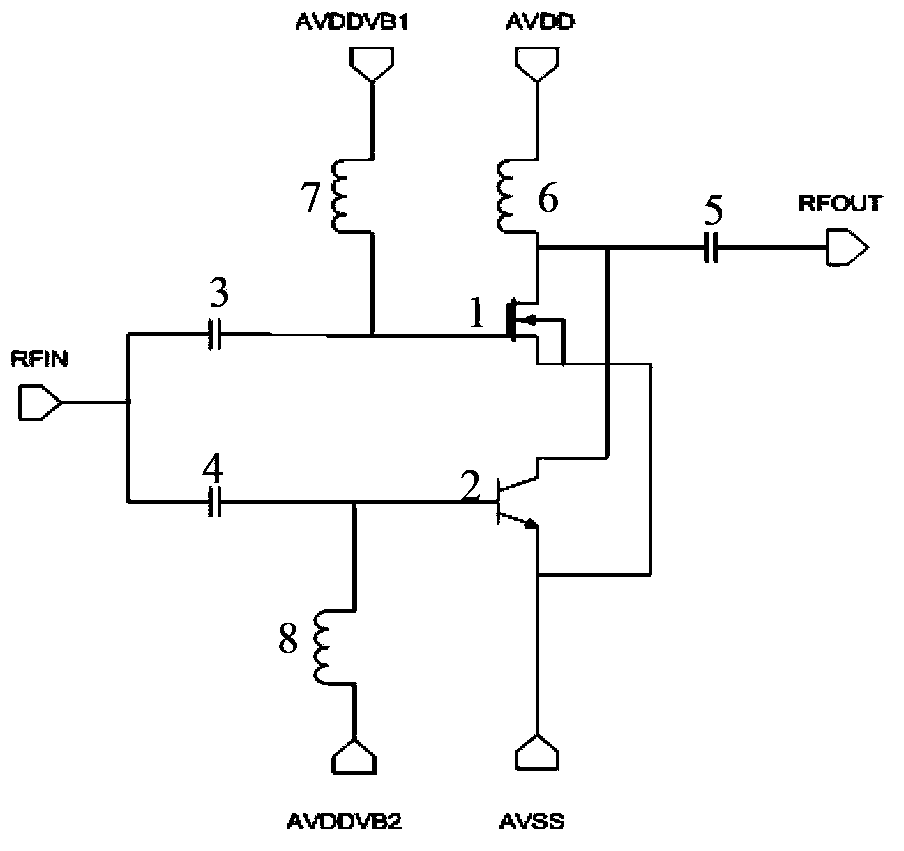

[0016] Such as figure 2 Shown is a schematic structural diagram of a CMOS radio frequency power amplifier in an embodiment of the present invention. The CMOS radio frequency power amplifier in an embodiment of the present invention includes:

[0017] The NMOS transistor 1 is connected in a common source amplifier mode. The gate of the NMOS transistor 1 inputs the radio frequency input signal RFIN through the first capacitor 3, and the drain outputs the radio frequency output signal RFOUT through the third capacitor 5; The gate of the NMOS transistor 1 is connected to the bias capacitor 7, and the bias circuit 7 is connected to the bias voltage source AVDDVB1. The bias circuit 7 of the NMOS transistor 1 makes the MOS transistor work in the saturation region. The drain of the NMOS transistor 1 is connected to a positive power supply AVDD through a first resistor 6, and the source of the NMOS transistor 1 is grounded or a negative power supply AVSS.

[0018] NPN transistor 2, the NPN...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More