A method for semiconductor packaging by utilizing connection pieces to realize connection

A connecting sheet and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problems of increasing process complexity, affecting circuit performance, reducing production costs, etc., to achieve convenient and flexible production and facilitate heat dissipation , the effect of reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

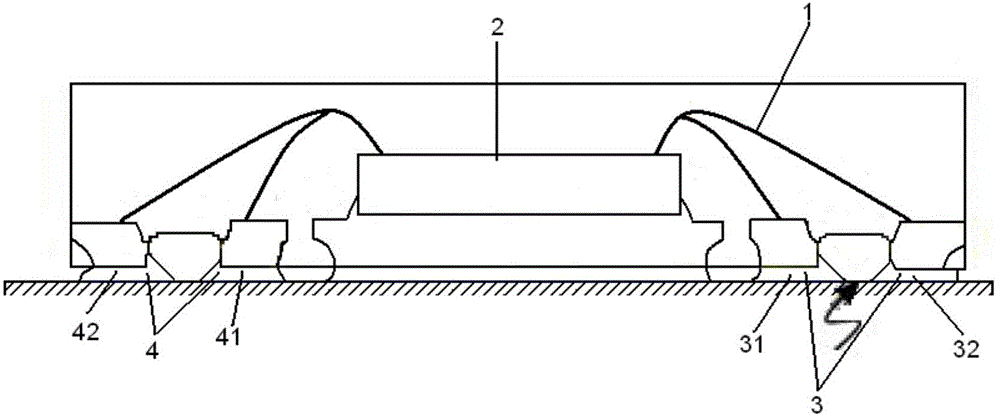

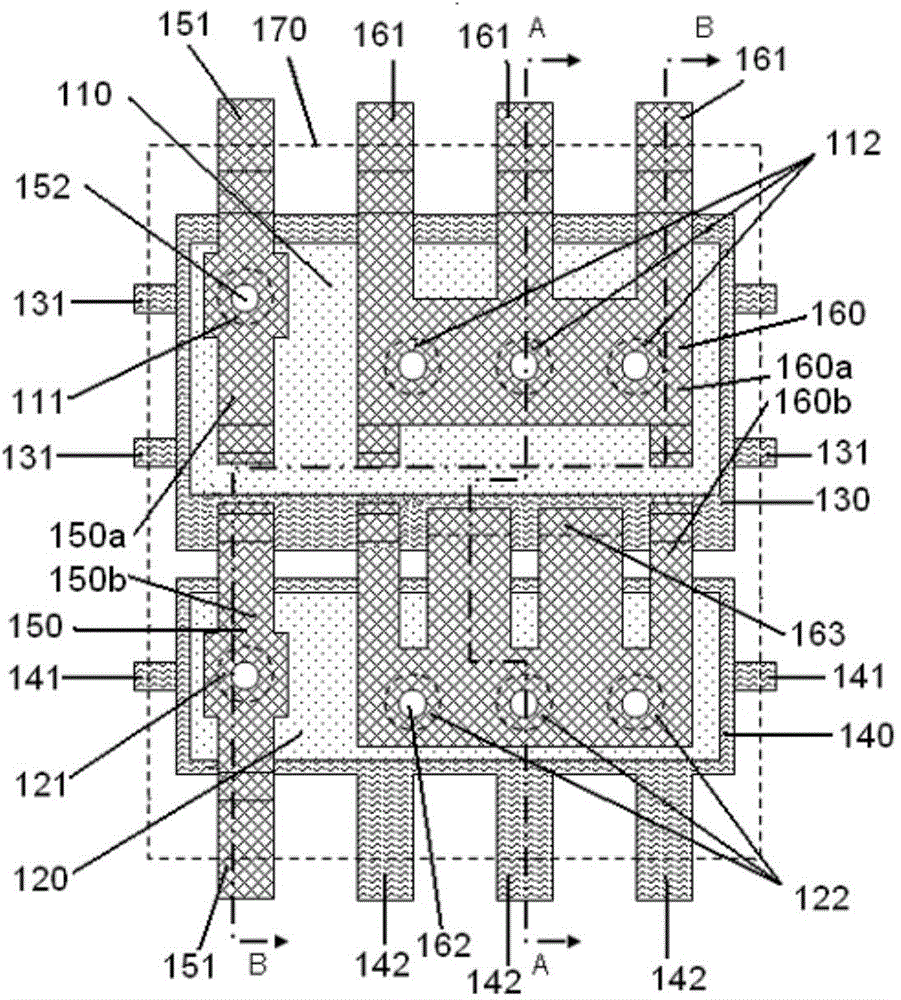

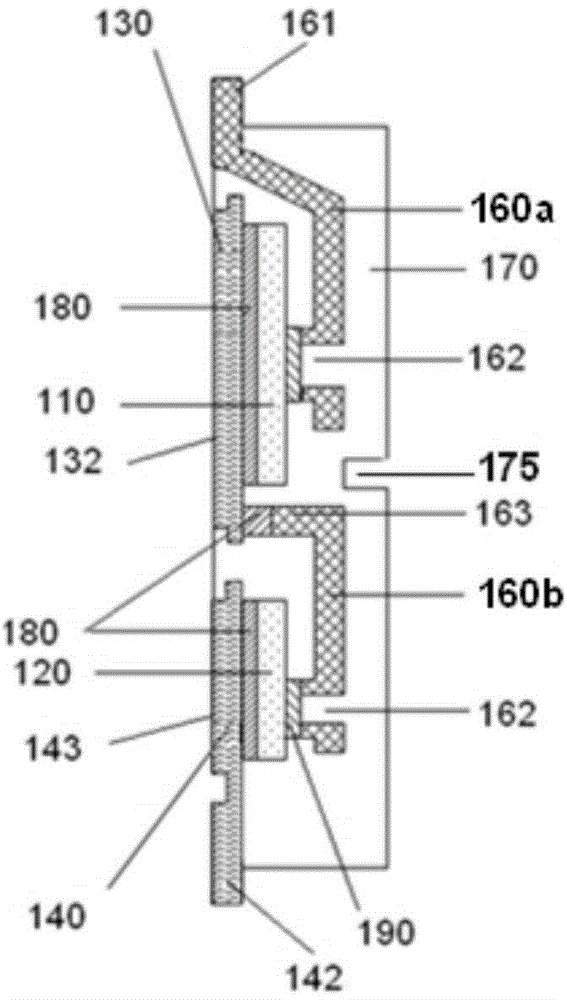

[0088] Embodiment 1. A semiconductor package that is connected by a connecting piece, taking a low-side MOSFET device and a high-side MOSFET co-packaged device as an example, as Figure 2A , Figure 2B and Figure 2CAs shown, it includes first and second two chips, a substrate frame, a plurality of connecting pieces and a plastic package 170 for packaging all the above components; the two chips are respectively the first chip low-side metal-oxide-semiconductor field-effect transistor ( LS MOSFET) 110 and the second chip high-side metal oxide semiconductor field effect transistor (HS MOSFET) 120, the top contact regions of LS MOSFET 110 are gate contact region 111 and source contact region 112 respectively, and the bottom contact region is drain contact region (not shown in the figure), the top contact regions of the HS MOSFET 120 are the gate contact region 121 and the source contact region 122 respectively, and the bottom contact region thereof is the drain contact region (n...

Embodiment 2

[0092] Embodiment 2. A semiconductor package that is connected by a connecting piece, taking a low-side MOSFET device and a high-side MOSFET co-packaged device as an example, as Figure 8A , Figure 8B and Figure 8C As shown, it includes two chips, a substrate frame, a plurality of connecting sheets and a plastic package 270 for encapsulating all the above components; the two chips are the first chip low-side metal-oxide-semiconductor field-effect transistor (LS MOSFET) 210 and The top contact regions of the second chip high-side metal oxide semiconductor field effect transistor (HS MOSFET) 220 and LS MOSFET 210 are gate contact region 211 and source contact region 212 respectively, and their bottom contact regions are drain contact regions (not shown in the figure ), the top contact regions of the HS MOSFET 220 are the gate contact region 221 and the source contact region 222 respectively, and the bottom contact region is the drain contact region (not shown in the figure); ...

Embodiment 3

[0094] Embodiment 3. A semiconductor package that is connected by a connecting piece, taking a low-side MOSFET device and a high-side MOSFET co-packaged device as an example, as Figure 13A , Figure 13B and Figure 13CAs shown, it includes two chips, a substrate frame, a connecting sheet and a plastic package 370 for encapsulating all the above components; the two chips are respectively a low-side metal oxide semiconductor field effect transistor (LS MOSFET) 310 and a high-side metal oxide HS MOSFET 320, the top contact regions of LS MOSFET 310 are gate contact region 311 and source contact region 312 respectively, and the bottom contact region is drain contact region (not shown in the figure), the top contact region of HS MOSFET 320 The contact regions are gate contact region 321 and source contact region 322 respectively, and the bottom contact region is a drain contact region (not shown in the figure); a substrate frame, which includes a substrate frame first chip holder ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More