Low-temperature polycrystalline silicon thin film transistor, array substrate and manufacturing method of array substrate

A thin-film transistor and low-temperature polysilicon technology, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, and electric solid-state devices, can solve the problems of low-temperature polysilicon manufacturing process, low yield rate, and poor performance of thin-film transistors. Effects of defects and defects, performance improvement, and manufacturing process simplification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] Embodiments of the present invention provide a low-temperature polysilicon thin film transistor, an array substrate and a manufacturing method thereof, which are used to simplify the manufacturing process of the thin film transistor and improve the performance of the thin film transistor.

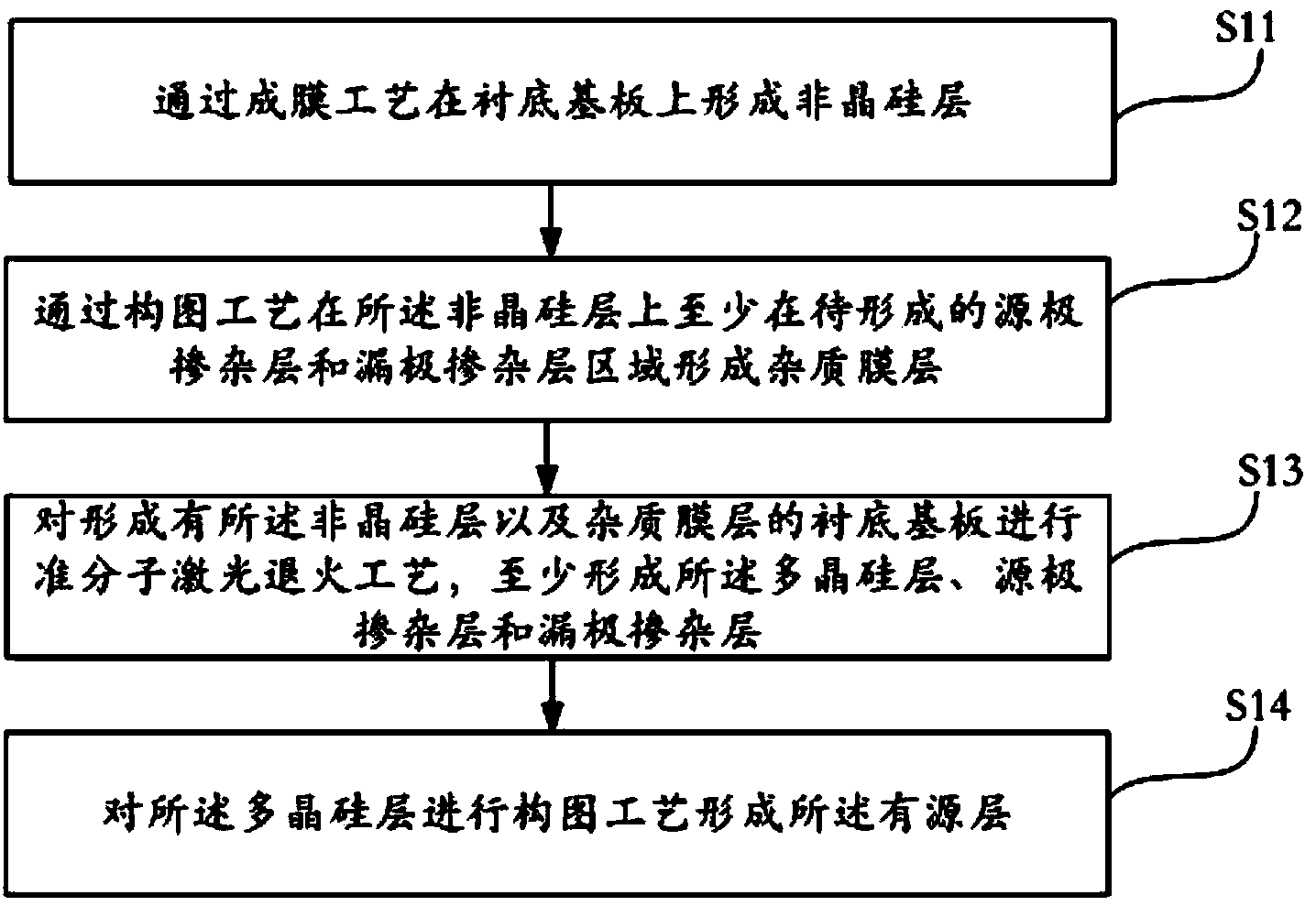

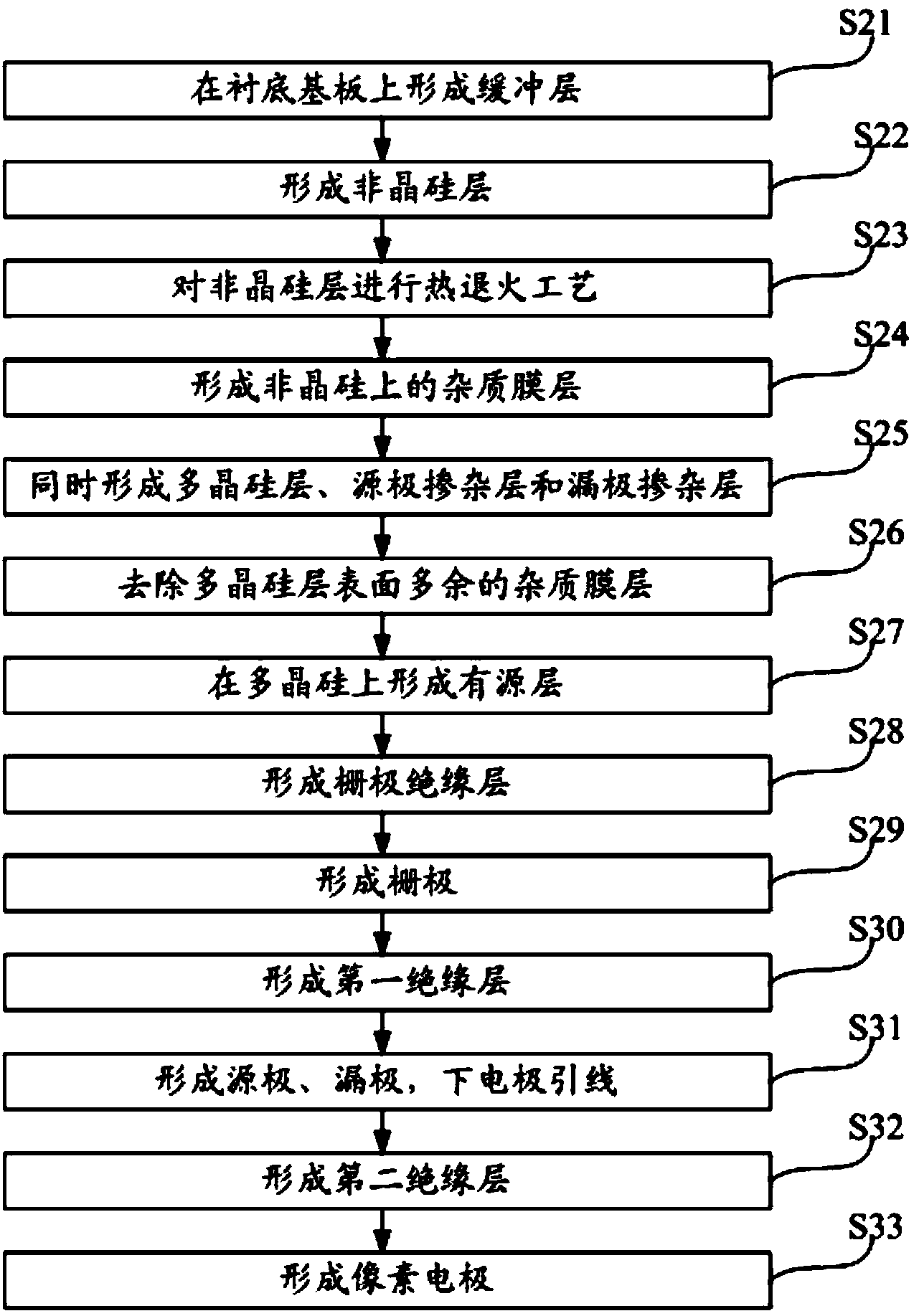

[0045] In the manufacturing method of the low-temperature polysilicon thin film transistor provided by the embodiment of the present invention, the source doped layer and the drain doped layer are simultaneously formed during the process of forming the polysilicon layer from the amorphous silicon layer, which simplifies the manufacturing process. The source doped layer and the drain doped layer are realized by doping in the polysilicon layer. In the present invention, the formation of doping ions in the polysilicon layer is achieved through excimer laser annealing, which avoids related defects and bad phenomena of thin film transistors caused by ion implantation, and improves the perf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More