Satellite navigation three-dimensional chip and manufacture method thereof

A three-dimensional chip and satellite navigation technology, applied in the field of satellite navigation, can solve the problems of insufficient connection between the radio frequency chip and the core algorithm of the baseband processing chip, restricting the rapid development of the Beidou satellite navigation industry, and high size and power consumption development costs, and achieves a reduction of two Secondary development difficulty, area and volume reduction, and the effect of increasing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example 3

[0040] refer to figure 2 , showing the flow of the three-dimensional chip packaging method according to the first embodiment of the present invention, specifically including:

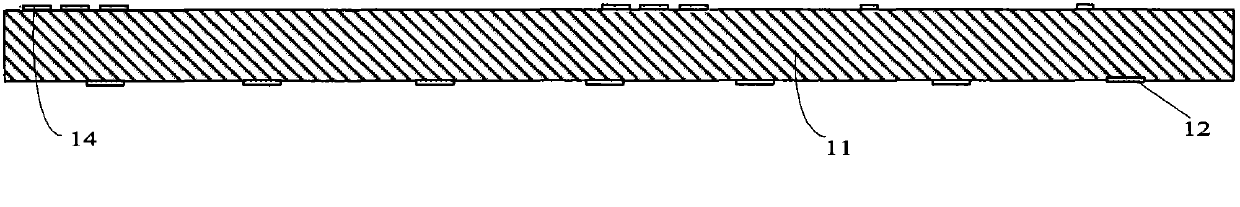

[0041] Step S101: fixing the first-layer functional chip to a designated position reserved on the substrate;

[0042] In this preferred embodiment, the surface of the first-level chip is pasted on the designated position reserved on the substrate with a placement machine, and then the substrate after the chip is mounted is cured at a high temperature, so that a stable connection is formed between the chip and the substrate;

[0043] Step S102: establishing an electrical connection between the functional chip and the substrate;

[0044] In this preferred embodiment, the pads of the first-level functional chip are led out to the corresponding lead pad positions on the substrate through a wire bonding machine, so as to realize the electrical connection between the first-level functional chip and the subs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More