A kind of semiconductor device and its manufacturing method

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as affecting the performance of semiconductor devices and easily generating leakage current, and achieve the effect of improving performance and avoiding leakage current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

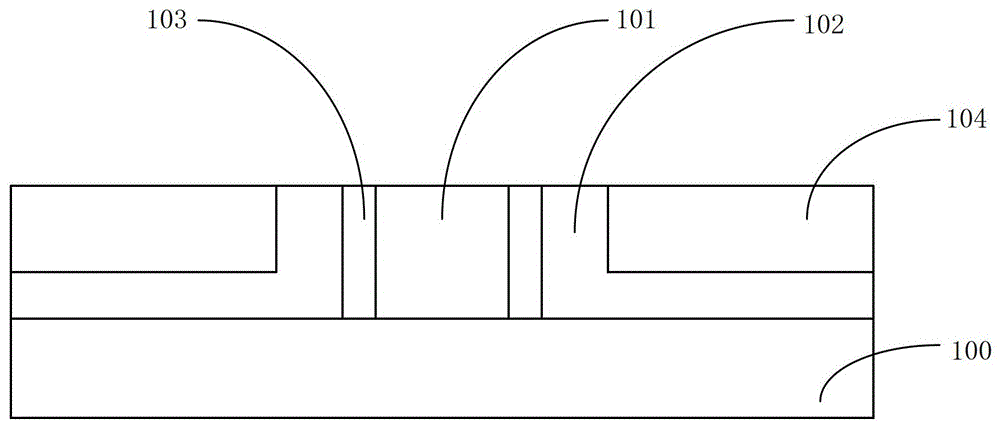

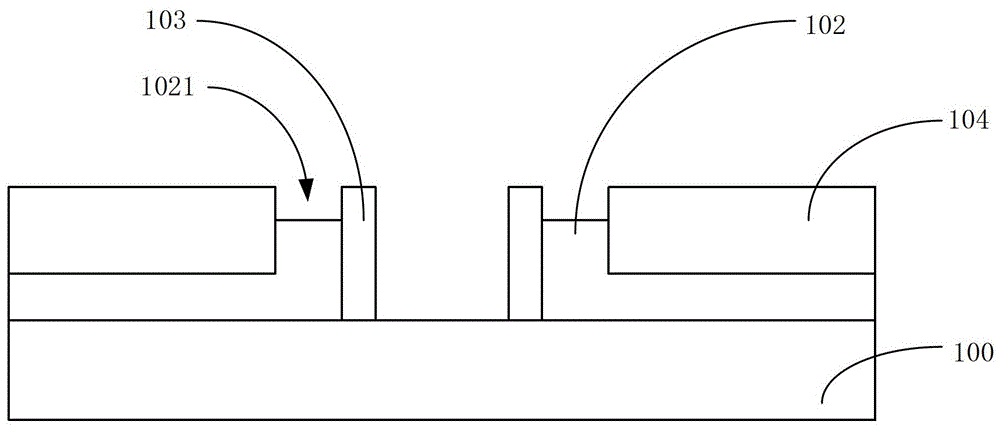

[0047] Below, refer to Figure 2A-Figure 2F and image 3 , to describe the detailed steps of an exemplary method of the semiconductor device manufacturing method proposed by the present invention. in, Figure 2A-Figure 2F A schematic cross-sectional view of the graphics formed in each step of the manufacturing method of the semiconductor device proposed by the present invention; image 3 It is a flowchart of a manufacturing method of a semiconductor device proposed by the present invention.

[0048] The method for manufacturing a semiconductor device according to an embodiment of the present invention includes the following steps:

[0049] Step 1: Provide a semiconductor substrate 200, on which a dummy gate 201, a contact etch stop layer (CESL) 202, a gate sidewall 203 and an interlayer dielectric layer 204 are formed, such as Figure 2A shown. Of course, the semiconductor substrate 200 may also include STI, source / drain and other structures (not shown in the figure), whi...

Embodiment 2

[0080] An embodiment of the present invention provides a semiconductor device, such as Figure 2F As shown, the semiconductor device includes a semiconductor substrate 200, a metal gate 206 located on the semiconductor substrate 200, a contact hole etch barrier layer 202, a gate sidewall 203 and an interlayer dielectric layer 204, wherein the The semiconductor device further includes: a protection layer 2051 located above the contact hole etch barrier layer 202 , and the protection layer 2051 is on the same plane as the interlayer dielectric layer 204 .

[0081] Wherein, the protection layer 2051 and the interlayer dielectric layer 204 are on the same plane, which refers to the case where the semiconductor substrate 200 is placed horizontally.

[0082] Further, the thickness of the protective layer 2051 is 3nm-30nm.

[0083] Further, the material of the protection layer 2051 is silicon oxide.

[0084] The semiconductor device provided by the embodiment of the present inventi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More