Sampling clock generation circuit for multichannel time interleaving analog-digital converter

An analog-to-digital converter and a technology for generating circuits, applied in the direction of analog/digital conversion calibration/testing, etc., can solve the problems of increasing multi-channel sampling clock error, affecting phase calibration accuracy, reducing conversion accuracy, etc., to reduce the cost of hardware , the effect of eliminating errors and improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

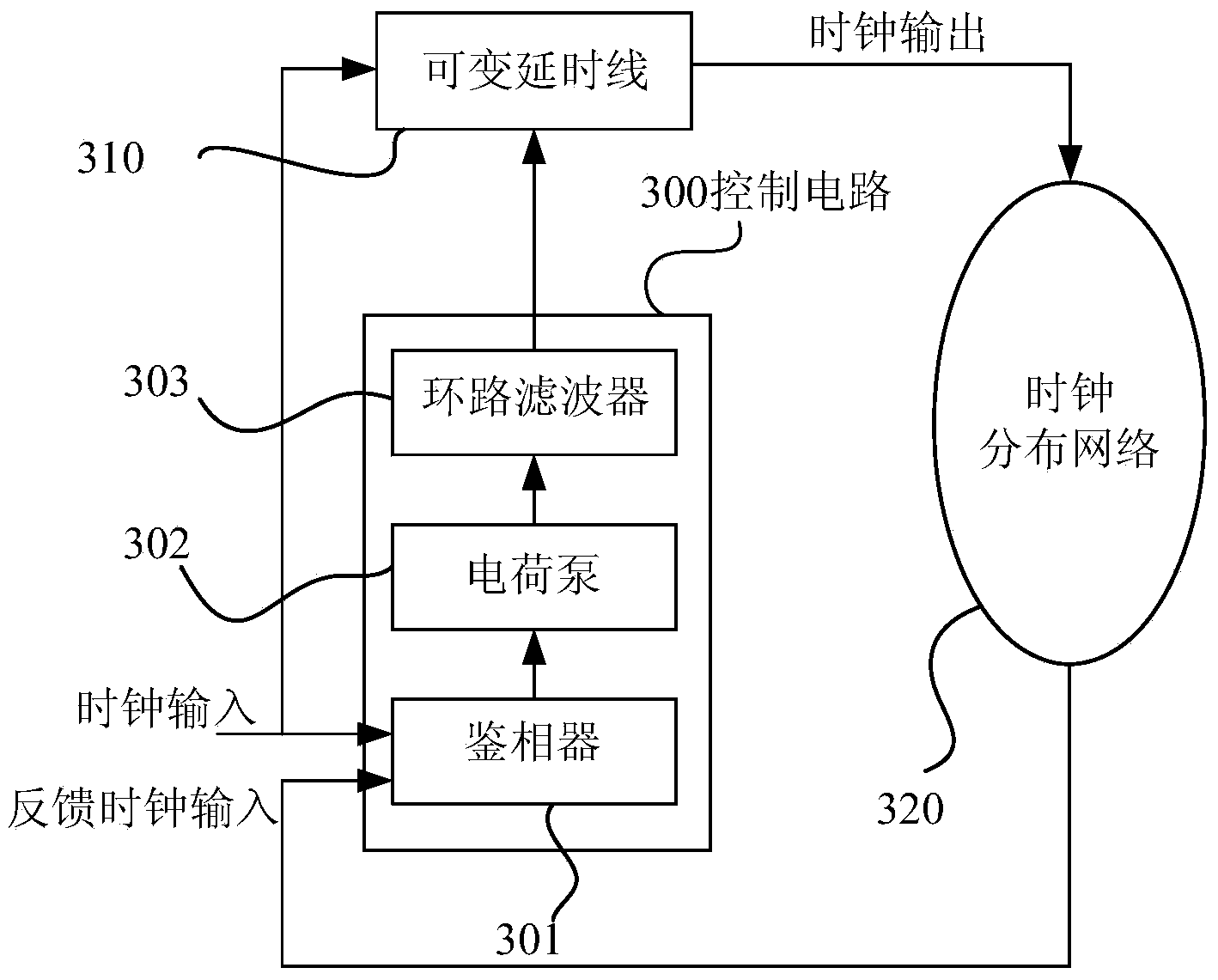

[0041] Such as Figure 4 Shown is a schematic structural diagram of the sampling clock generation circuit of the present invention. It can be seen from the figure that the sampling clock generation circuit of the present invention is composed of a multi-phase clock generation module 400 , a duty cycle recovery circuit 410 , and a channel selection module 420 . The multi-phase clock generating module 400 generates multi-phase clock signals required by the multi-channel digital-to-analog converter, and at the same time compensates phase errors of the multi-phase clock signals to ensure the accuracy of sampling clocks between channels of the digital-to-analog converter. The duty cycle recovery circuit 410 is used to perform edge synchronization operation on the multi-phase clock generated by the multi-phase clock generation module and the input glo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More