Transistor based on multi-top-gate structure

A transistor and top-gate technology, applied in the field of microelectronics, can solve problems such as difficulty in guaranteeing the yield of logic circuits and complicated manufacturing process, and achieve the effects of volume reduction, production cost reduction, and number reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

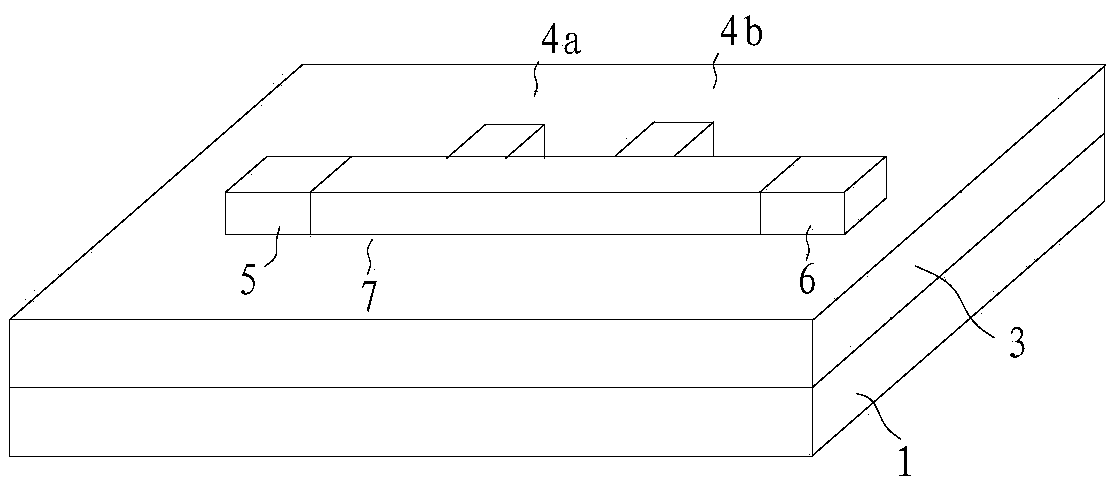

[0088] Such as figure 1 As shown, a transistor based on a multi-top gate structure includes a substrate 1 and a dielectric layer 3 on the substrate 1. A source region 5 and a drain region 6 are arranged on the dielectric layer 3, and are connected to the source region 5 and the drain region. In the channel region 7 between 6, two top gates are respectively the first top gate 4a and the second top gate 4b, both of which are connected to the channel region 7. The first top gate 4a is used as an output pole, and the second top gate 4b is used as an input pole.

[0089] Such as figure 2 As shown, the first top gate 4a and the second top gate 4b are connected to the channel region 7, and the channel region 7 can be extended to form a ledge, and the first top gate 4a and the second top gate 4b are connected to the channel through the ledge. District 7 is connected.

[0090] The substrate 1 is made of glass with a single surface as a conductive layer, the conductive layer is made...

Embodiment 2

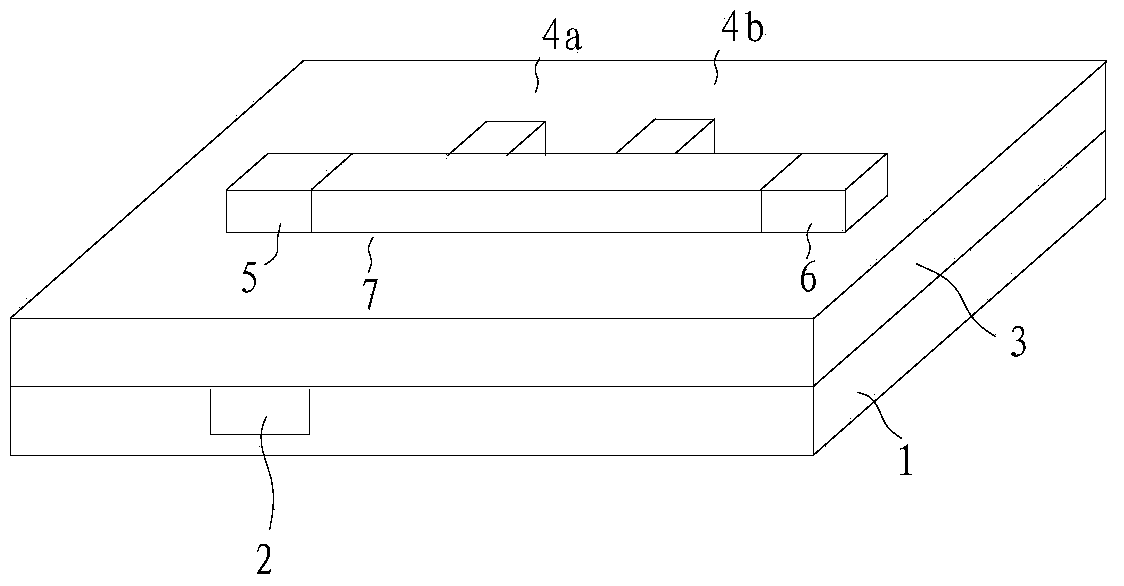

[0098] Such as image 3 As shown, a transistor based on a multi-top gate structure includes a substrate 1 and a dielectric layer 3 on the substrate 1. A source region 5 and a drain region 6 are arranged on the dielectric layer 3, and are connected to the source region 5 and the drain region. The channel region 7 between 6, the two top gates, and the bottom gate 2 coupled with the two top gates. The two top gates are respectively a first top gate 4 a and a second top gate 4 b, both of which are connected to the channel region 7 . The bottom gate 2 is located between the substrate 1 and the dielectric layer 3, the bottom gate 2 is distributed in a local area on the substrate 1, and the substrate 1 is provided with an accommodation groove corresponding to the position of the bottom gate 2, and the area of the bottom gate 2 can be controlled at least channel region 7. If there is no bottom gate, add a top gate outside the channel to replace the bottom gate to regulate the chan...

Embodiment 3

[0108] Such as Figure 4 The shown transistor based on the multi-top gate structure includes a substrate 1 and a dielectric layer 3 on the substrate 1. A source region 5 and a drain region 6 are arranged on the dielectric layer 3, and are connected between the source region 5 and the drain region 6. The channel region 7 between them, and the three top gates are the first top gate 4a, the second top gate 4b and the third top gate 4c respectively, wherein the first top gate 4a, the second top gate 4b and the first top gate The three top gates 4c are all connected to the channel region 7, and the substrate 1 also serves as the bottom gate.

[0109] The substrate 1 is made of glass with a single surface as a conductive layer, the conductive layer is made of indium tin oxide (ITO) and the dielectric layer 3 is bonded, the dielectric layer 3 is made of silicon dioxide, and the physical thickness of the dielectric layer 3 is 0.5 μm; the source region 5. The drain region 6, the first...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More