Method for optimizing shape of ion implantation region

A technology of ion implantation and area, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems affecting the quality of ion implantation and the morphology of ion implantation area, corrosion damage of substrate surface, reducing device quality and yield, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

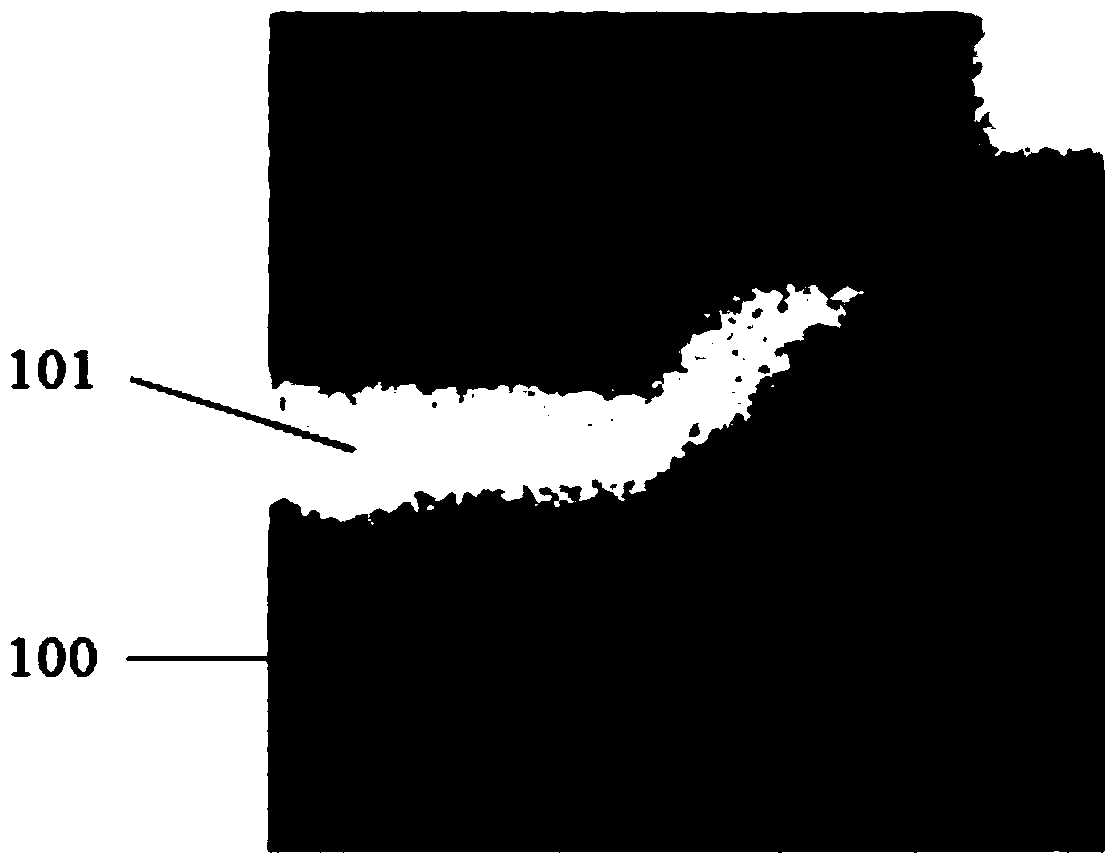

[0042] The following will be combined with Figure 3-9 The method for optimizing the morphology of the ion implantation region of the present invention will be further described in detail with specific embodiments. in, image 3 It is a schematic flow chart of the method for optimizing the morphology of the ion implantation region of the present invention, Figure 4-9It is a schematic diagram of the structure formed by each preparation step of the method for optimizing the morphology of the ion implantation region according to the first embodiment of the present invention. It should be noted that the drawings are all in a very simplified form, using imprecise scales, and are only used to facilitate and clearly achieve the purpose of assisting in describing the present embodiment.

[0043] see image 3 , the method for optimizing the morphology of the ion implantation region of the present invention, comprising:

[0044] Step S01: See Figure 4 , providing a semiconductor d...

Embodiment 2

[0069] The method for optimizing the morphology of the ion implantation region in the second embodiment can be the same as that in the first embodiment; the difference with respect to the first embodiment is that the etching by-products in the second embodiment remain on the surface of the original oxide layer at the top of the gate , or there are residues on both the surface of the original oxide layer on the top of the gate and the surface of the original oxide layer on the substrate of the semiconductor device. The method for removing the residual oxide is the same as the first embodiment, no matter where the etching by-products remain on the original oxide layer, the removal process is still to remove the original oxide layer on the top of the gate and the surface of the semiconductor device substrate. Then, a new oxide layer is grown on the entire semiconductor device substrate, and the new oxide layer covers the tops of the gate and sidewalls, the sidewalls of the sidewal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More