Semiconductor device manufacturing method

A device manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as rough edges, inability to integrate large-scale, and inability to narrow the width of nano-bands, and achieve high integration, suitable for For large-scale integration, low edge roughness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Hereinafter, the present invention is described by means of specific embodiments shown in the drawings. It should be understood, however, that these descriptions are exemplary only and are not intended to limit the scope of the present invention. Also, in the following description, descriptions of well-known structures and techniques are omitted to avoid unnecessarily obscuring the concept of the present invention.

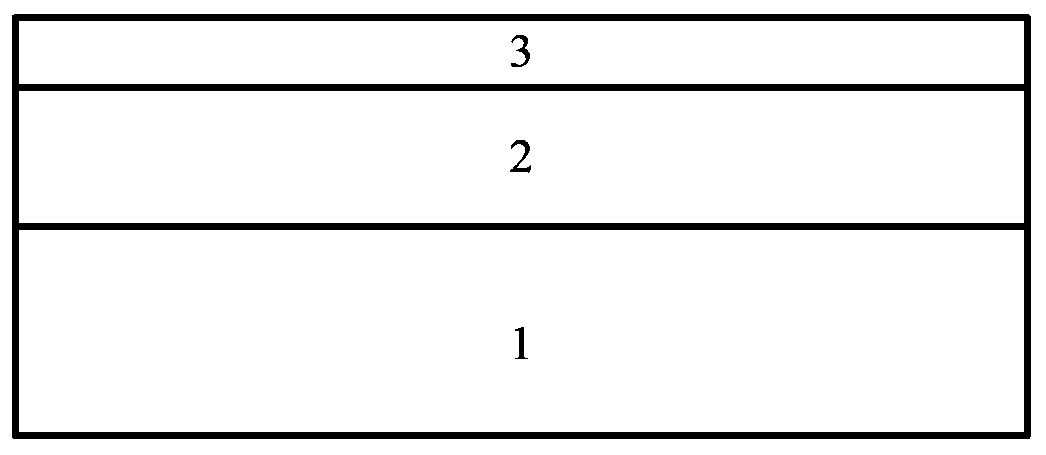

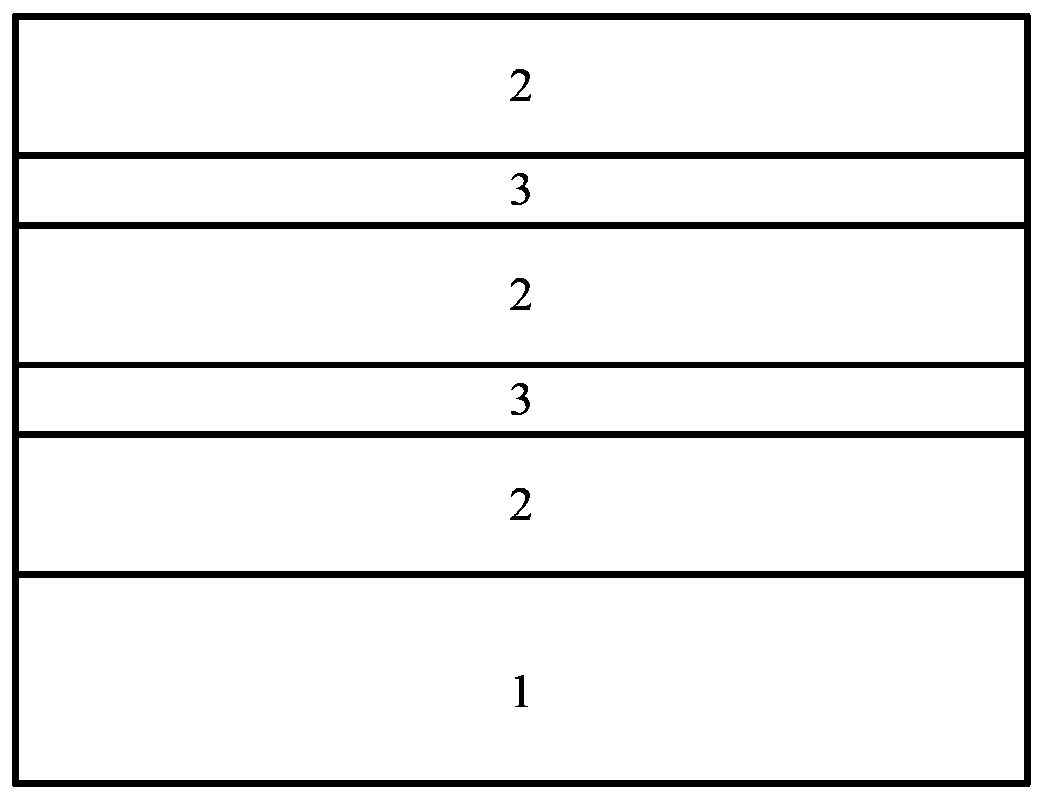

[0026] The invention provides a method for manufacturing a semiconductor device, which uses a lamination method to self-limit the growth of graphene nanobelts. For the manufacturing process, see the appended Figure 1-7 .

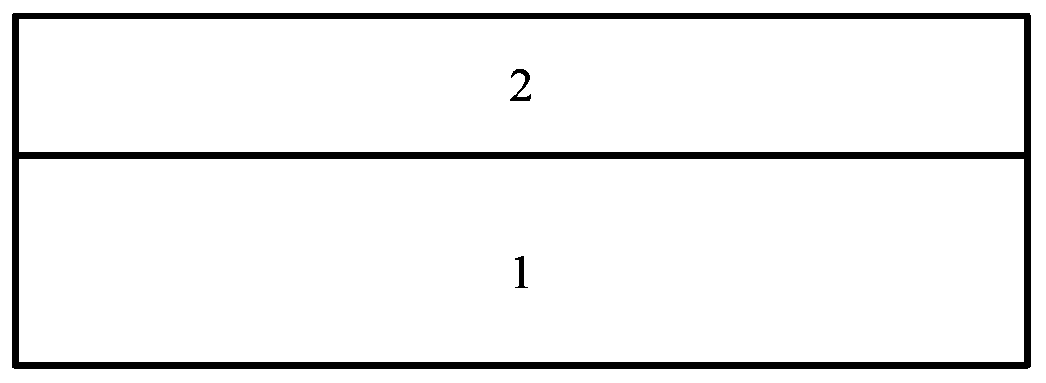

[0027] First, see attached figure 1 , providing a substrate 1 . The substrate 1 in the present invention can be a substrate processed by at least one process, and its material can be semiconductor materials such as silicon, gallium nitride, and silicon germanium, or other insulating media such as glass, and the selection of specific m...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More