Patents

Literature

55results about How to "Reduce edge roughness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

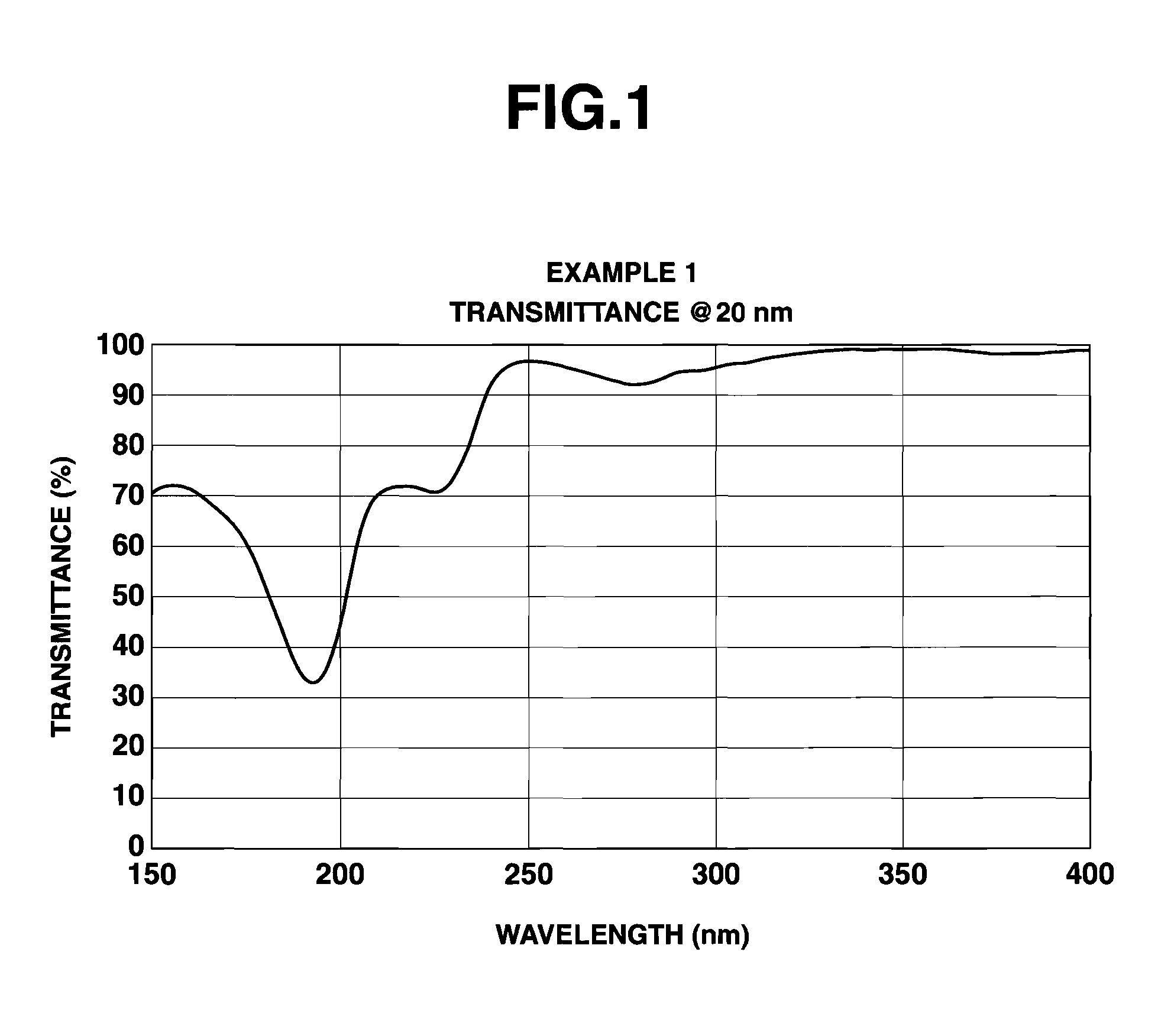

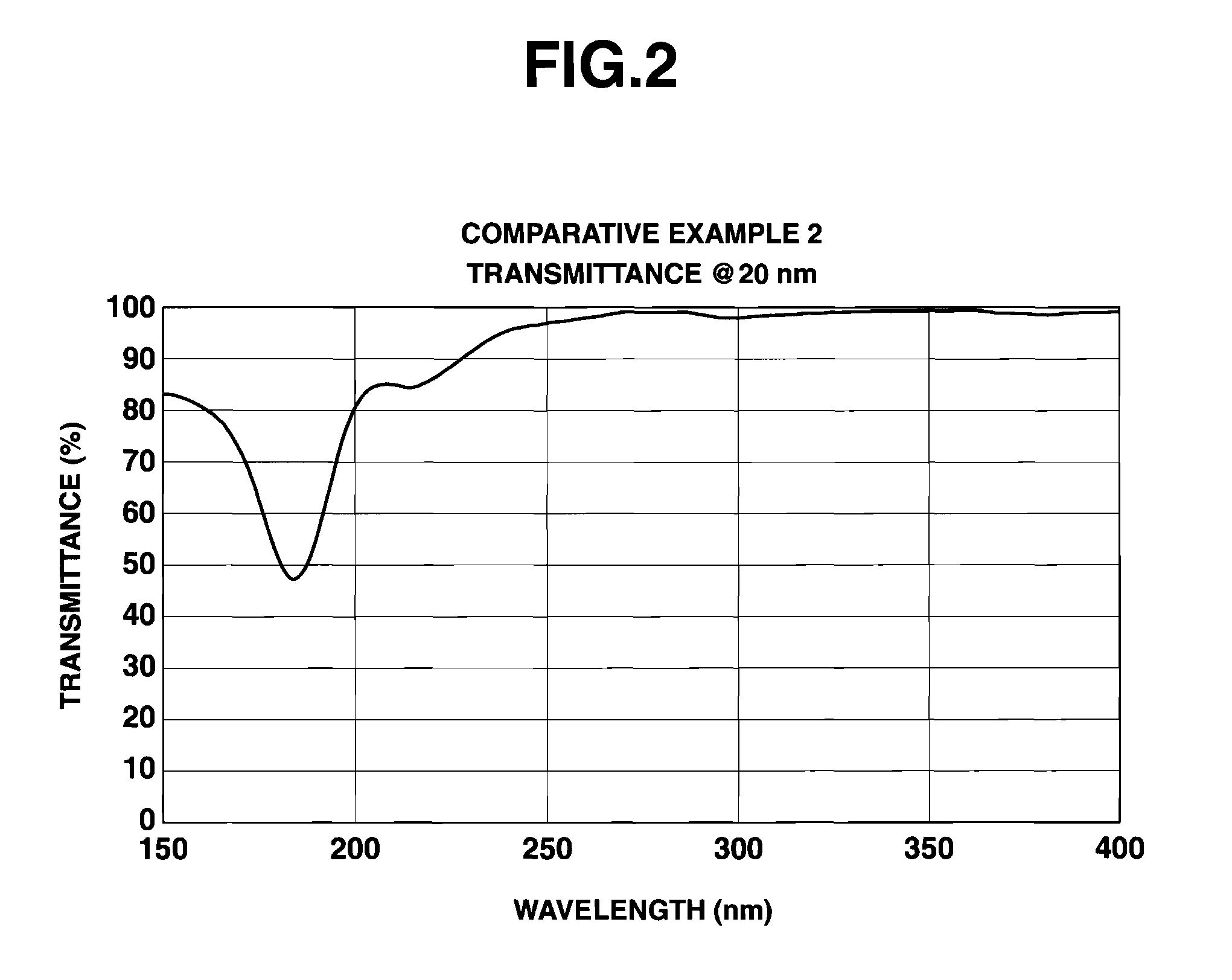

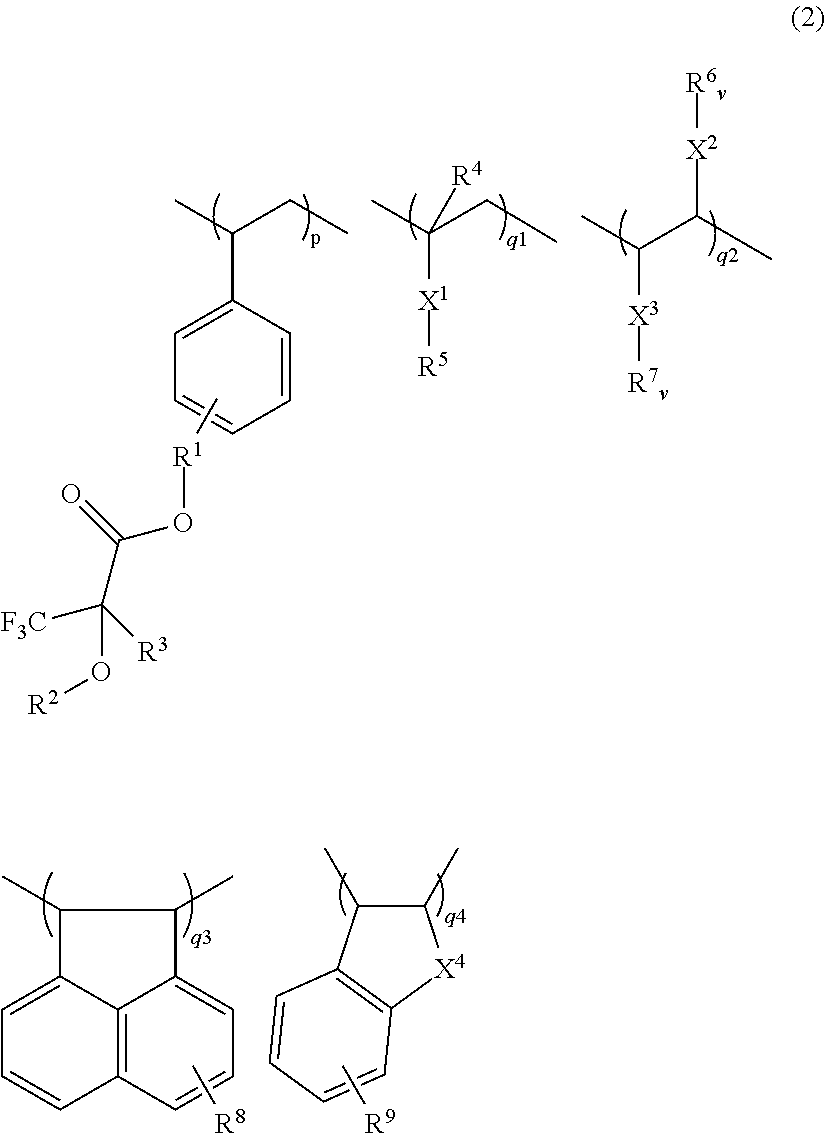

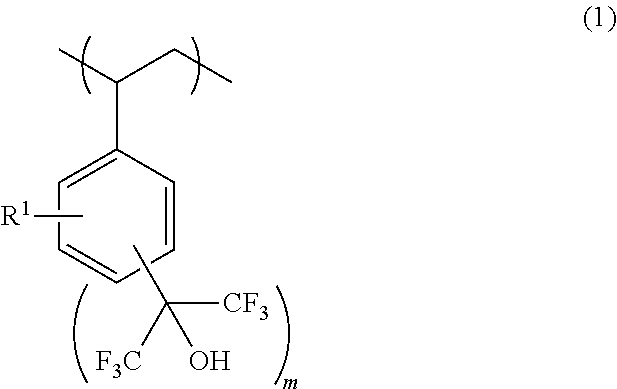

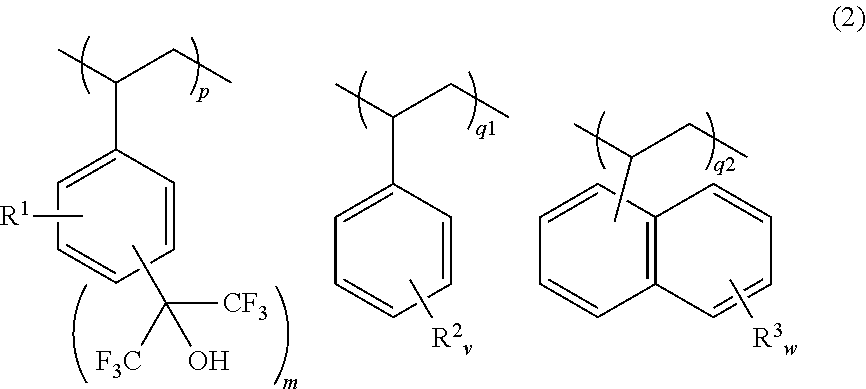

Photoresist composition for deep ultraviolet lithography comprising a mixture of photoactive compounds

InactiveUS6991888B2Reduce edge roughnessAcceptable photosensitivityOrganic chemistryOrganic compound preparationResistUltraviolet

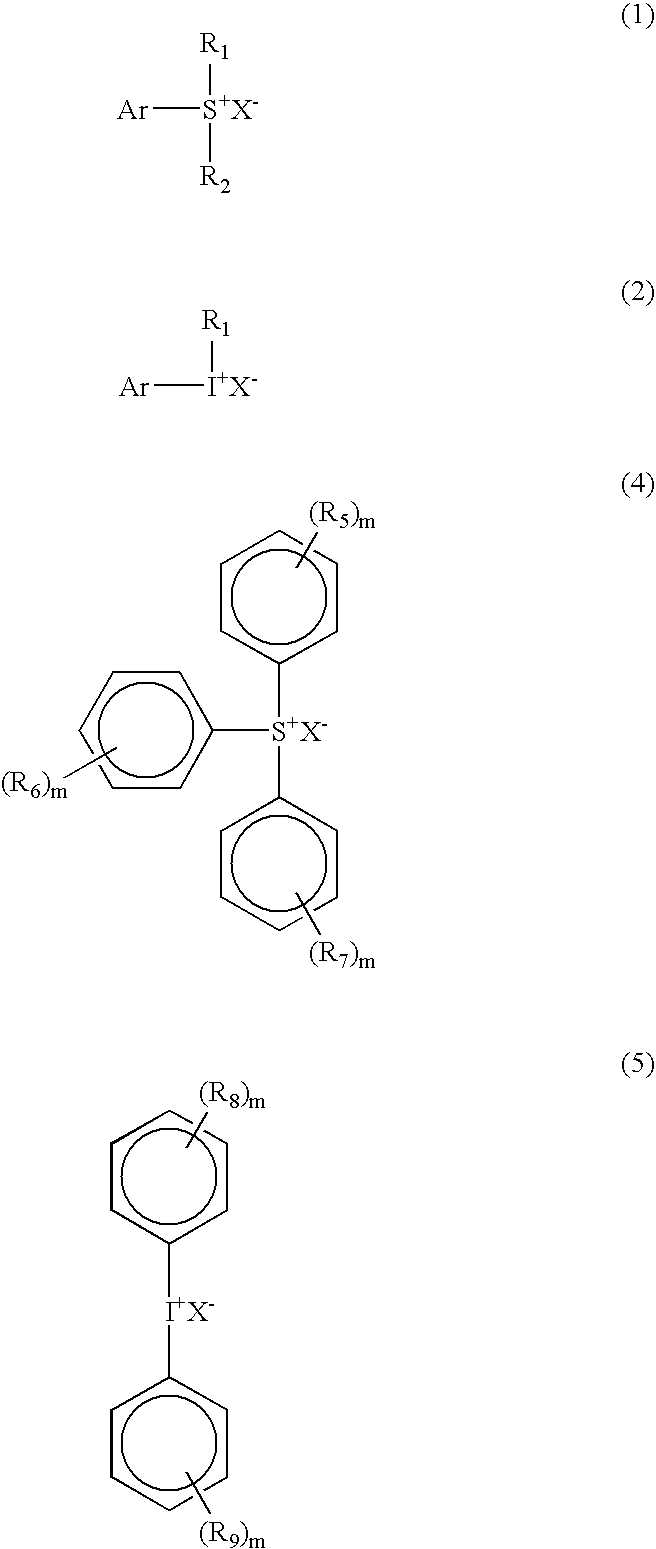

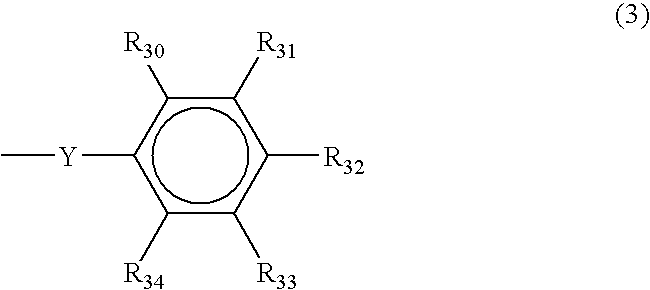

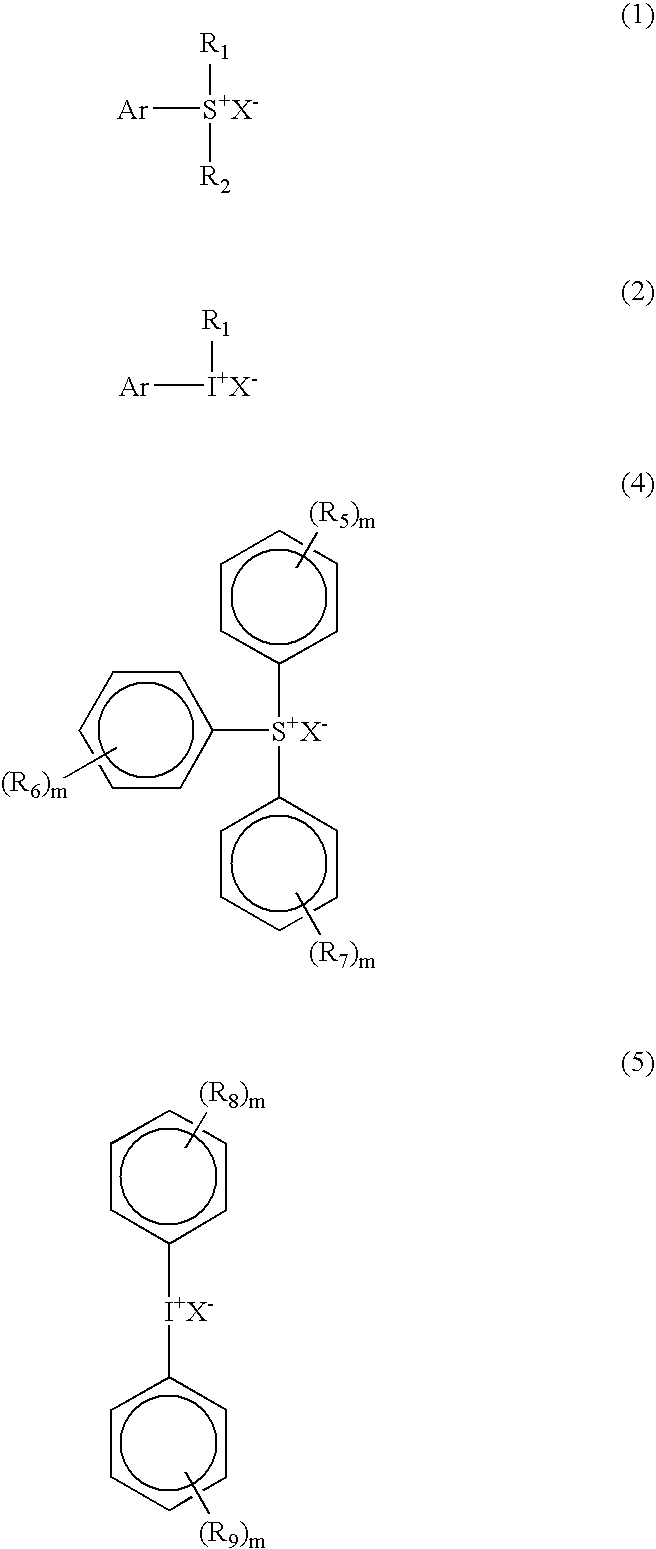

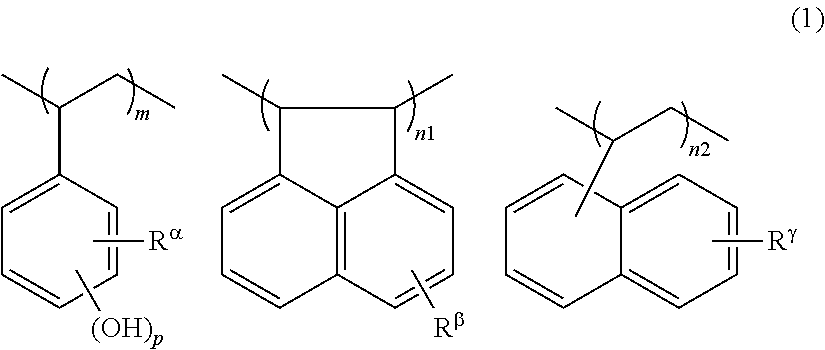

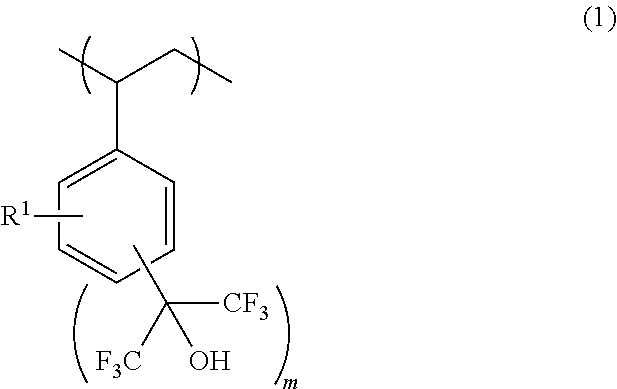

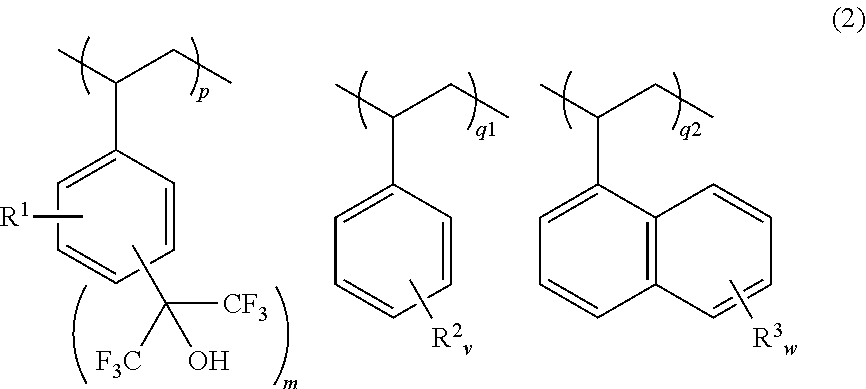

The present invention relates to a novel photoresist composition that can be developed with an aqueous alkaline solution, and is capable of being imaged at exposure wavelengths in the deep ultraviolet. The invention also relates to a process for imaging the novel photoresist as well as novel photoacid generators.The novel photoresist comprises a) a polymer containing an acid labile group, and b) a novel mixture of photoactive compounds, where the mixture comprises a lower absorbing compound selected from structure 1 and 2, and a higher absorbing compound selected from structure 4 and 5, where, R1 and R2 R5, R6, R7, R8, and R9 are defined herein; m=1–5; X− is an anion, and Ar is selected from naphthyl, anthracyl, and structure 3, where R30, R31, R32, R33, and R34 are defined herein.

Owner:MERCK PATENT GMBH

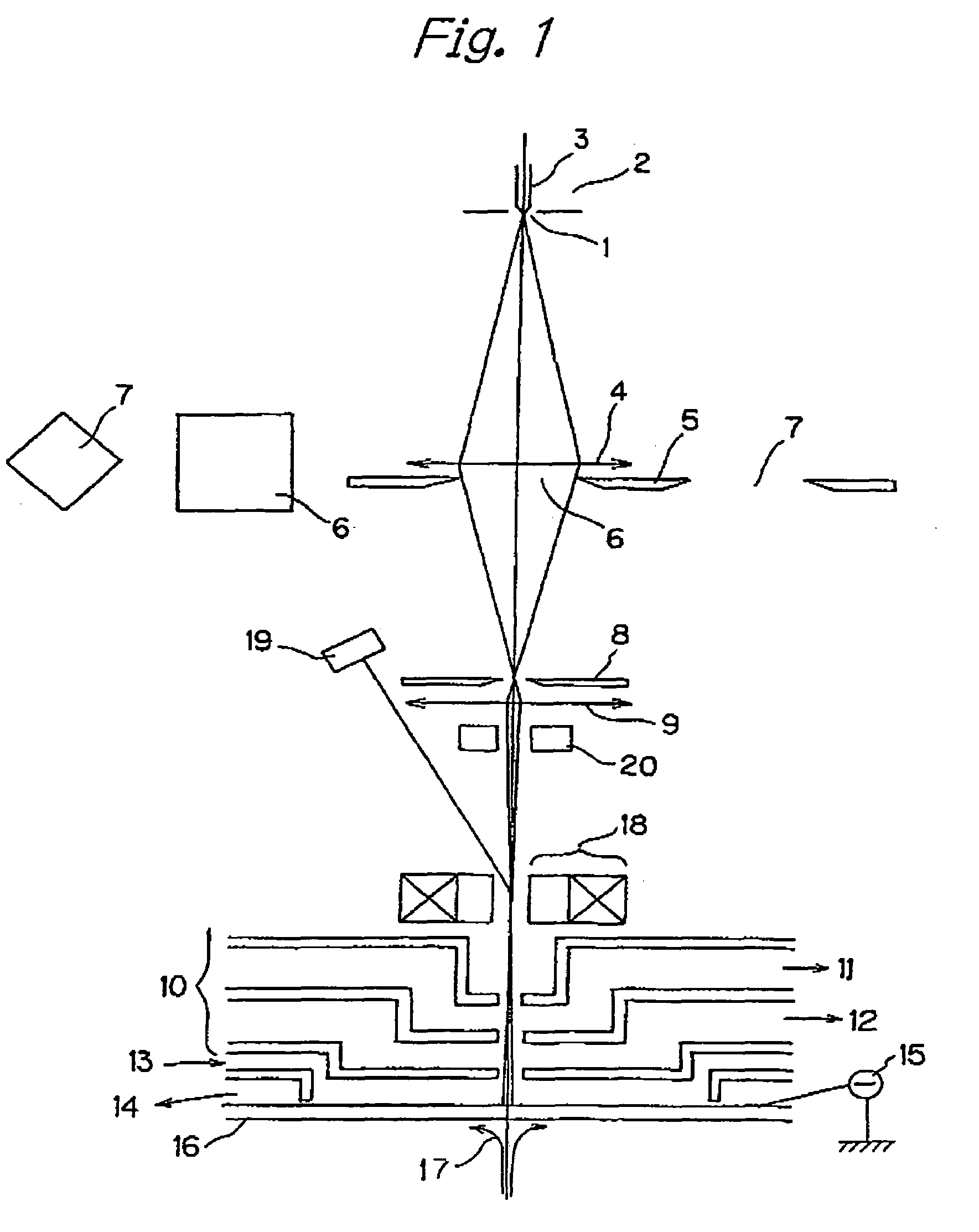

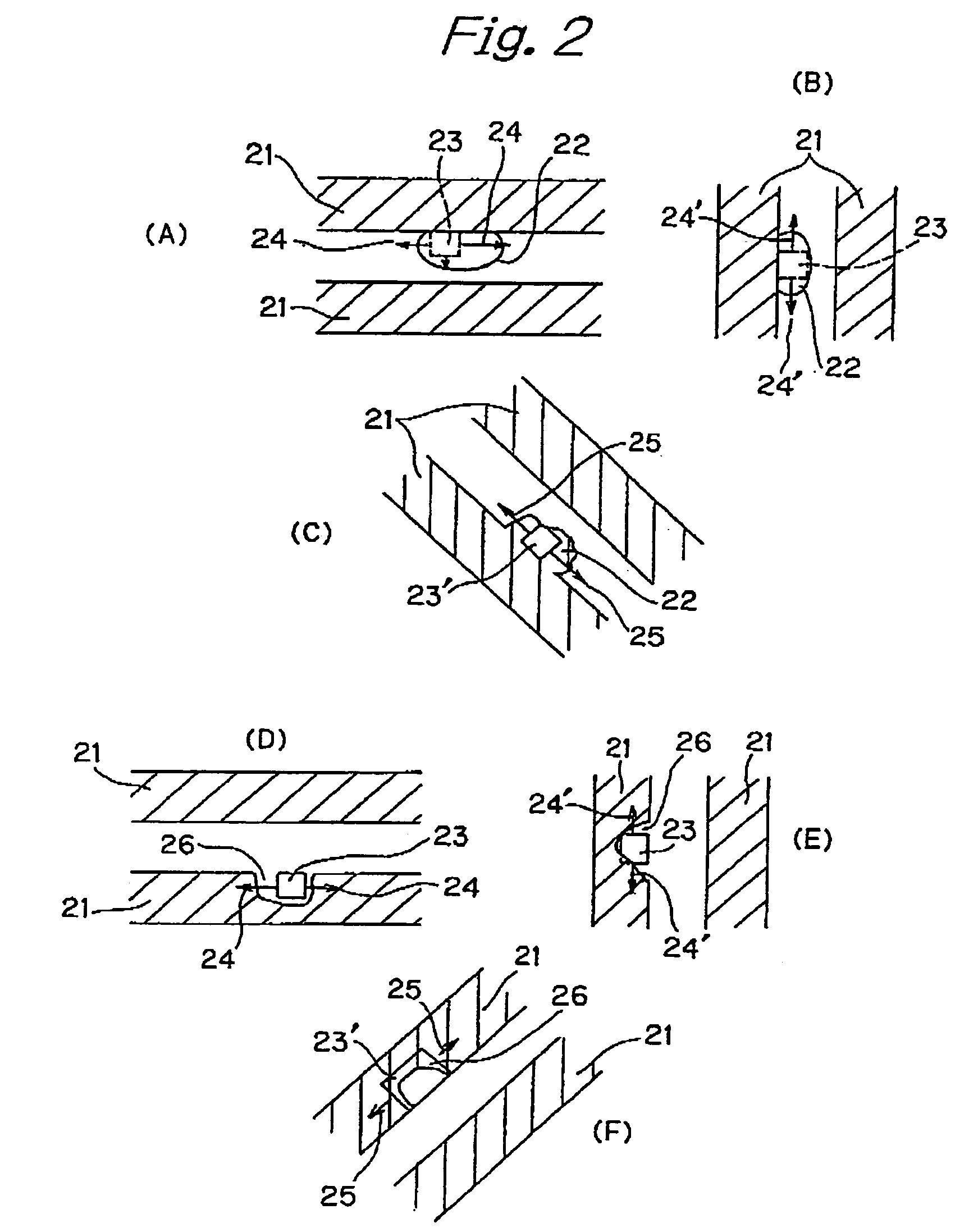

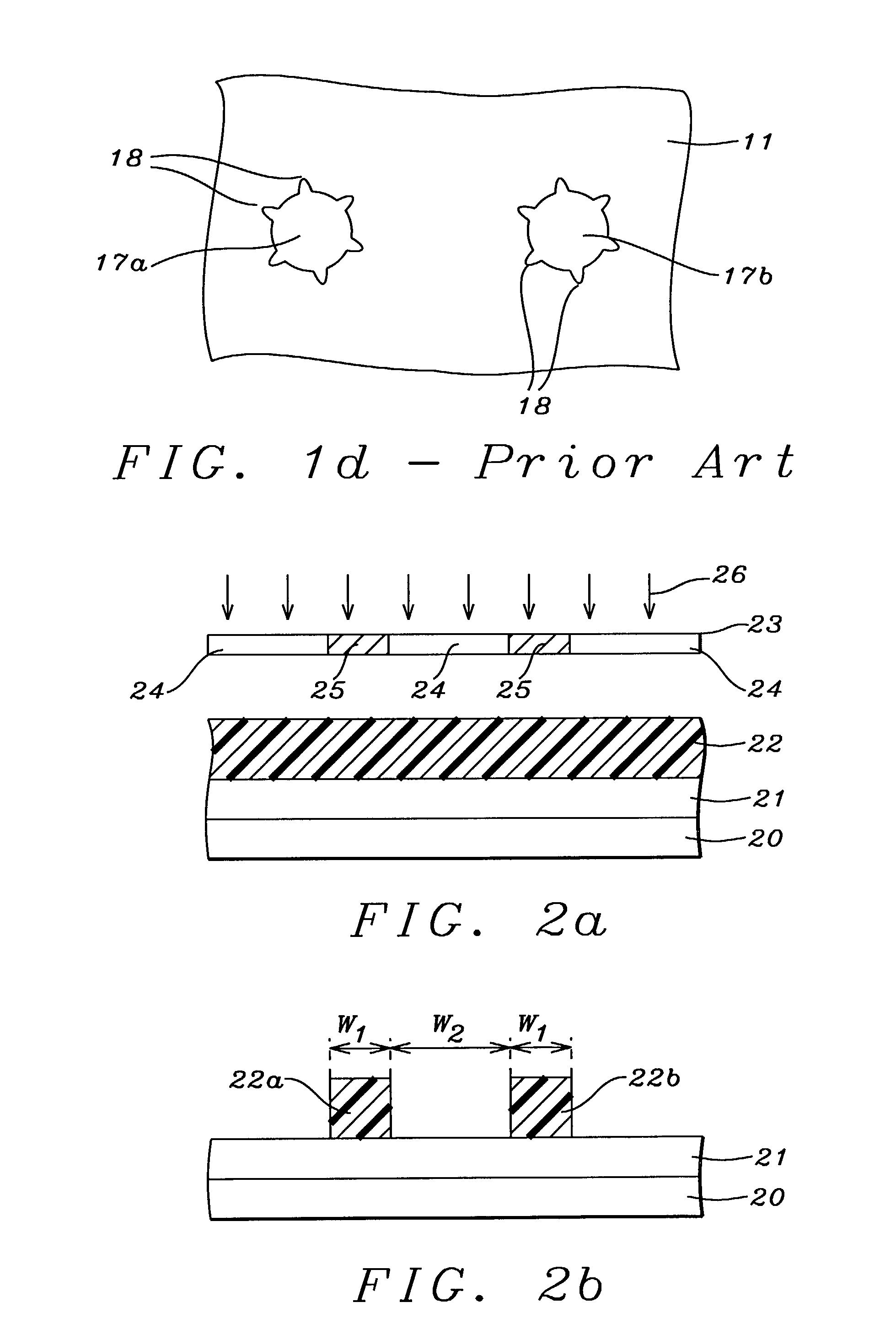

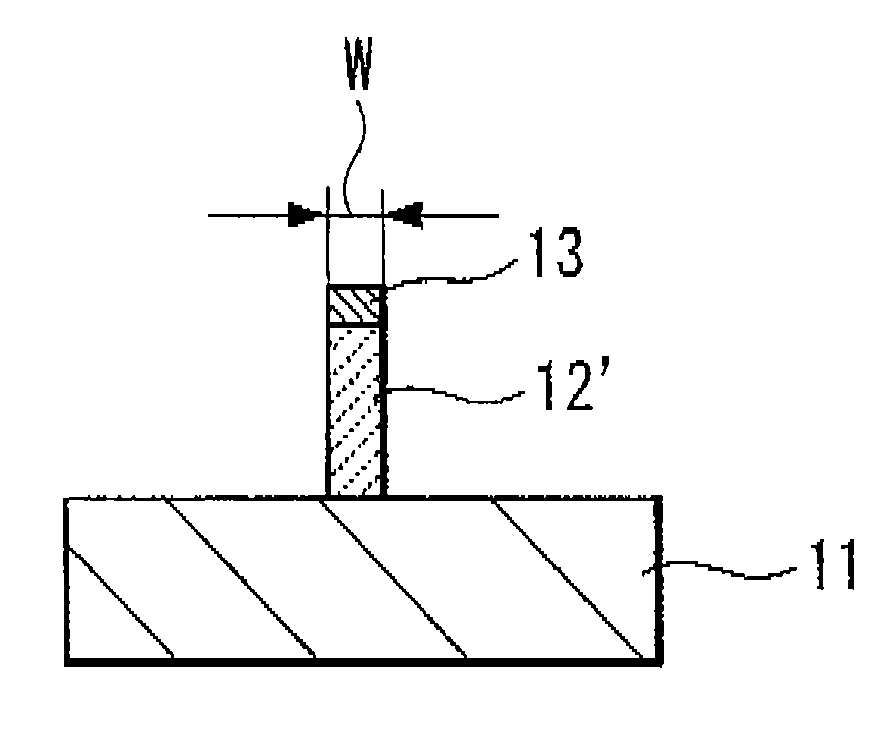

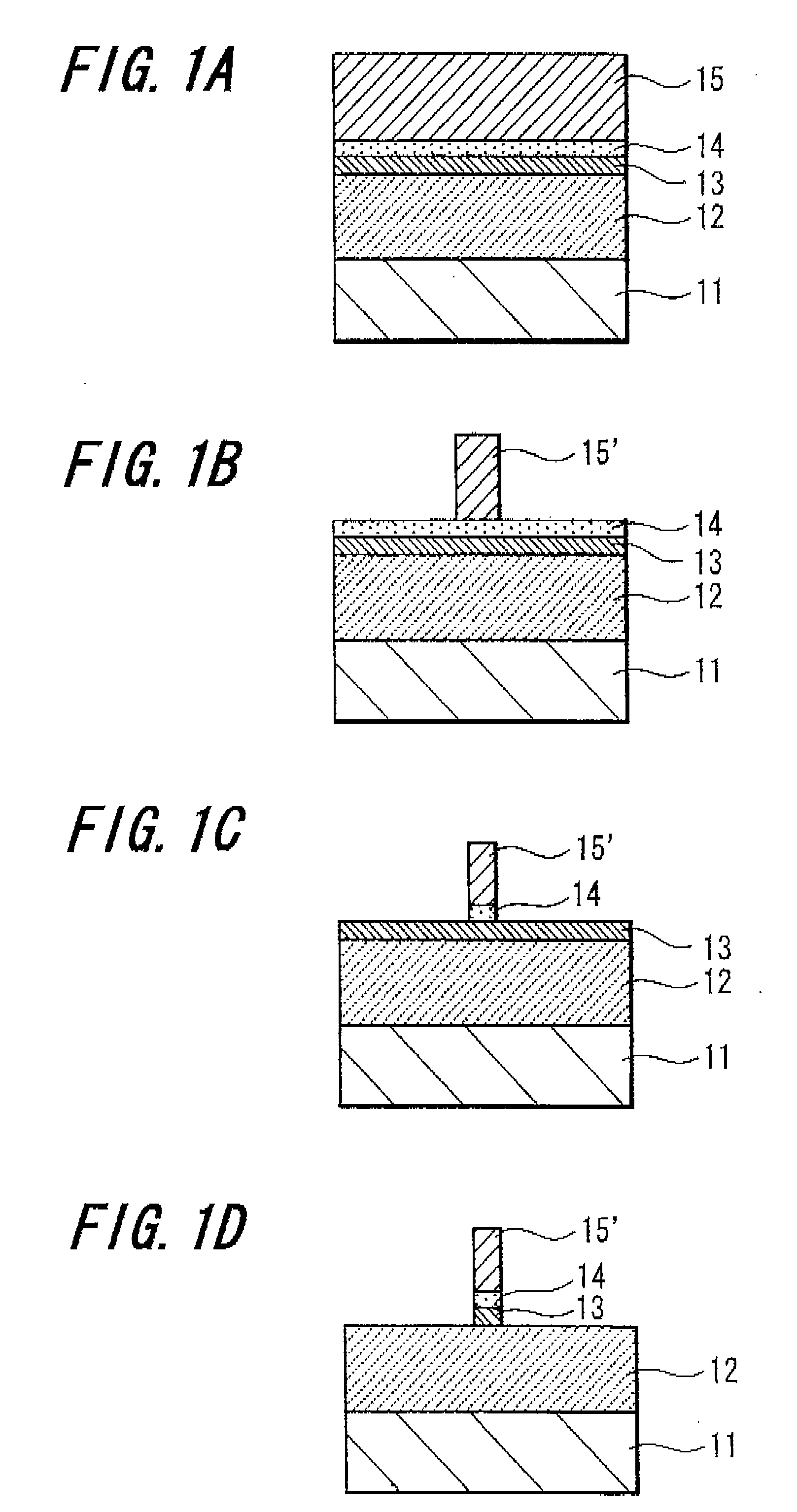

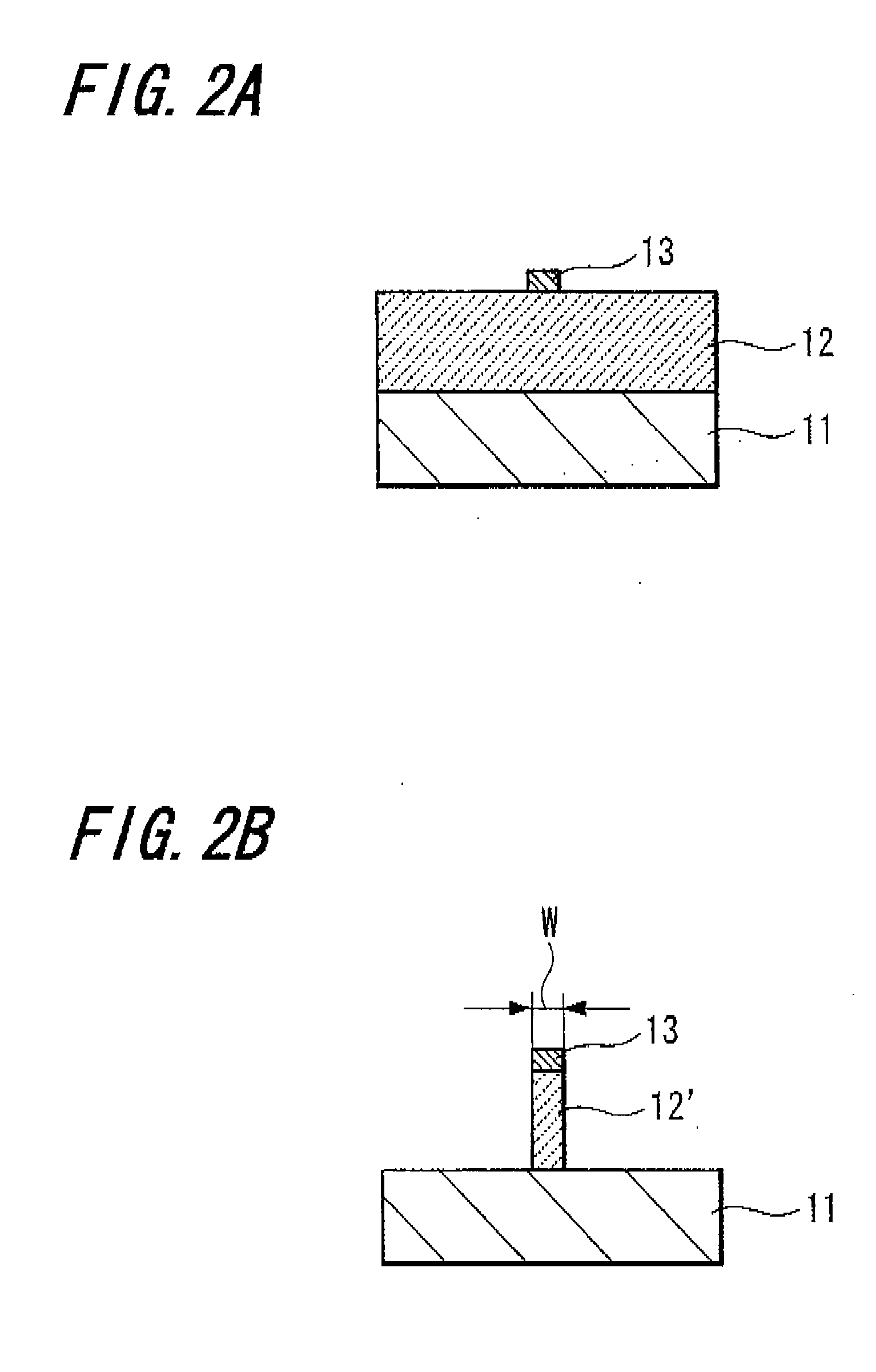

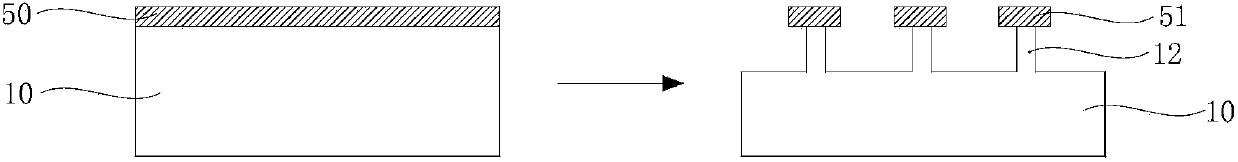

Sample repairing apparatus, a sample repairing method and a device manufacturing method using the same method

InactiveUS7256405B2Reduce edge roughnessReduce in quantityStability-of-path spectrometersMaterial analysis by optical meansEtchingReactive gas

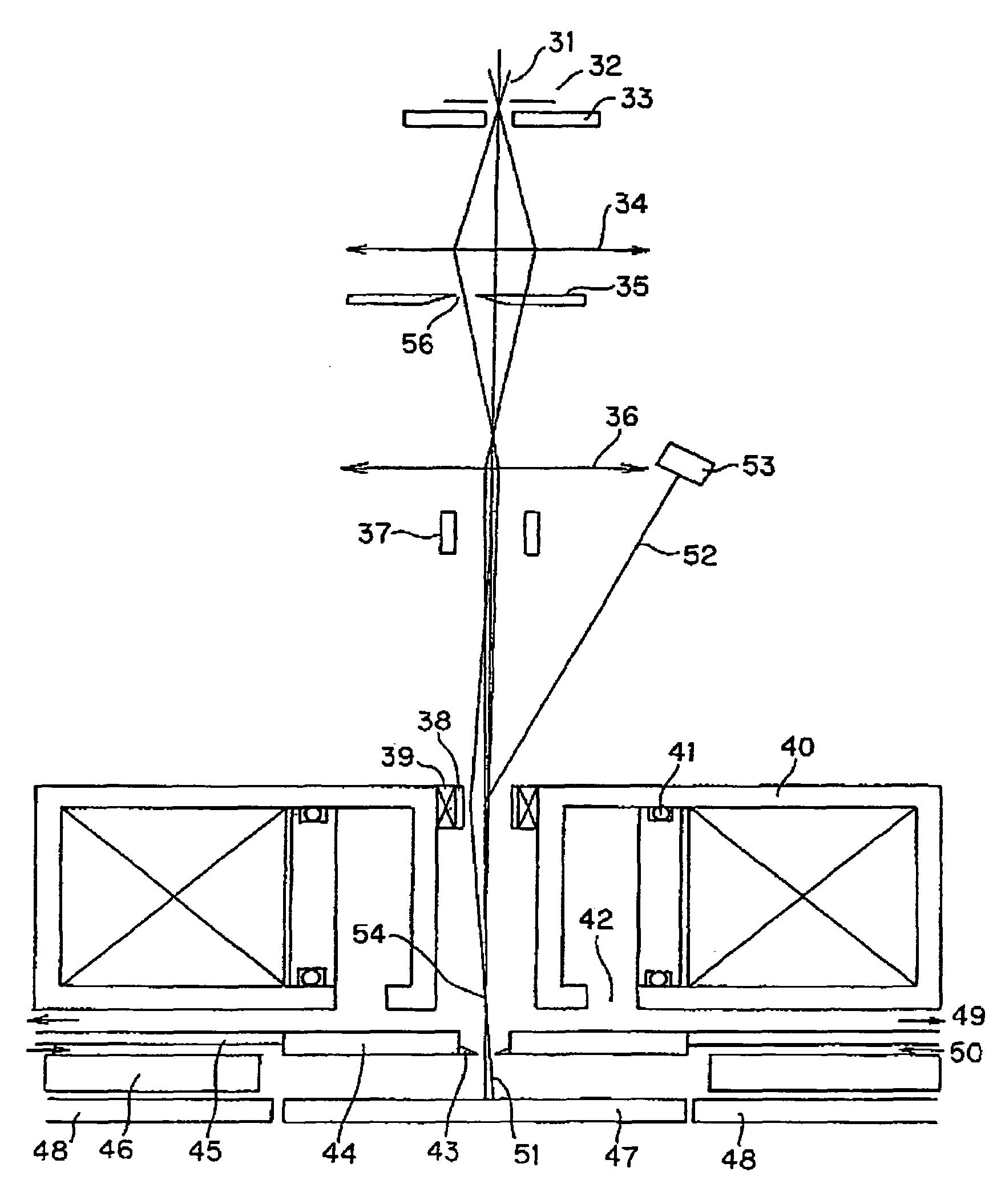

An object of the present invention is to provide a sample repairing apparatus, a sample repairing method and a device manufacturing method using the same method, which can reduce an edge roughness in a repaired pattern and also can provide the repairing of a sample by applying an electron beam-assisted etching or an electron beam-assisted deposition. There is provided a sample repairing method comprising: (a) a step of focusing an electron beam by an objective lens to irradiate a sample: (b) a step of supplying a reactive gas onto an electron beam irradiated surface of said sample: (c) a step of selectively scanning a pattern to be repaired on said sample with the electron beam so as to repair said pattern by applying an etching or a deposition; and (d) a step of providing a continuous exhausting operation by means of a differential exhaust system arranged in said objective lens so as to prevent the reactive gas supplied onto said electron beam irradiated surface from flowing toward an electron gun side.

Owner:EBARA CORP

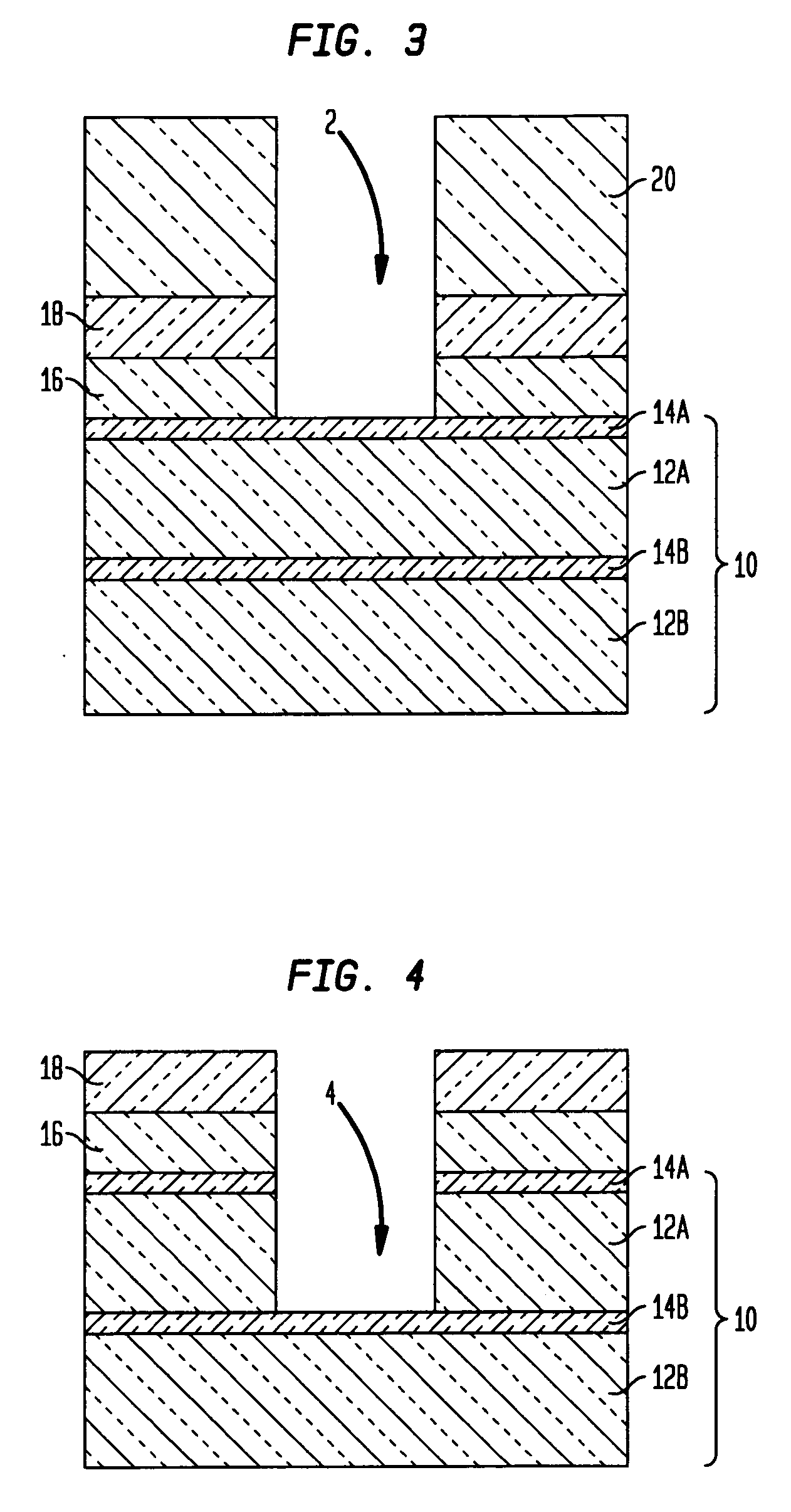

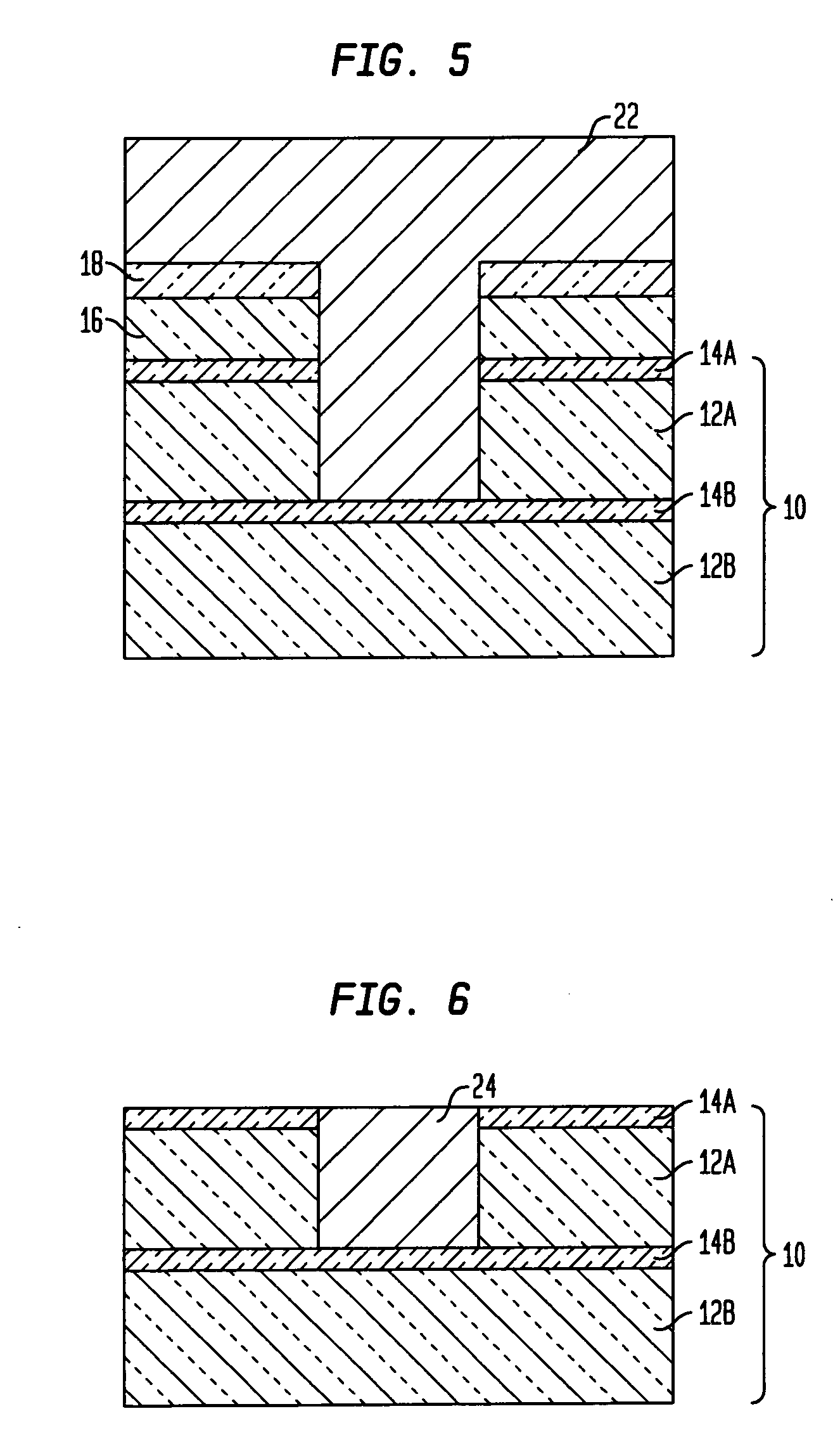

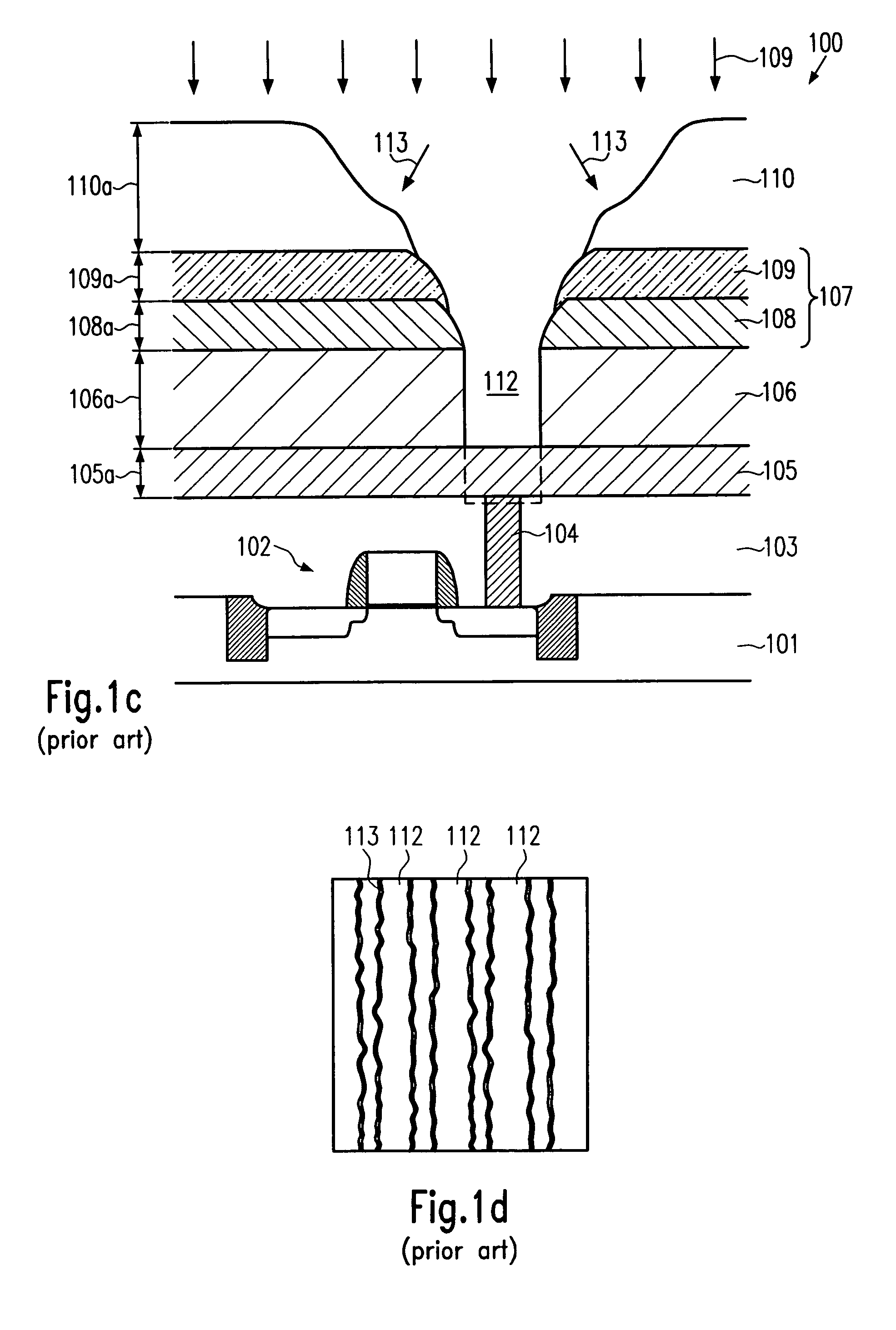

Complementary replacement of material

InactiveUS7399709B1Increase contrastMinimized roughnessDecorative surface effectsSolid-state devicesResistResolution enhancement technologies

An image reversal method is described that removes the etch resistance requirement from a resist. A high resolution resist pattern comprised of islands, lines, or trenches is formed with a large process window by exposing through one or more masks including phase edge masks and optionally with resolution enhancement techniques. A complementary material replacement (CMR) layer comprised of an organic polymer or material such as fluorosilicate glass which has a lower etch rate than the resist is coated over the resist pattern. CMR and resist layers are etched simultaneously to provide an image reversed pattern in the CMR layer which is etch transferred into a substrate. The method avoids edge roughness like bird's beak defects in the etched pattern and is useful for applications including forming contact holes in dielectric layers, forming polysilicon gates, and forming trenches in a damascene process. It is also valuable for direct write methods where an image reversal scheme is desired.

Owner:TAIWAN SEMICON MFG CO LTD

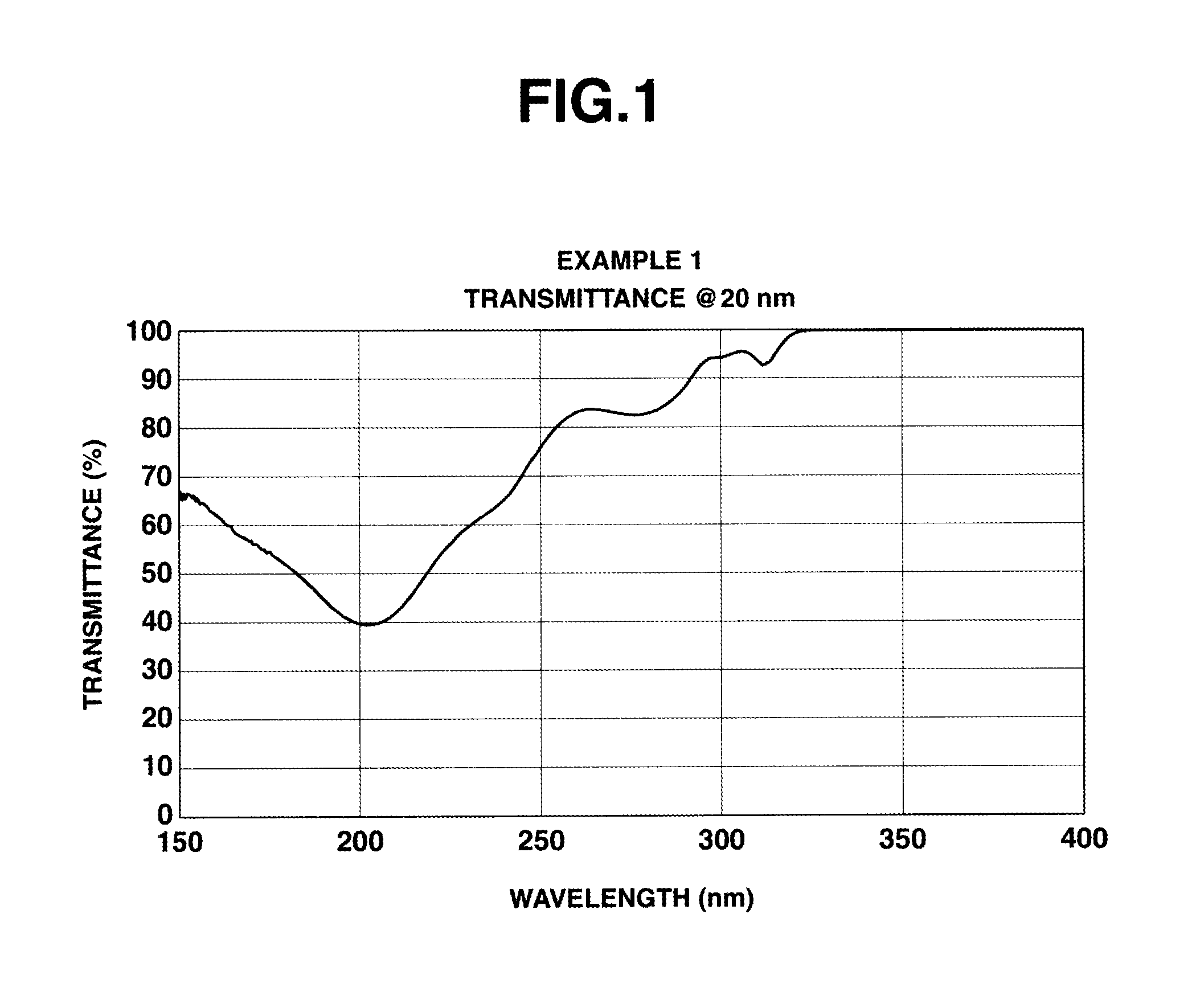

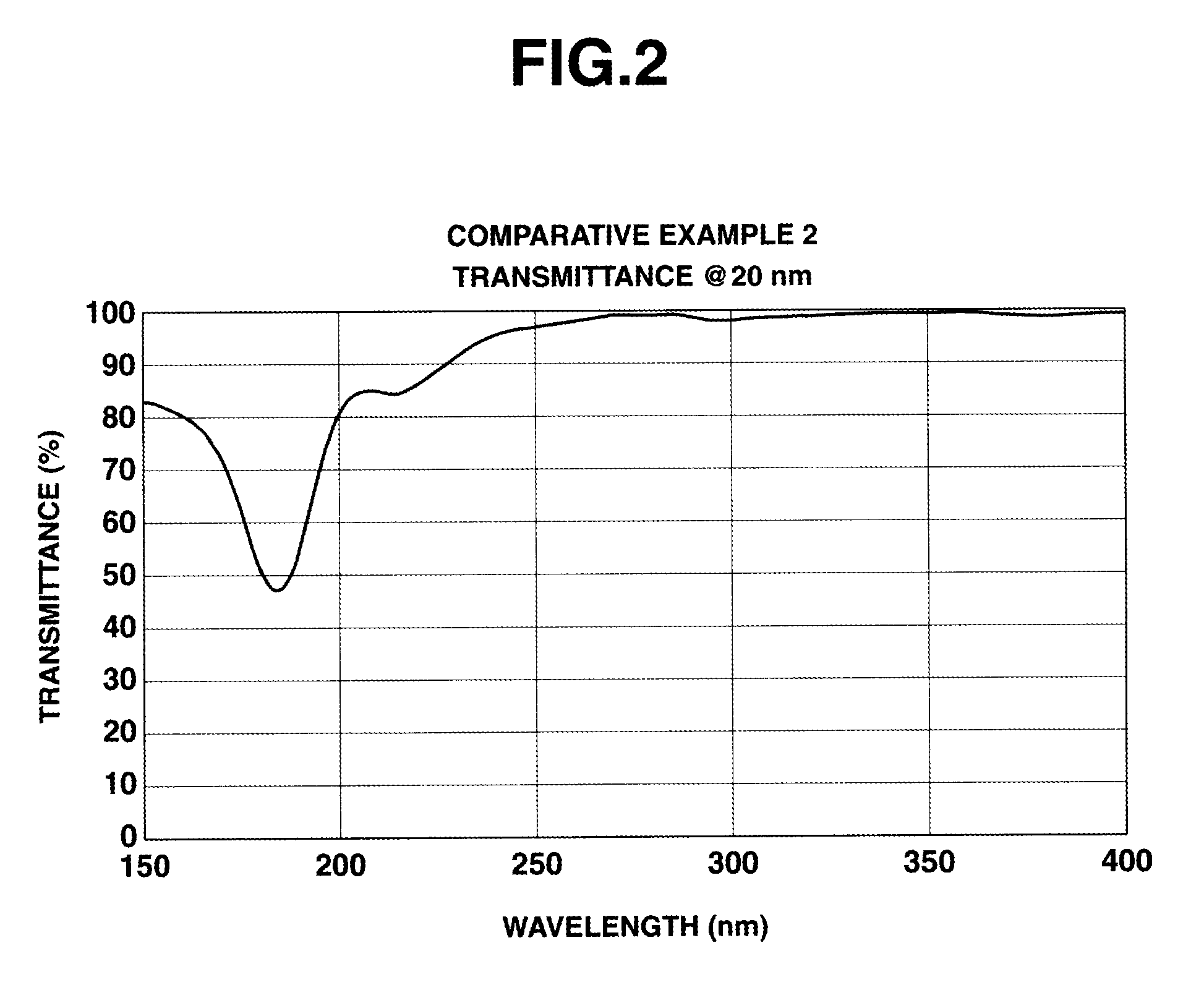

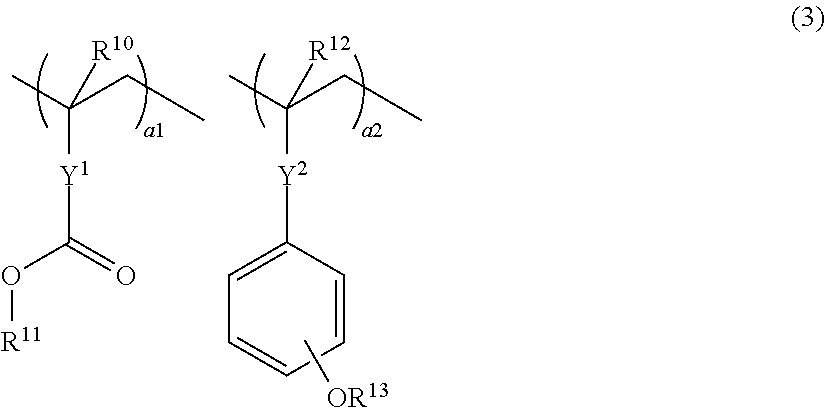

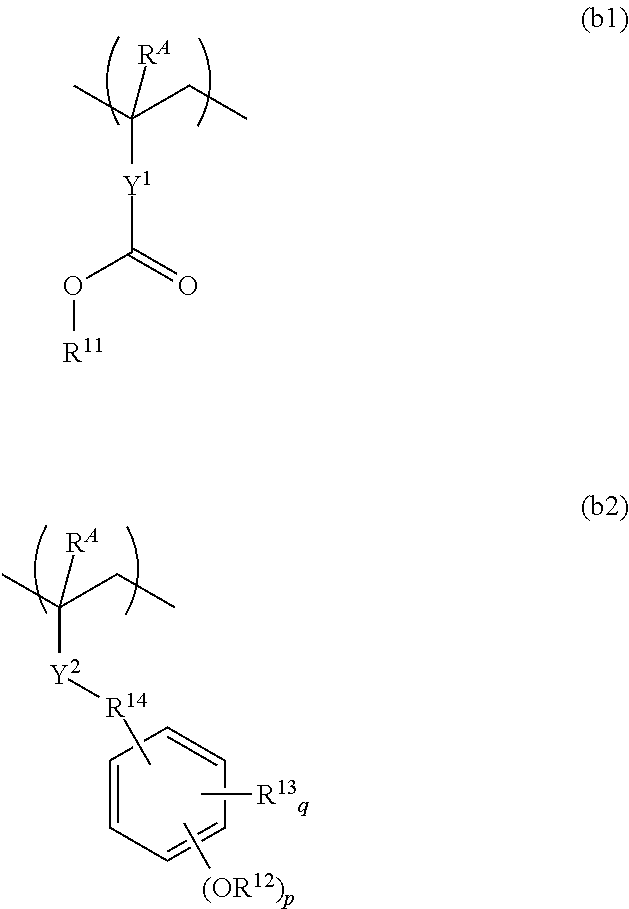

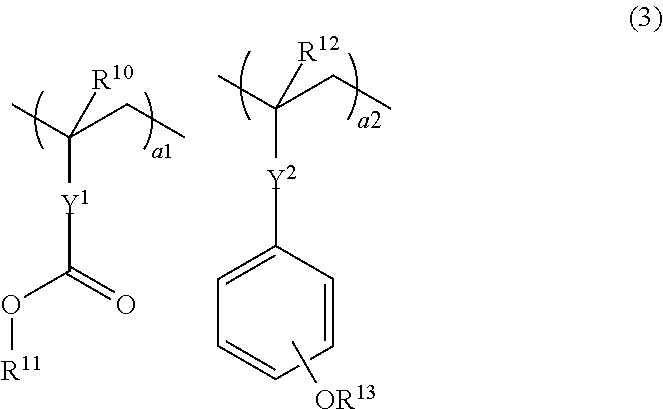

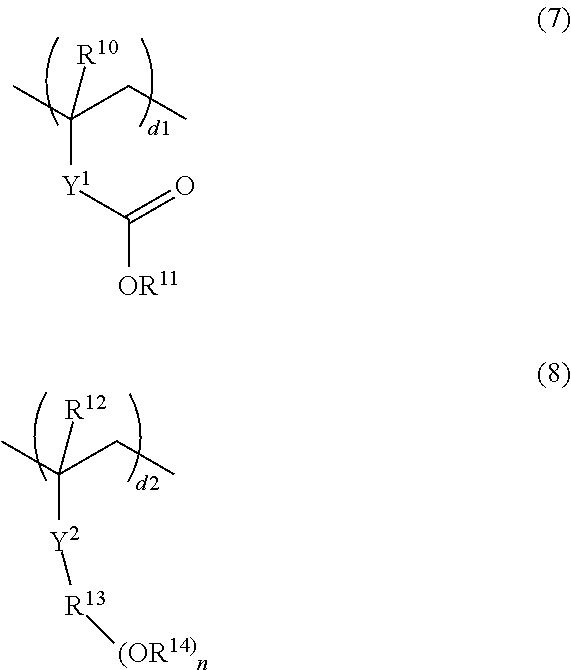

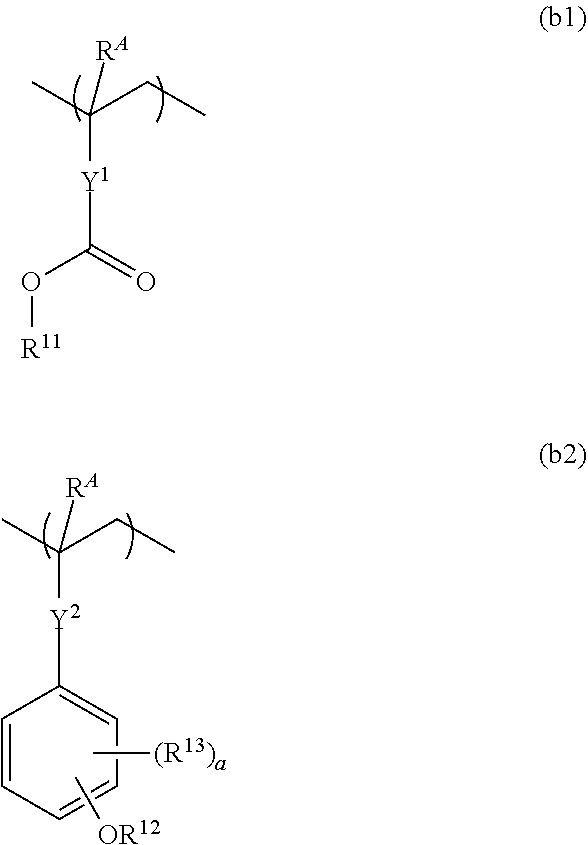

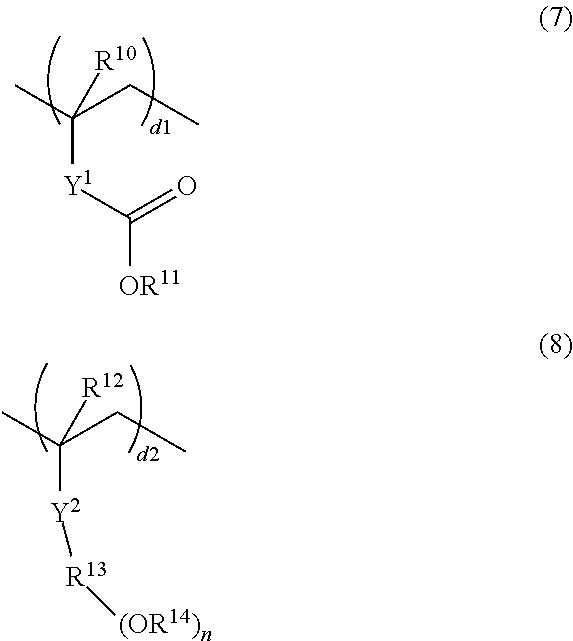

Resist-protective film-forming composition and patterning process

ActiveUS20130143162A1High sensitivityReduce edge roughnessElectric discharge tubesPhotomechanical exposure apparatusComposite materialEther

A pattern is printed by forming a photoresist layer on a wafer, forming a protective film thereon, exposure, and development. The protective film is formed from a protective film-forming composition comprising a novolak resin of a bisphenol compound and a mixture of an alcohol solvent and an ether or aromatic solvent.

Owner:SHIN ETSU CHEM IND CO LTD

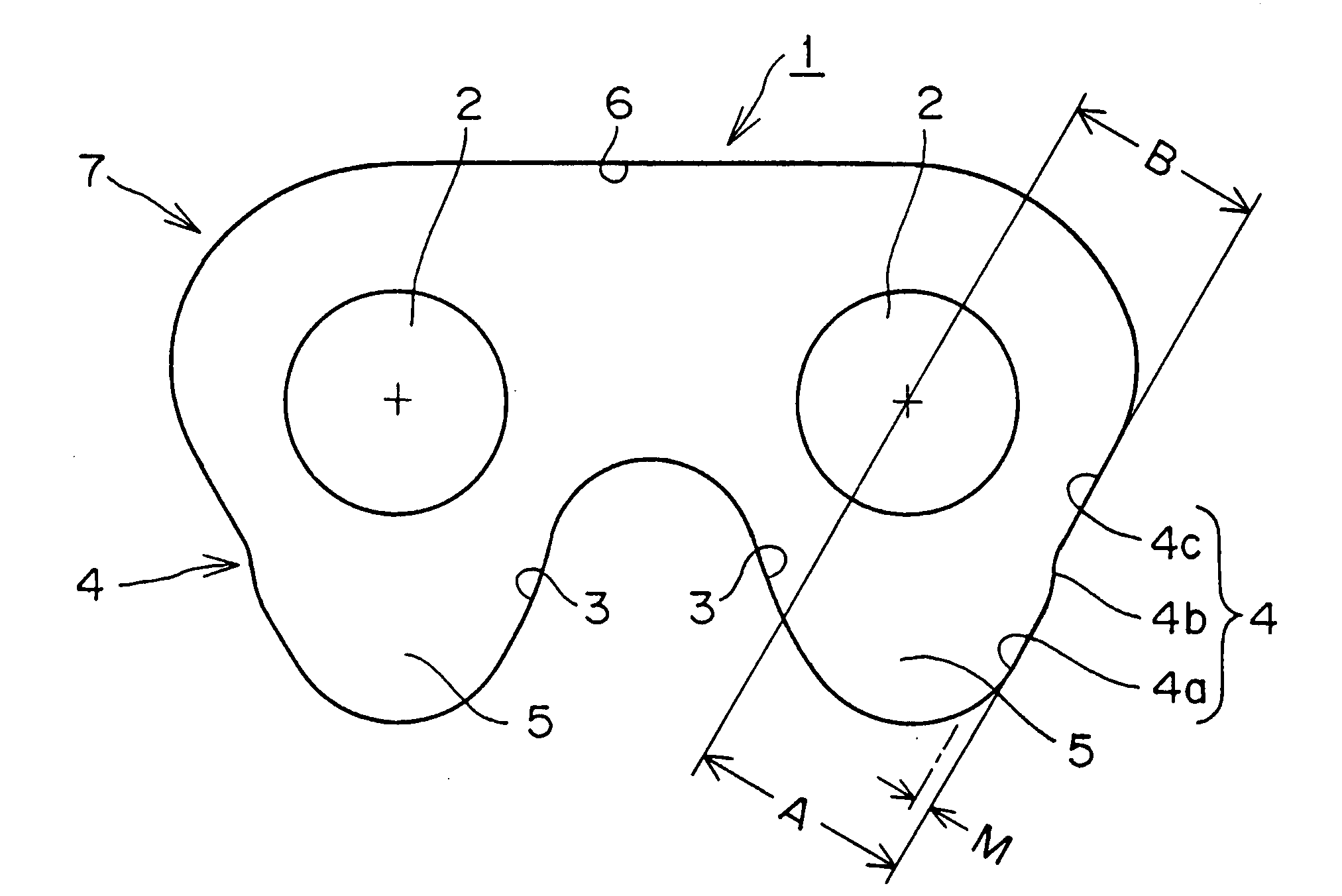

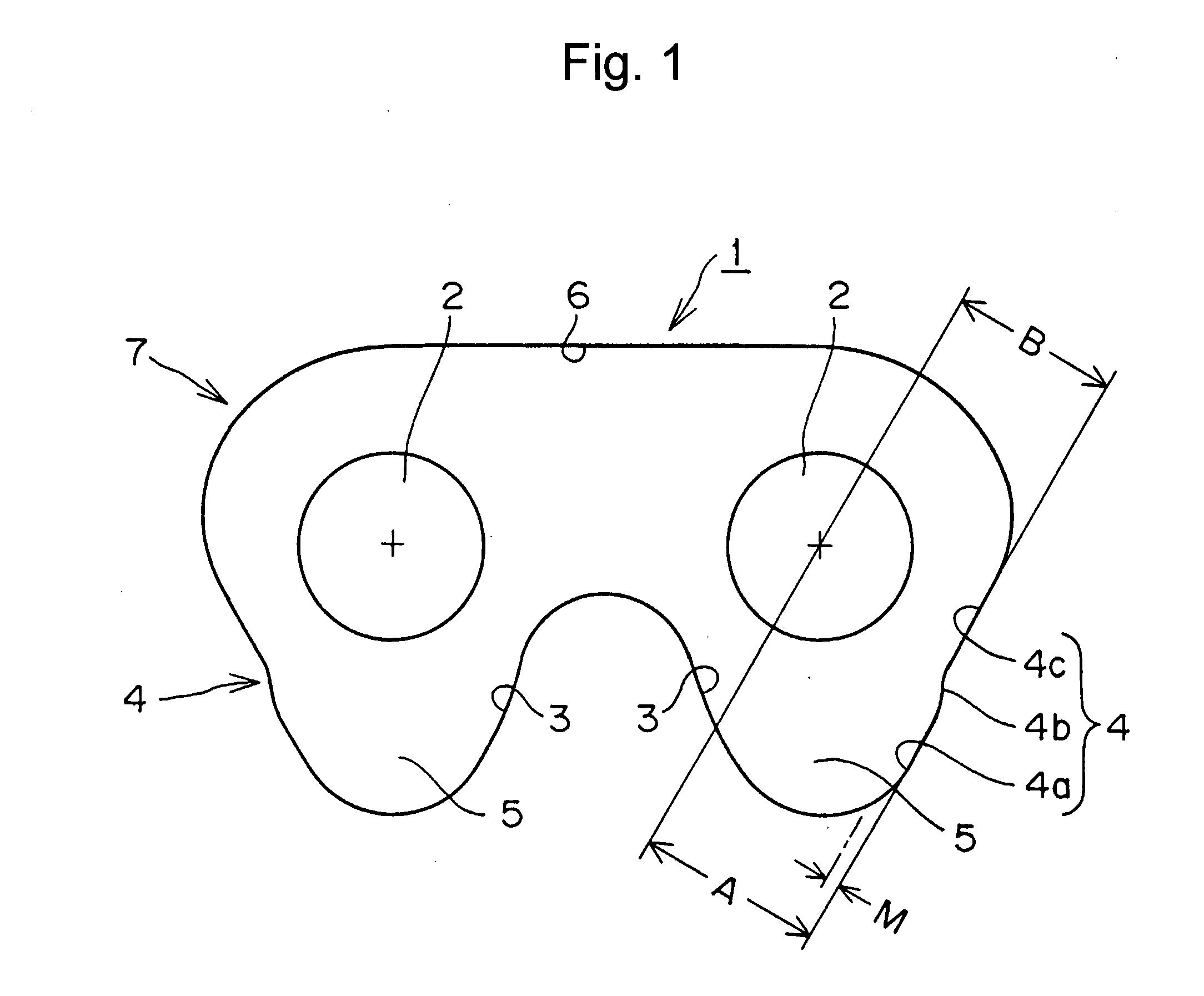

Link plate for silent chain

InactiveUS20080167151A1Improve shear plane coefficientReduce roughnessDriving chainsEngineeringMechanical engineering

Owner:TSUBAKIMOTO CHAIN CO

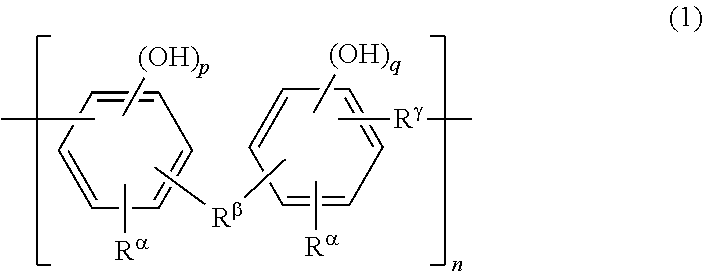

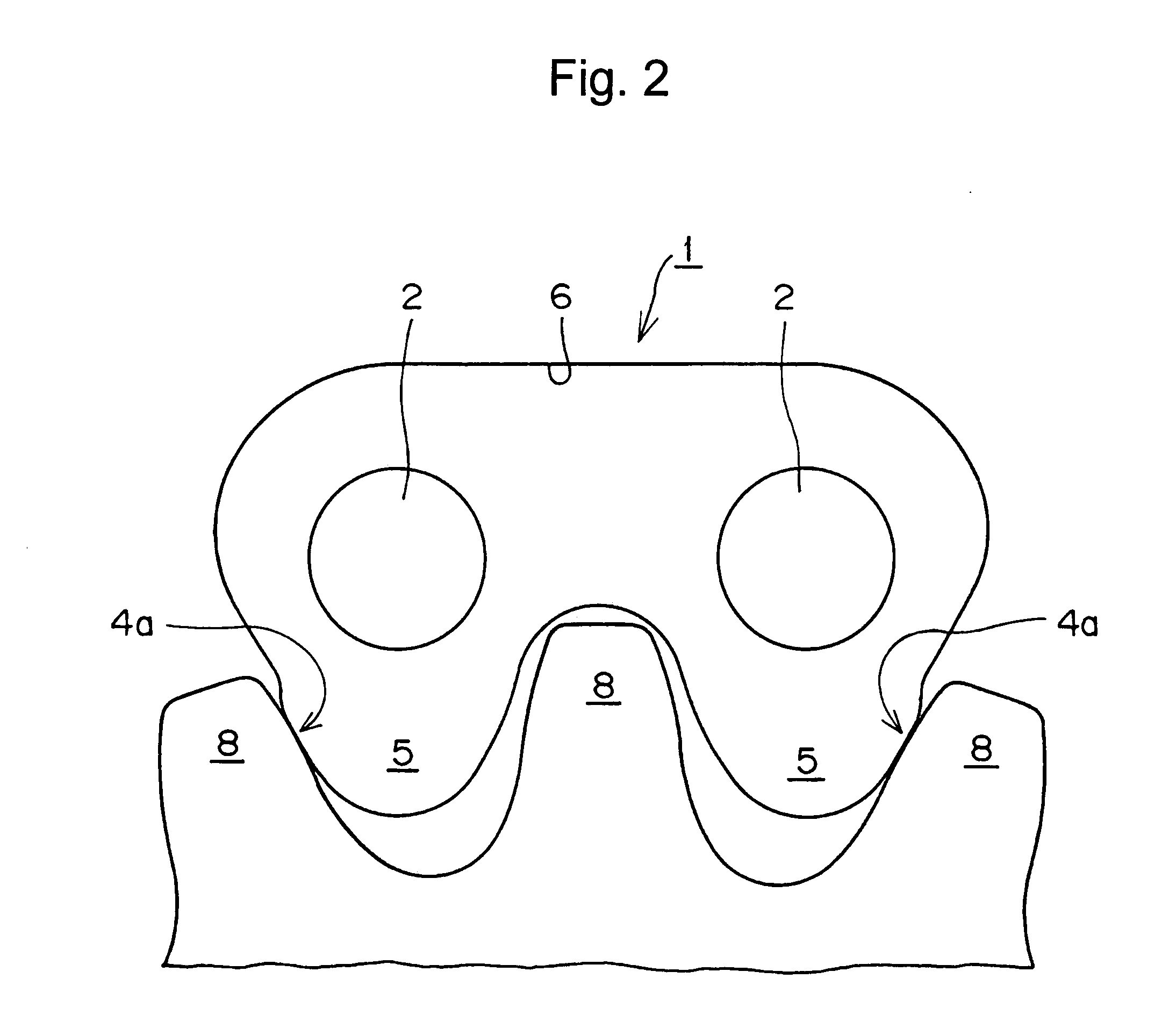

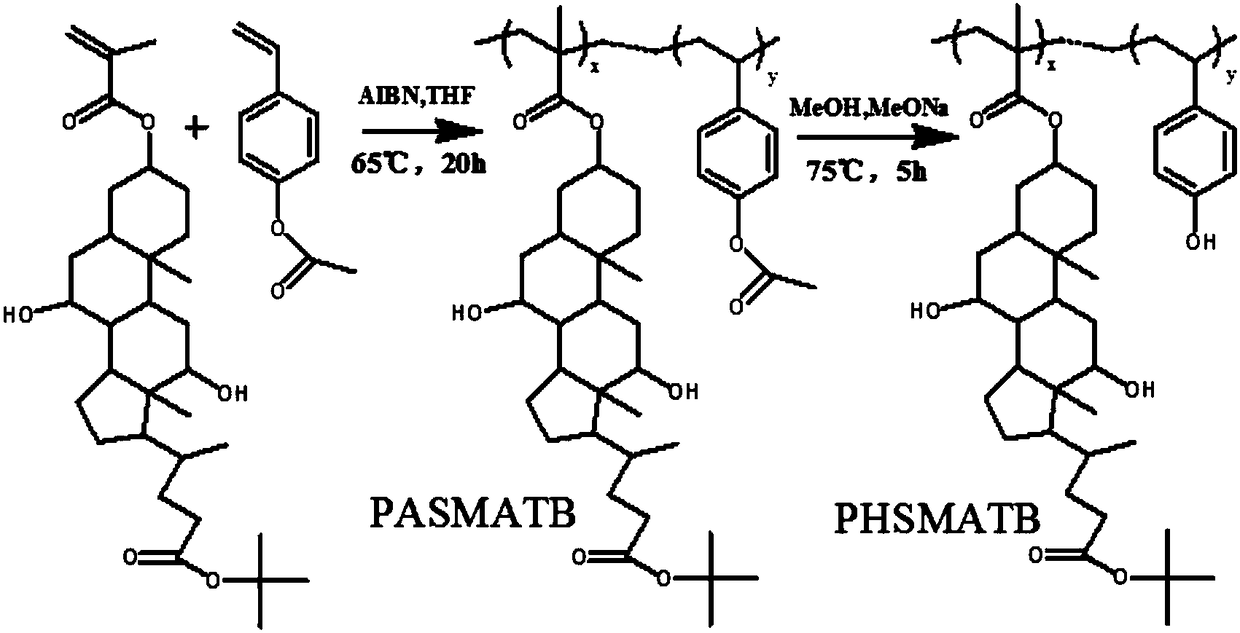

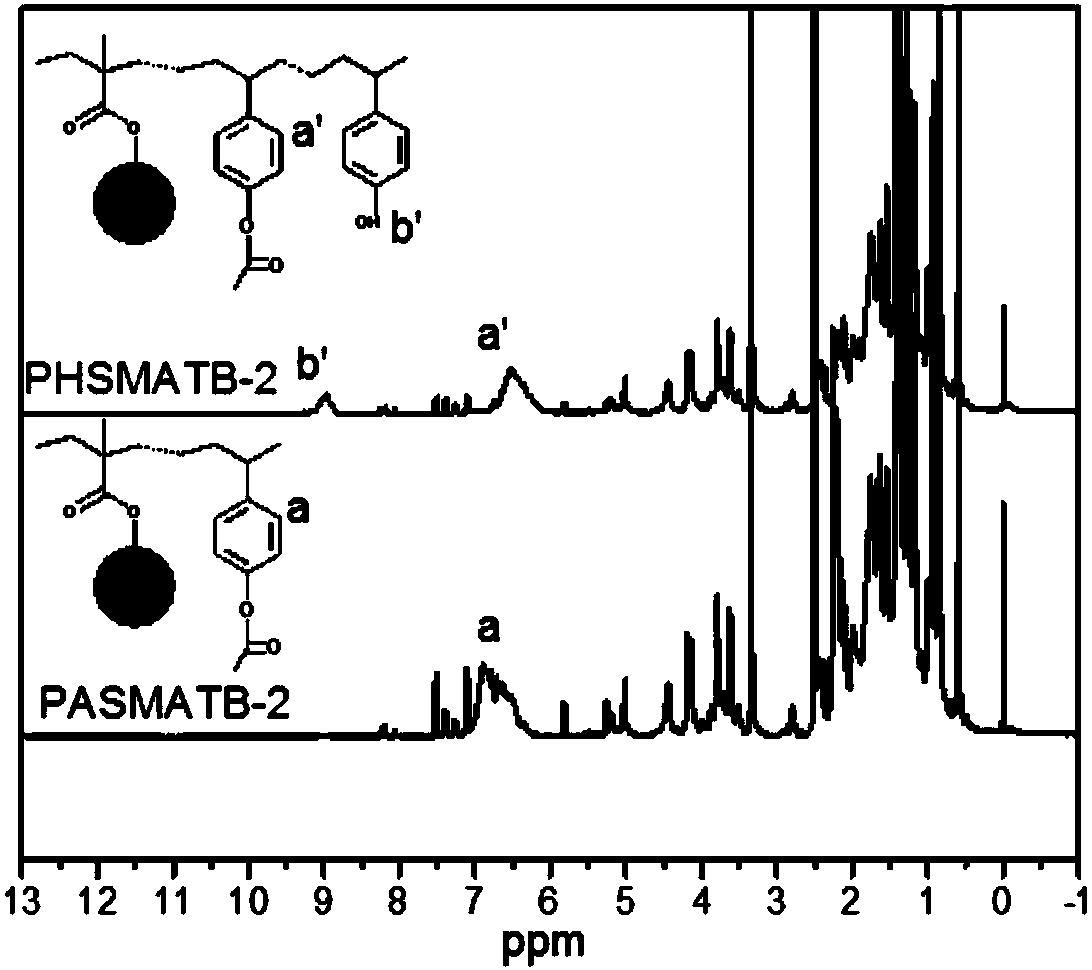

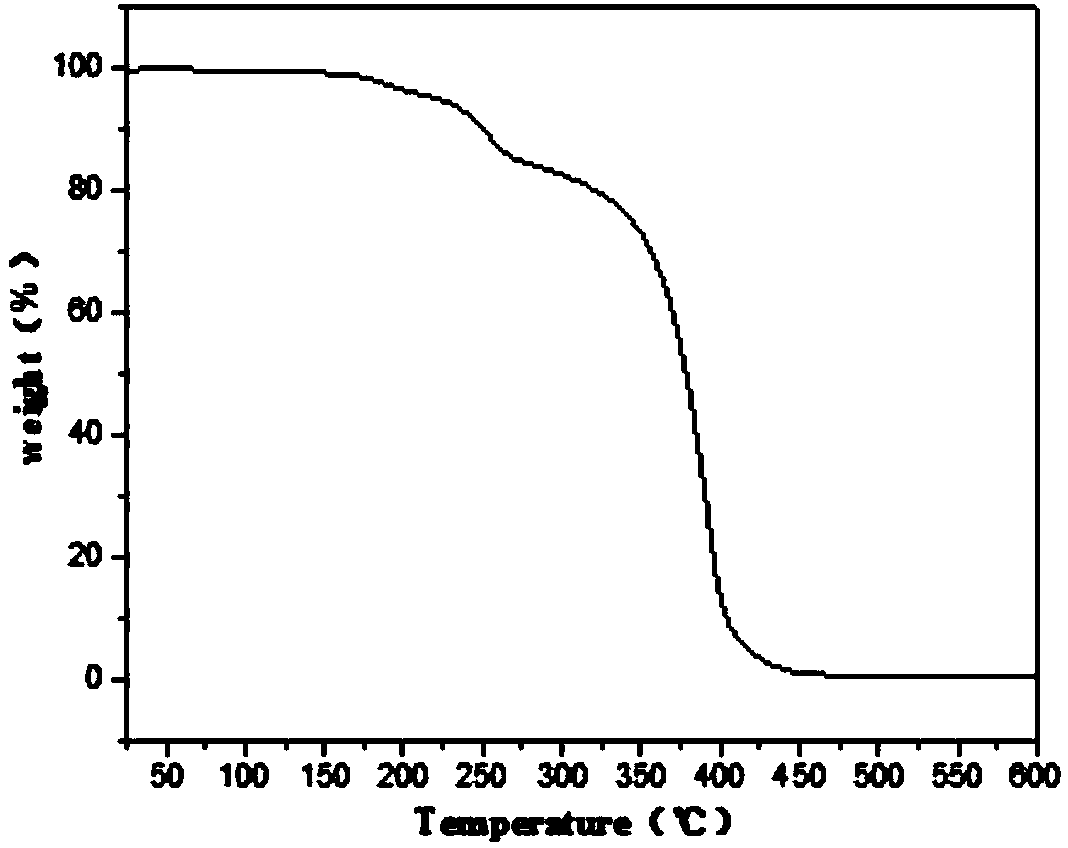

Bio-based film-forming resin and photoresist prepared by same

ActiveCN108084331AHigh light transmittanceImprove adhesionPhotosensitive materials for photomechanical apparatusPolymer scienceSide chain

The invention discloses bio-based film-forming resin and photoresist prepared by the same. The bio-based film-forming resin is prepared by styrene derivatives and cholic acid derivatives through freeradical polymerization reaction and alcoholysis reaction. The bio-based film-forming resin is mixed with a photo-acid generator, auxiliaries, a solvent and the like to prepare the 365nm and 248nm photoresist. The bio-based film-forming resin has the advantages that polymerizable monomers containing natural product cholic acid are introduced into conventional poly(p-hydroxystyrene) film-forming resin to form the new improved film-forming resin, the new film-forming resin can increase the ultraviolet transparency of the photoresist and increase the photosensitivity of the photoresist, and the large cyclic structure of the film-forming resin can increase carbon compactness, reduce the free volume of polymerization chains, increase heat resistance and increase the etching resistance of the film-forming resin; large lateral chains can improve the problem of acid diffusion, increase dissolution difference and lower image edge roughness.

Owner:JIANGNAN UNIV

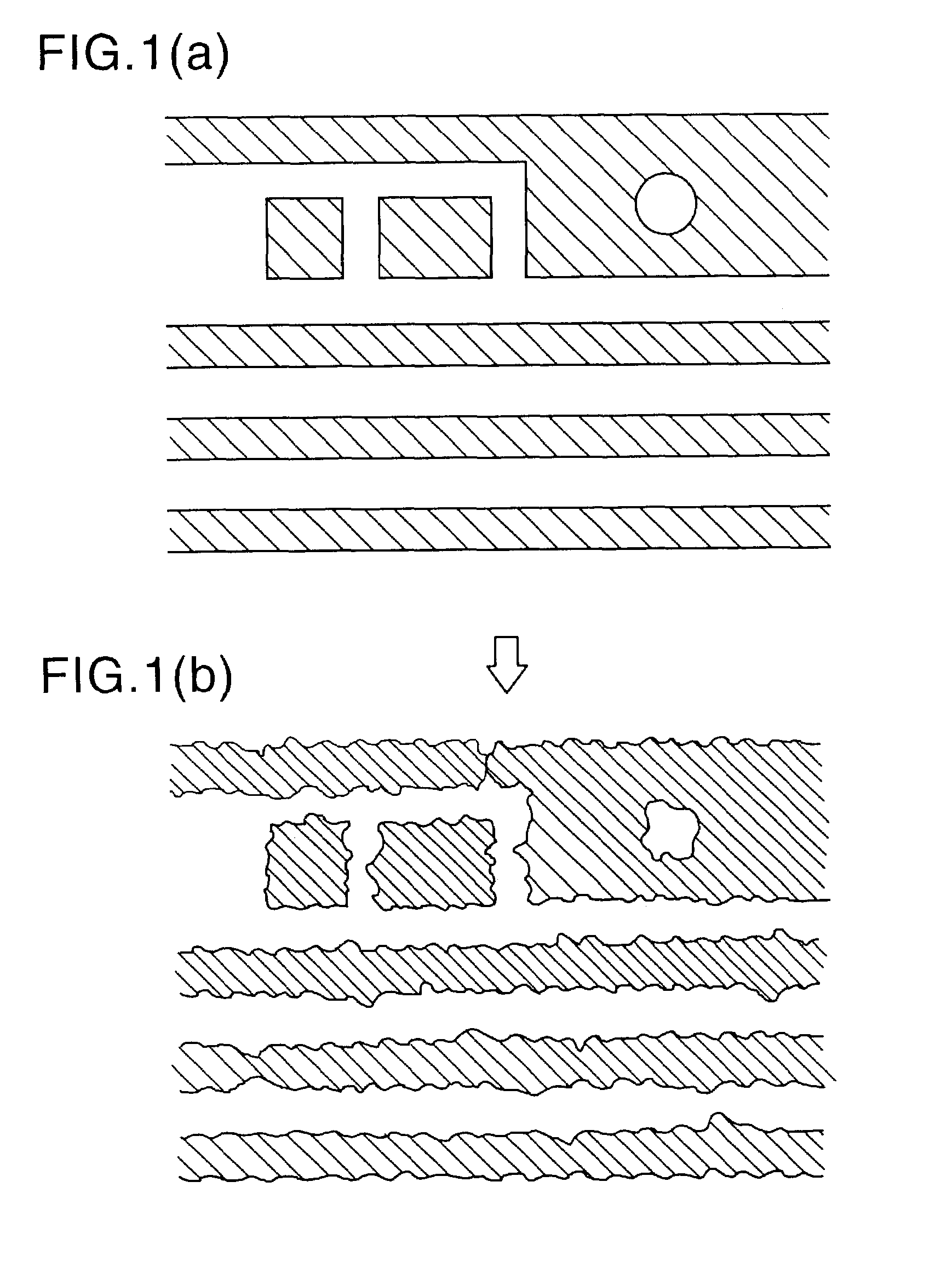

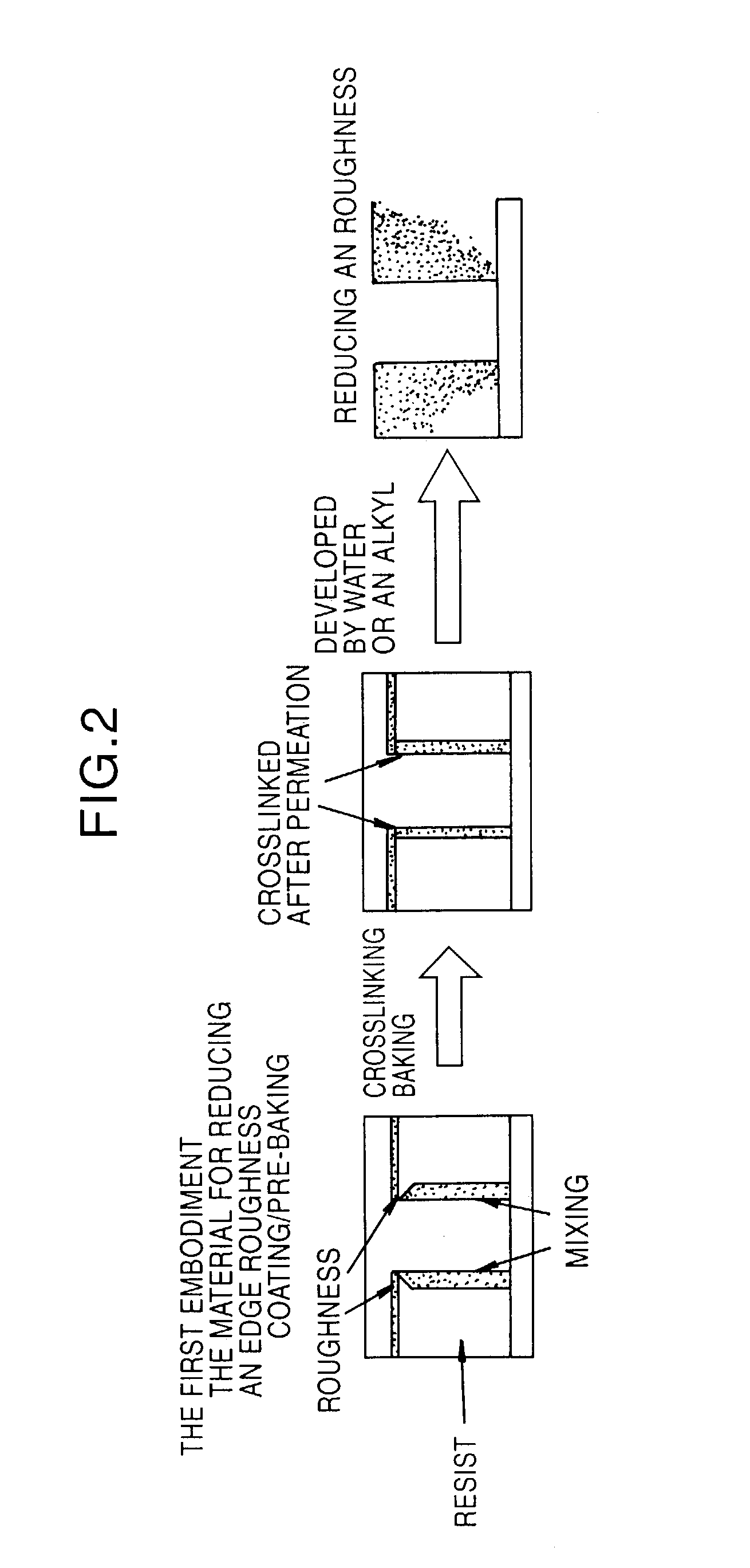

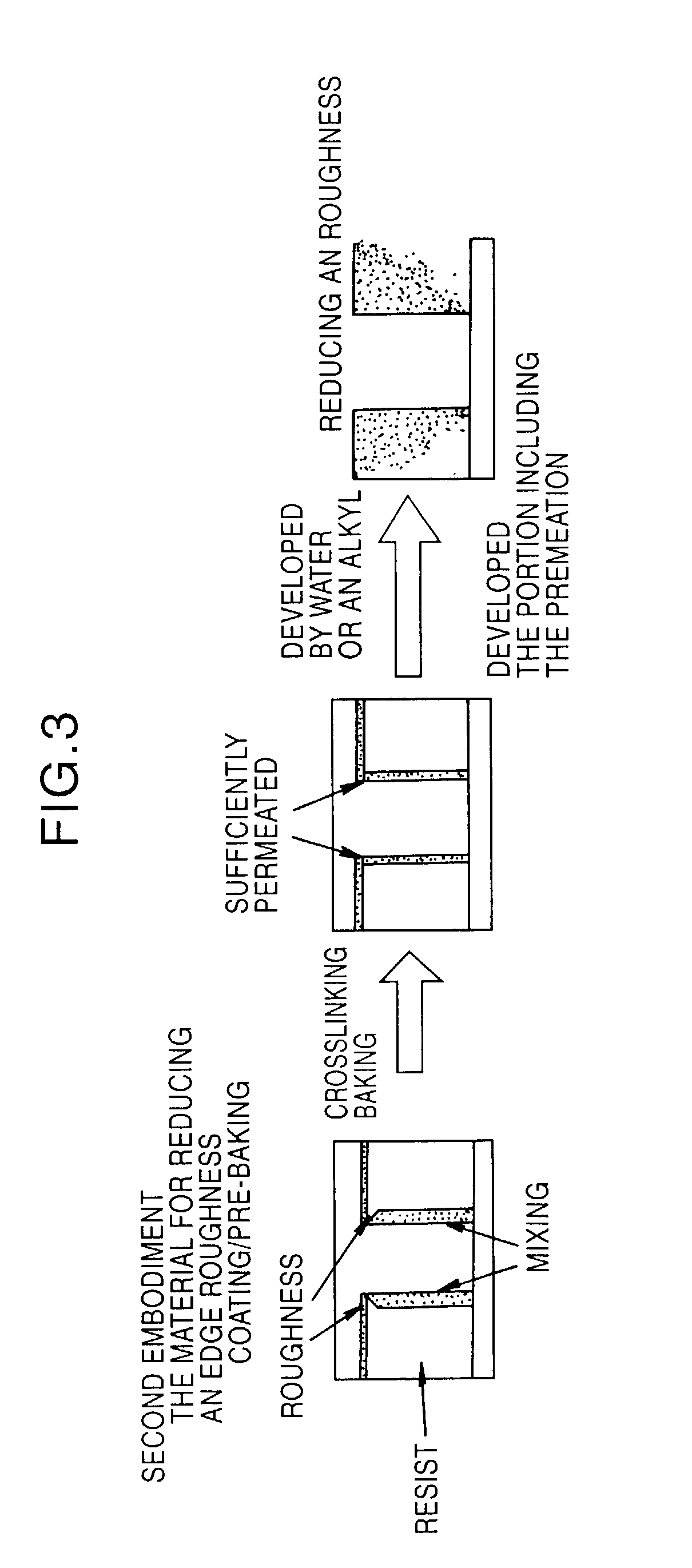

Resist pattern-improving material and a method for preparing a resist pattern by using the same

InactiveUS7416837B2Reduce edge roughnessResist materialBio-organic fraction processingSemiconductor/solid-state device manufacturingResistLaser light

Owner:FUJITSU LTD

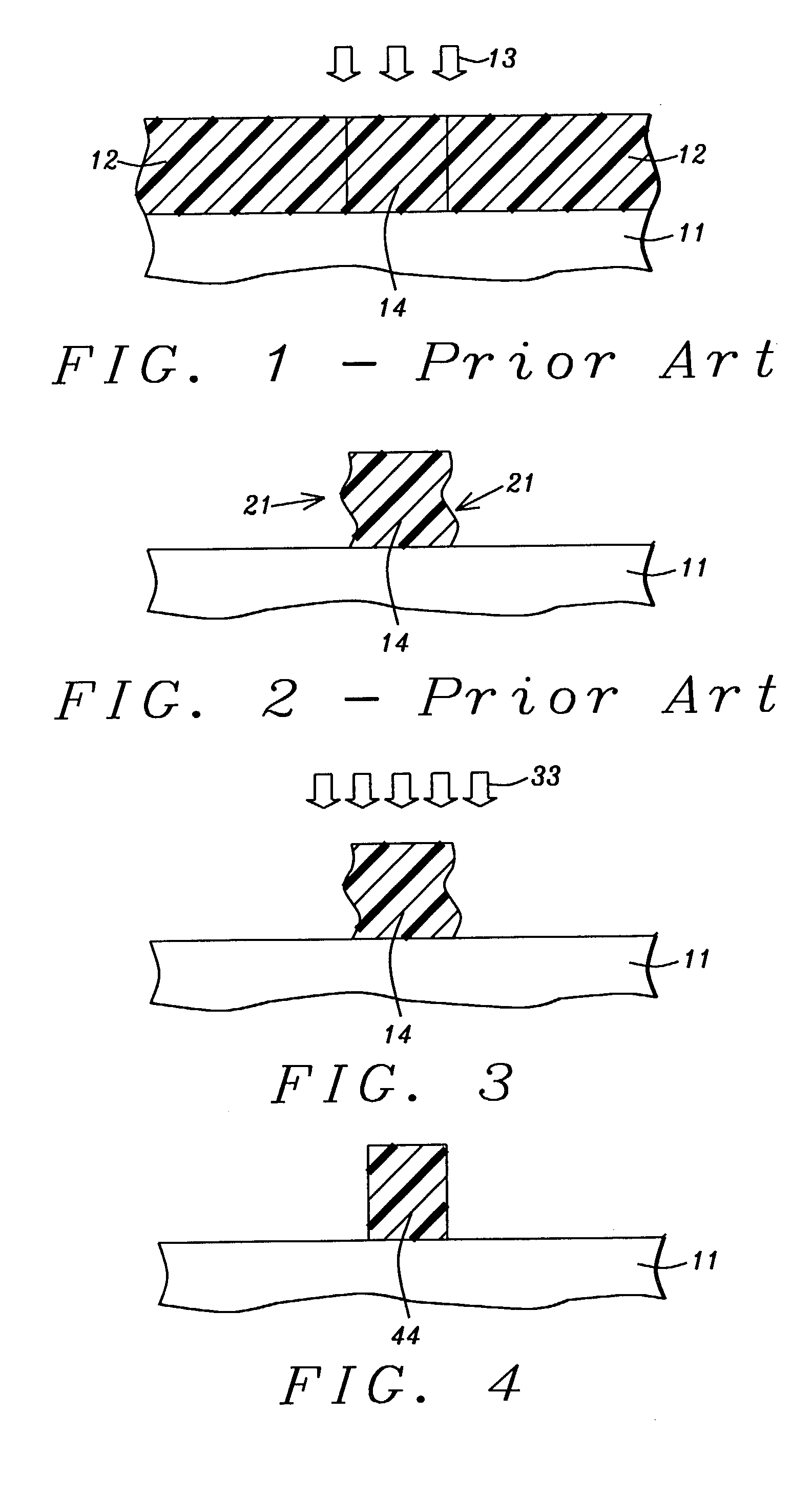

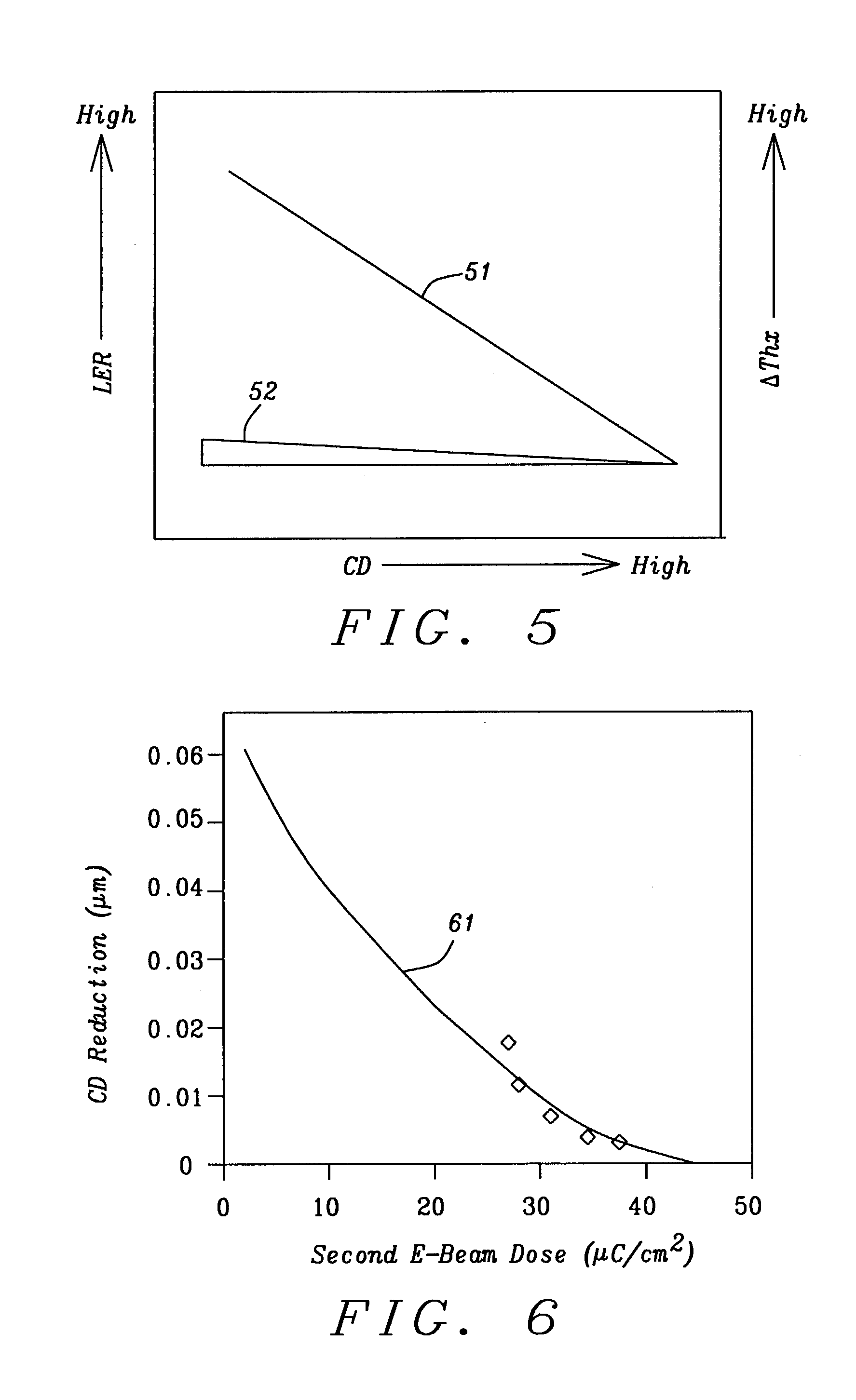

Method to form reduced dimension pattern with good edge roughness

InactiveUS20040214109A1Minimal edge roughnessImprove edge roughnessElectric discharge tubesElectrographic processes using photoelectrophoresisEngineeringHeat treating

As feature sizes approach 0.1 .mu.m or smaller, reduction of line edge roughness (LER) becomes increasingly important. Significant reductions in edge roughness have been achieved by applying a second Ebeam exposure after the initial one thatis used to define the pattern. After this second blanket exposure a longer heat treatment and a stronger development process than before are used. In addition to reducing edge roughness the disclosed treatment allows the CD to be reduced under tight control since the amount of CD reduction is proportional to the second Ebeam dosage.

Owner:HEADWAY TECH INC

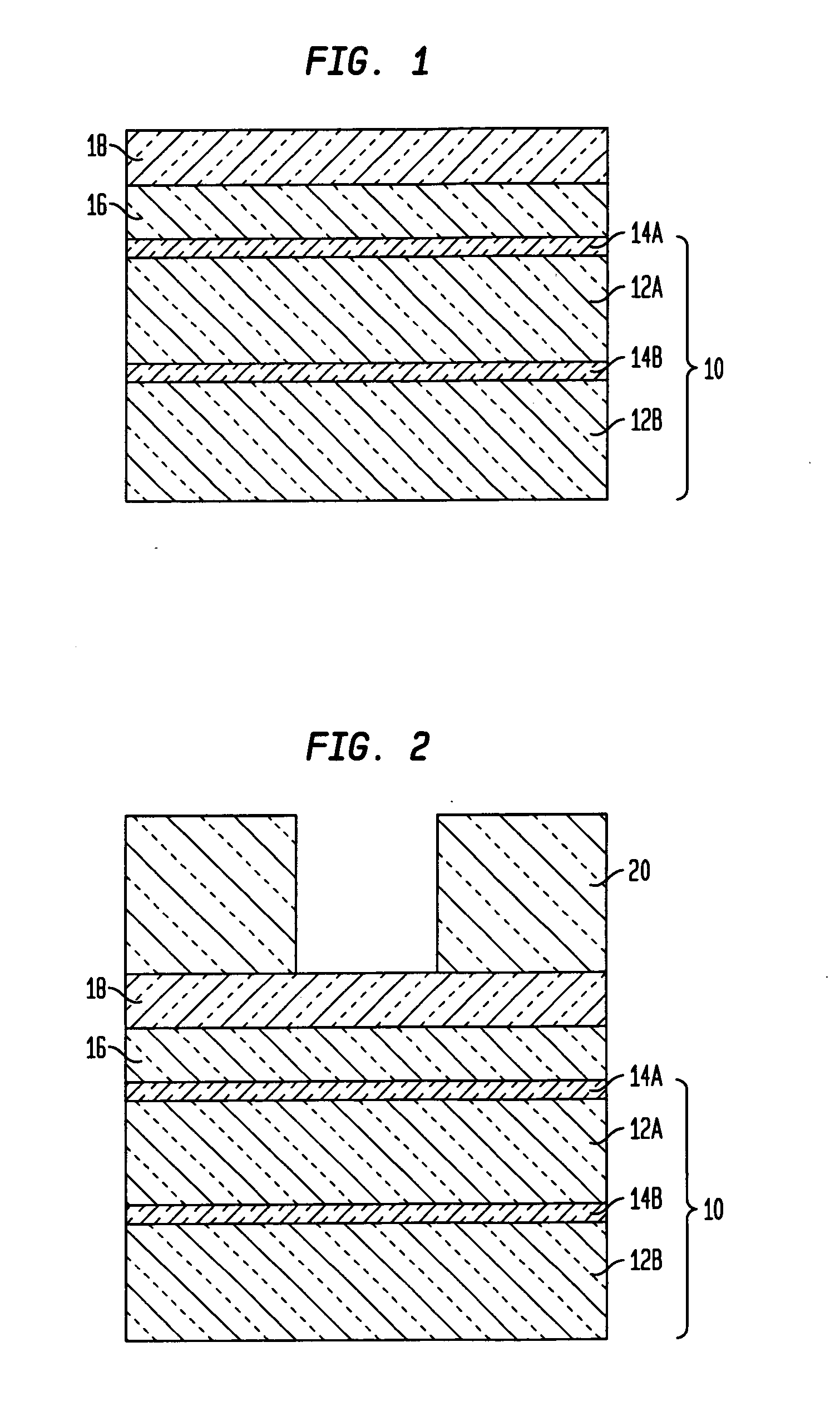

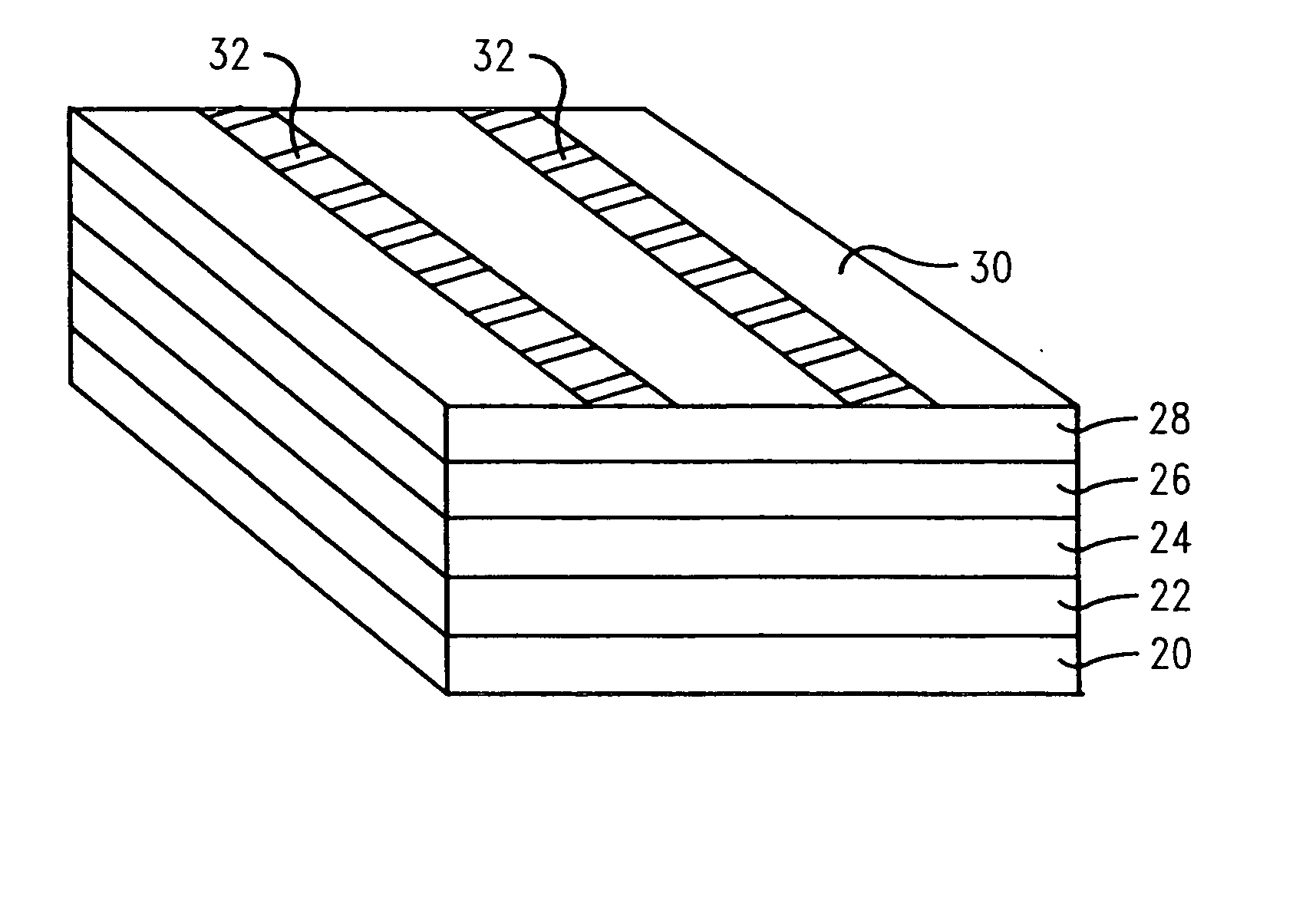

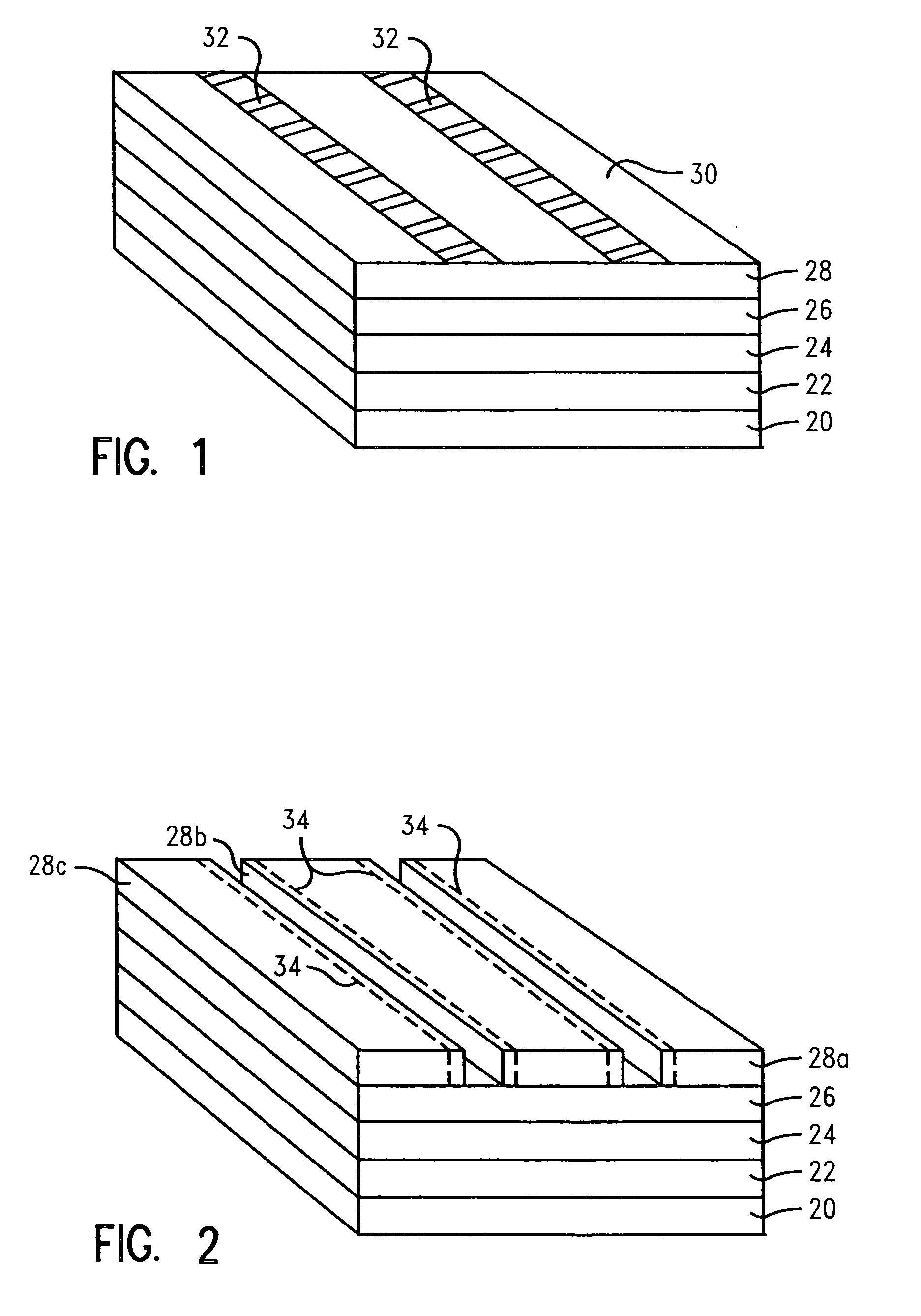

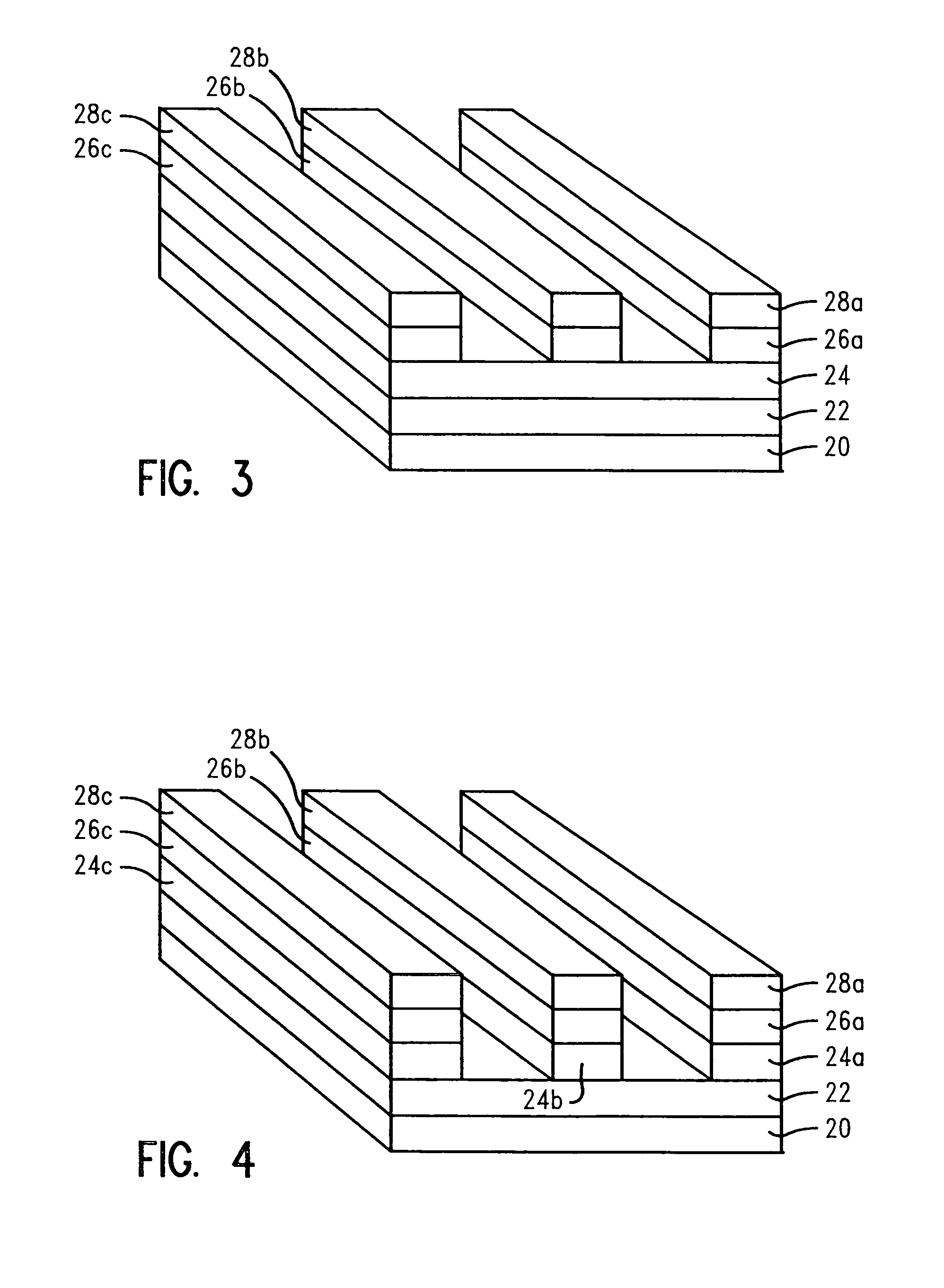

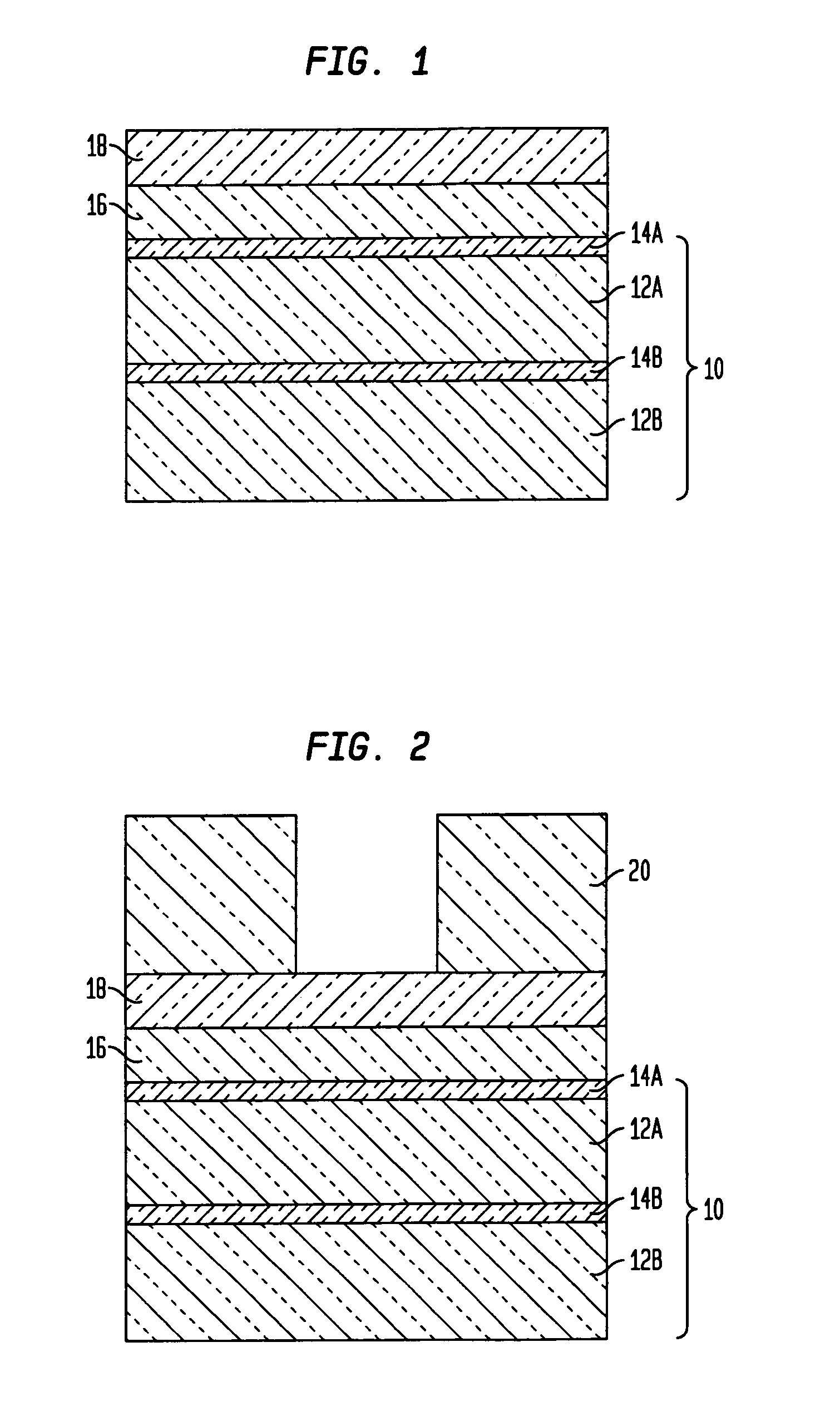

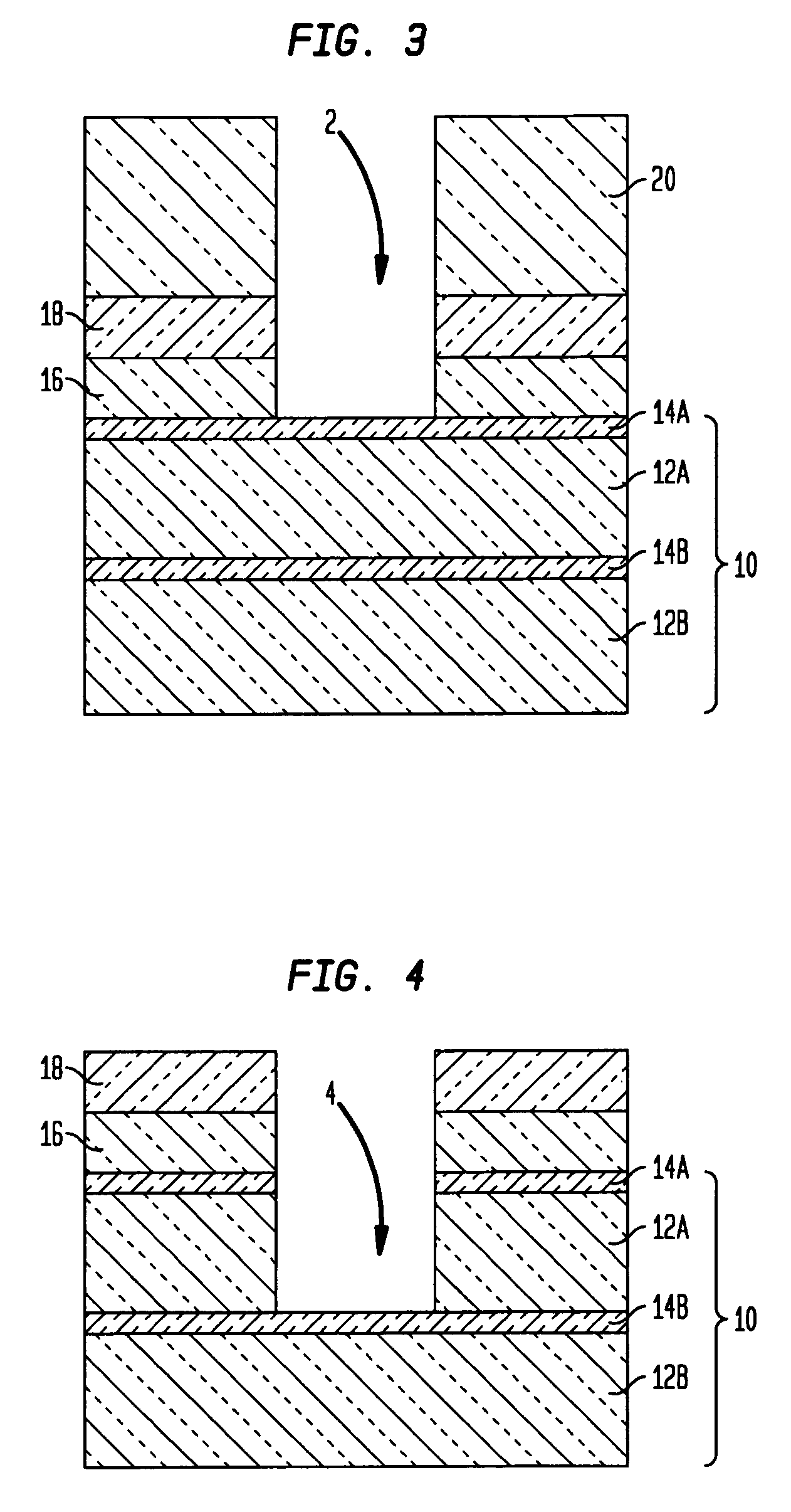

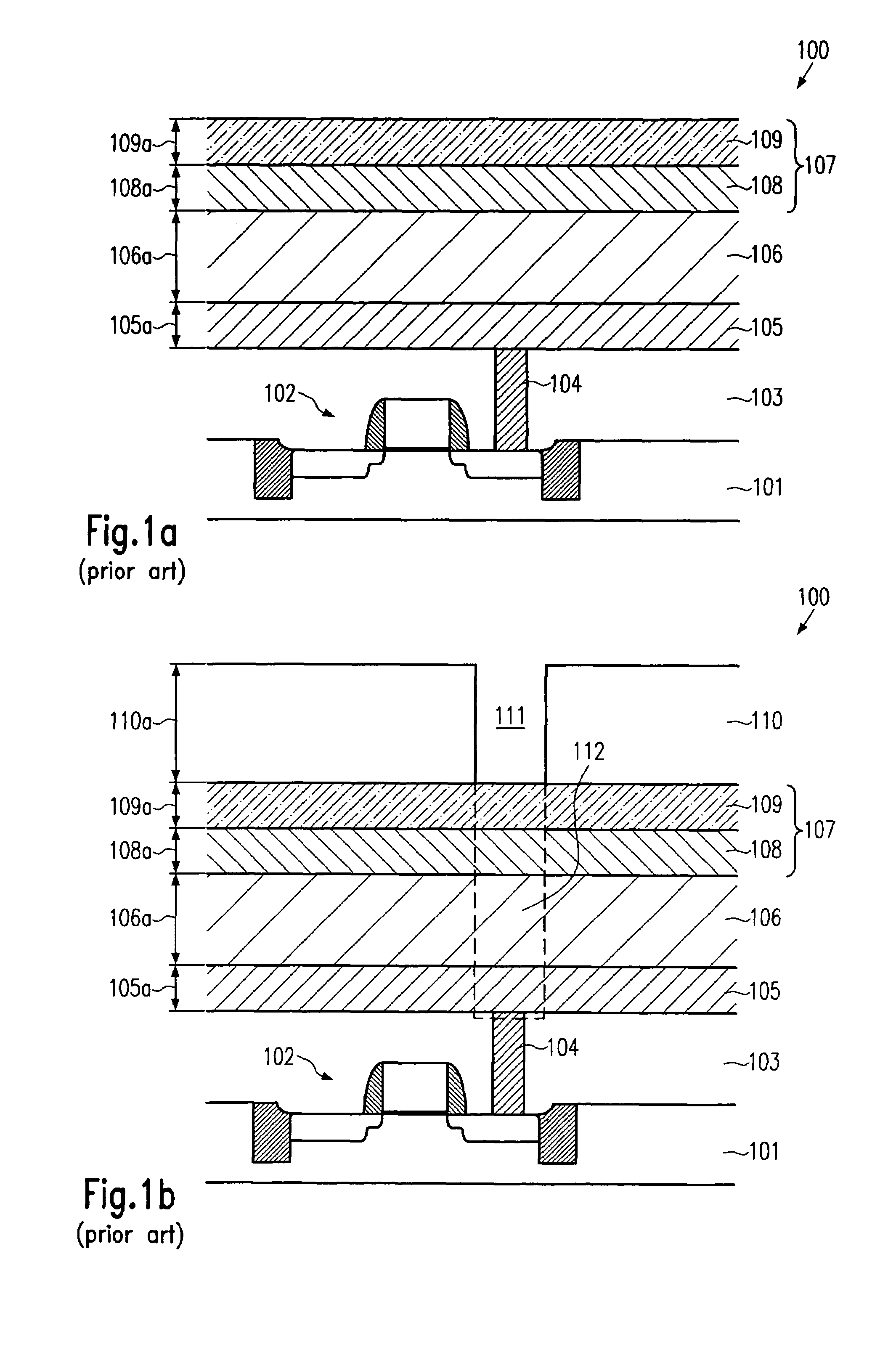

Structures and methods for low-k or ultra low-k interlayer dielectric pattern transfer

InactiveUS20070259291A1Expand line spacingIncreasing the thicknessElectric discharge tubesDecorative surface effectsResistDielectric

The present invention relates to improved methods and structures for forming interconnect patterns in low-k or ultra low-k (i.e., having a dielectric constant ranging from about 1.5 to about 3.5) interlevel dielectric (ILD) materials. Specifically, reduced lithographic critical dimensions (CDs) (i.e., in comparison with target CDs) are initially used for forming a patterned resist layer with an increased thickness, which in turn allows use of a simple hard mask stack comprising a lower nitride mask layer and an upper oxide mask layer for subsequent pattern transfer. The hard mask stack is next patterned by a first reactive ion etching (RIE) process using an oxygen-containing chemistry to form hard mask openings with restored CDs that are substantially the same as the target CDs. The ILD materials are then patterned by a second RIE process using a nitrogen-containing chemistry to form the interconnect pattern with the target CDs.

Owner:GLOBALFOUNDRIES INC

Resist-protective film-forming composition and patterning process

ActiveUS20130143163A1High sensitivityReduce edge roughnessElectric discharge tubesSemiconductor/solid-state device manufacturingTectorial membraneAcenaphthylene

A pattern is printed by forming a photoresist layer on a wafer, forming a protective film thereon, exposure, and development. The protective film is formed from a composition comprising a copolymer of hydroxystyrene with acenaphthylene and / or vinylnaphthalene and a mixture of an alcohol solvent and an ether or aromatic solvent.

Owner:SHIN ETSU CHEM IND CO LTD

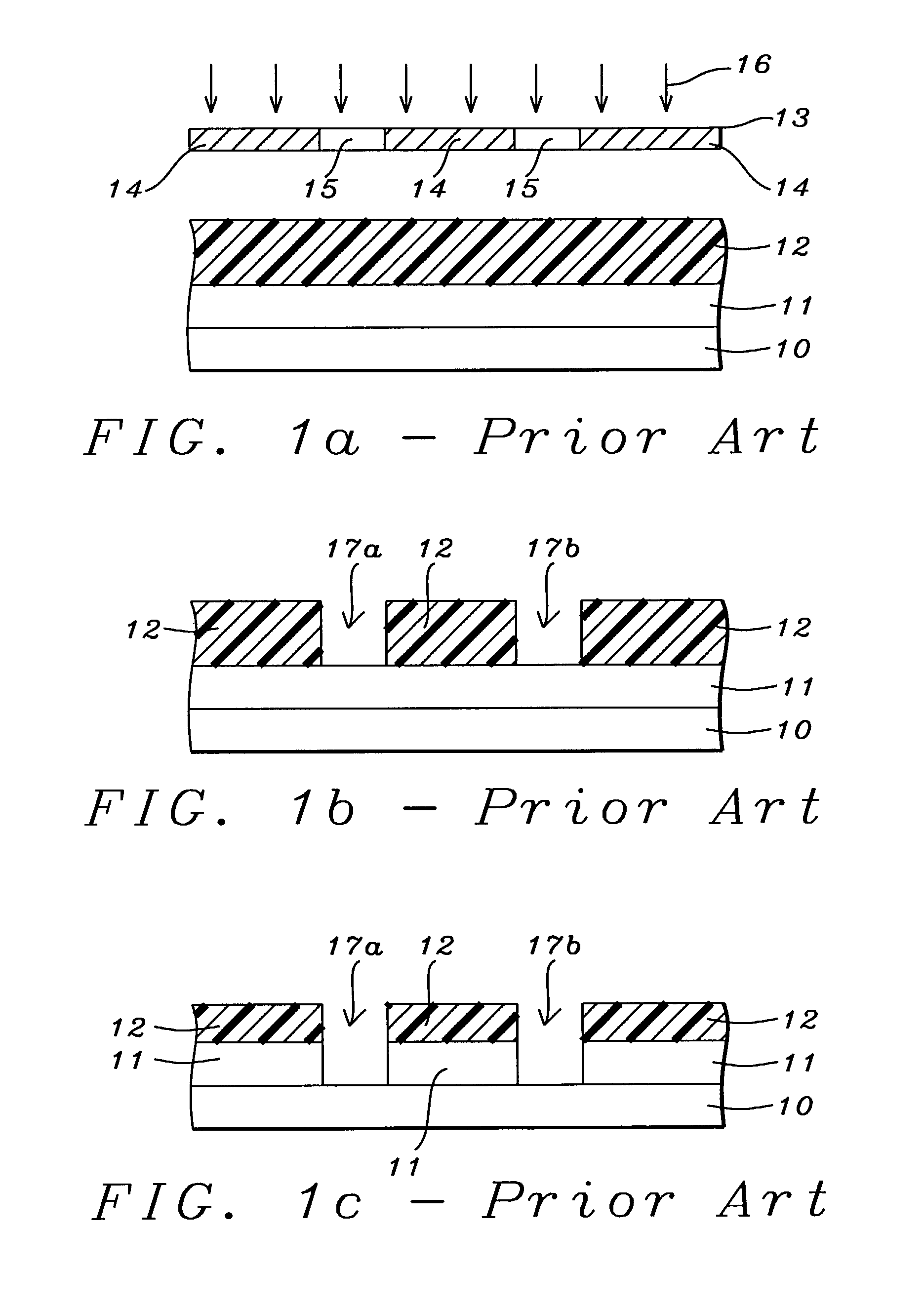

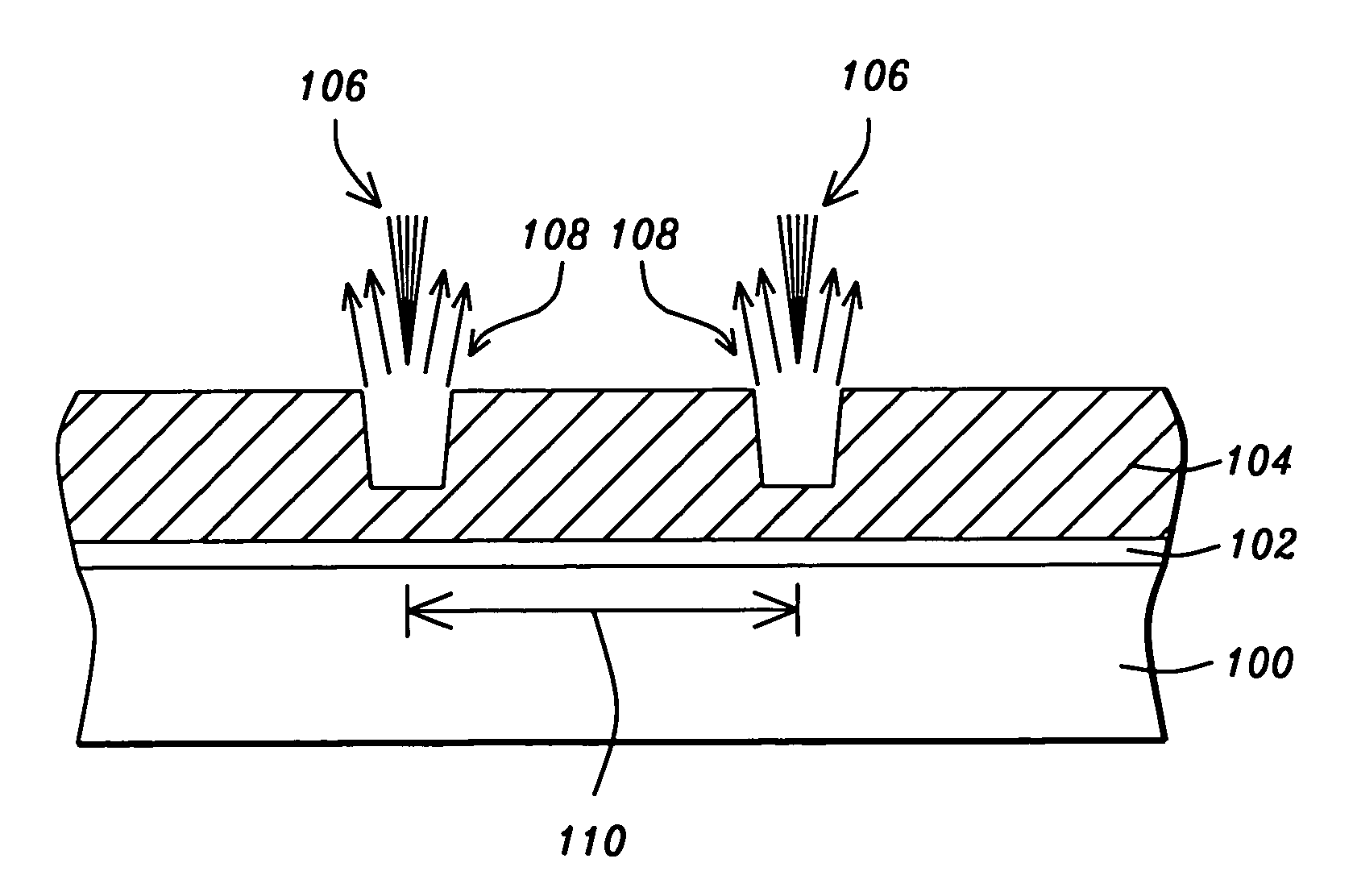

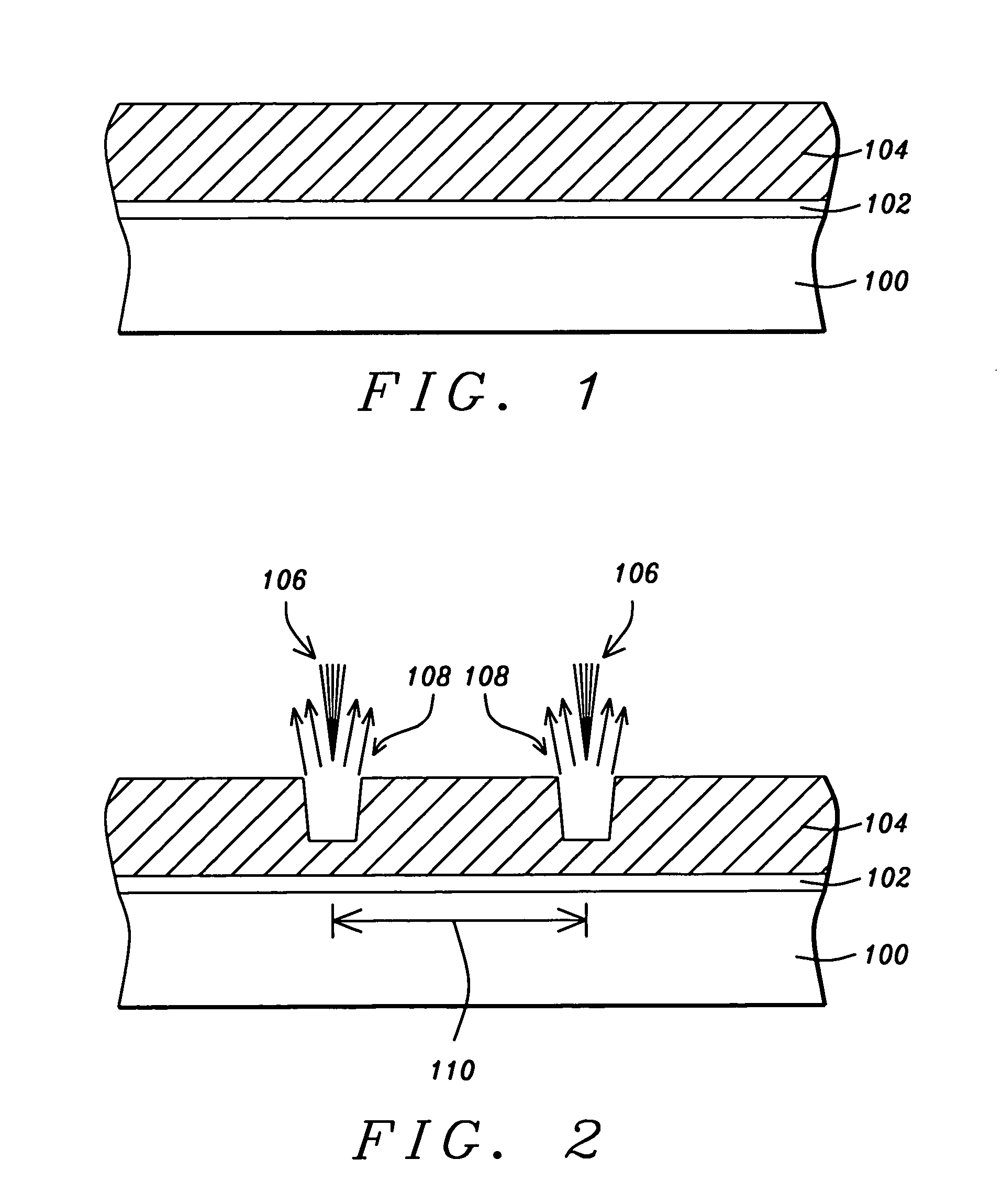

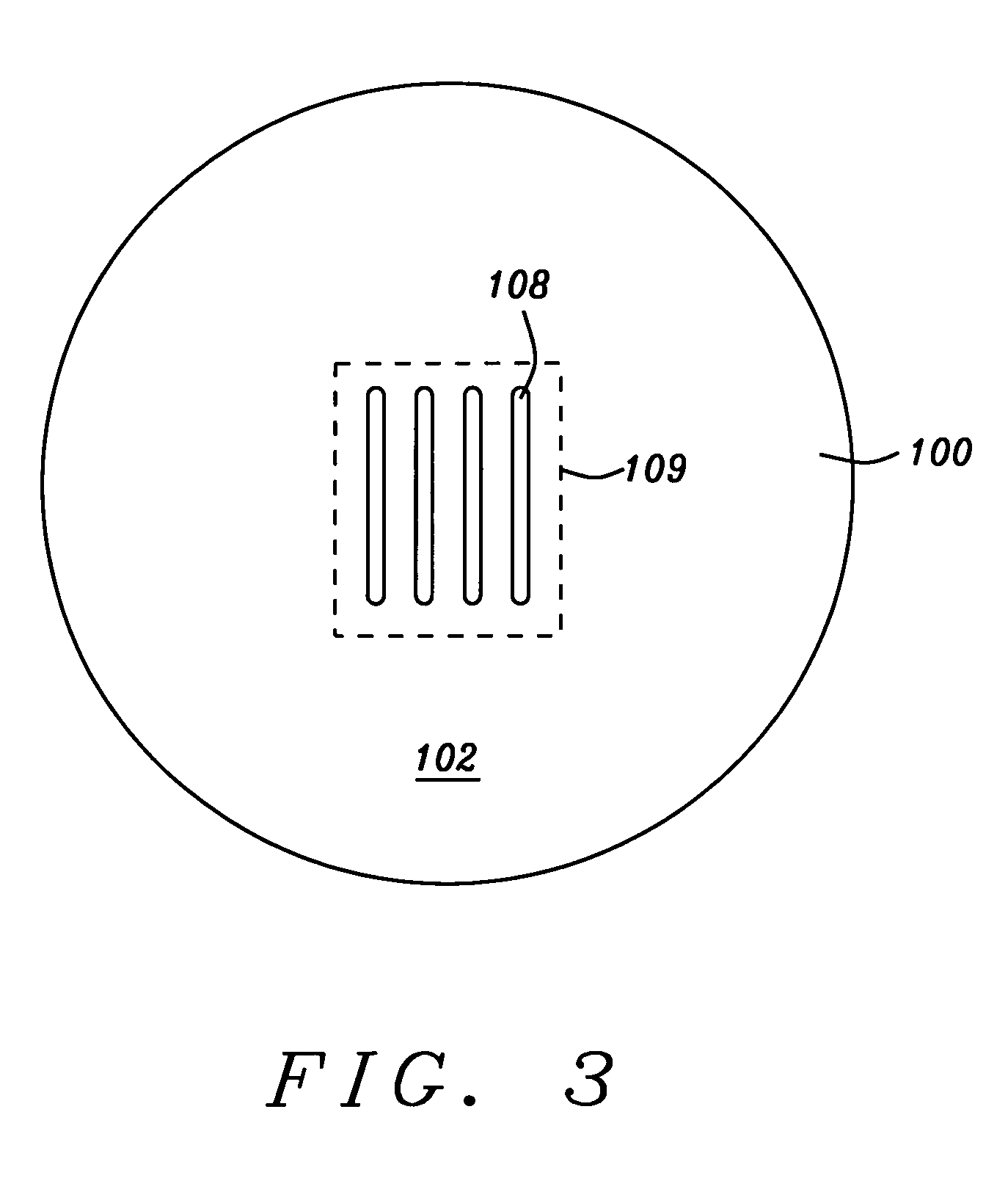

Calibration standard for critical dimension verification of sub-tenth micron integrated circuit technology

InactiveUS7049157B2Reduce roughnessReduce edge roughnessMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementScanning electron microscopeCritical dimension

A critical dimension control wafer for calibrating process control scanning electron microscopes is described. The test wafer provides one or more test structures each consisting of an array of parallel trenches precision micro-machined in a metal plate. The trenches are formed, preferably in an aluminum / copper alloy plate, using focused ion beam milling. The micro-machined trenches have lower width roughness and lower edge roughness compared to similar patterns form in polysilicon by conventional photo lithographic methods. In addition, electron charging in the scanning electron microscope, which produces distorted images, is essentially eliminated. The dimensions of the trenches and the metal lines between them have dimensions comparable to those of polysilicon lines used in sub-tenth micron integrated circuit process technology control wafer. The control wafers are calibrated using a calibrated laboratory grade scanning electron microscope. Once calibrated, the control wafers may be stock-piled for subsequent routine use as a high precision dimensional reference, in particular for calibrating and monitoring the stability of process line scanning electron microscopes.

Owner:TAIWAN SEMICON MFG CO LTD

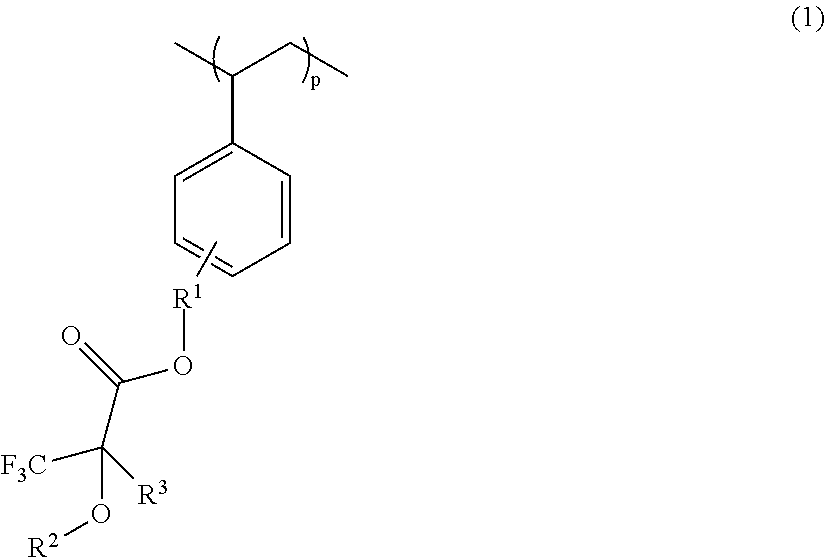

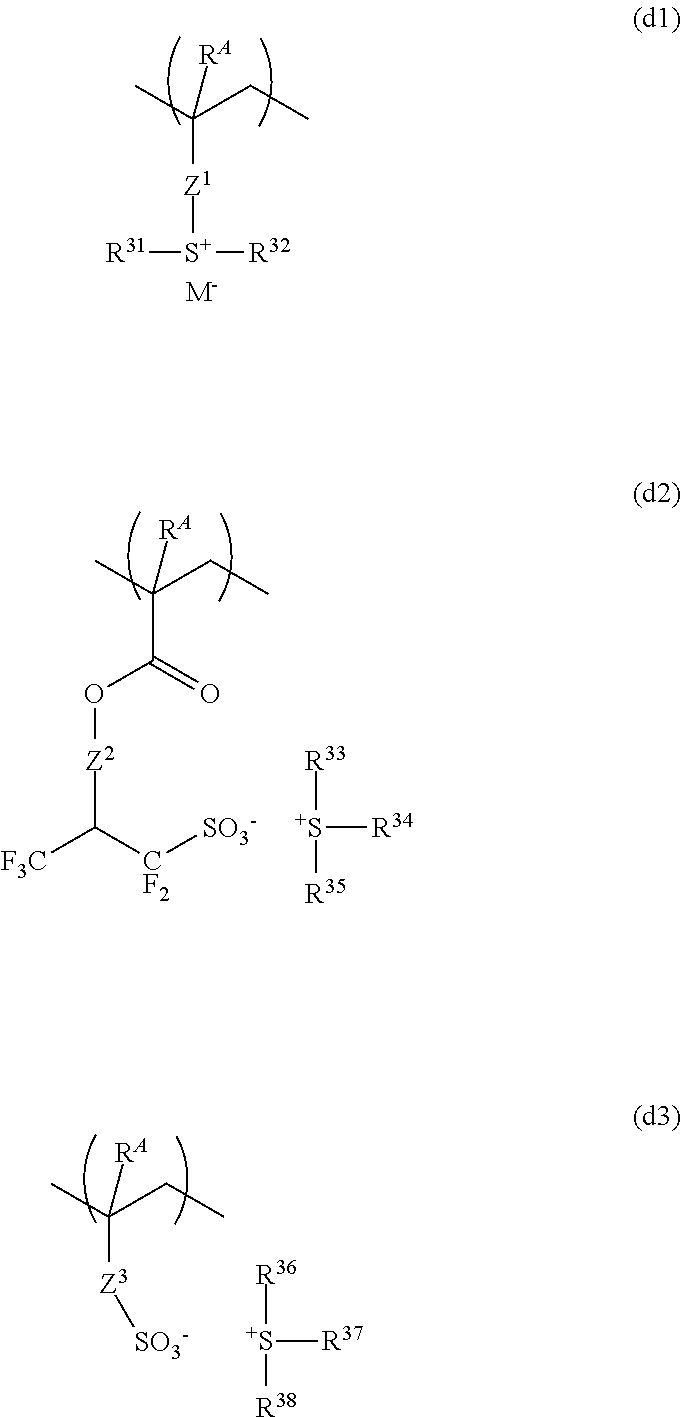

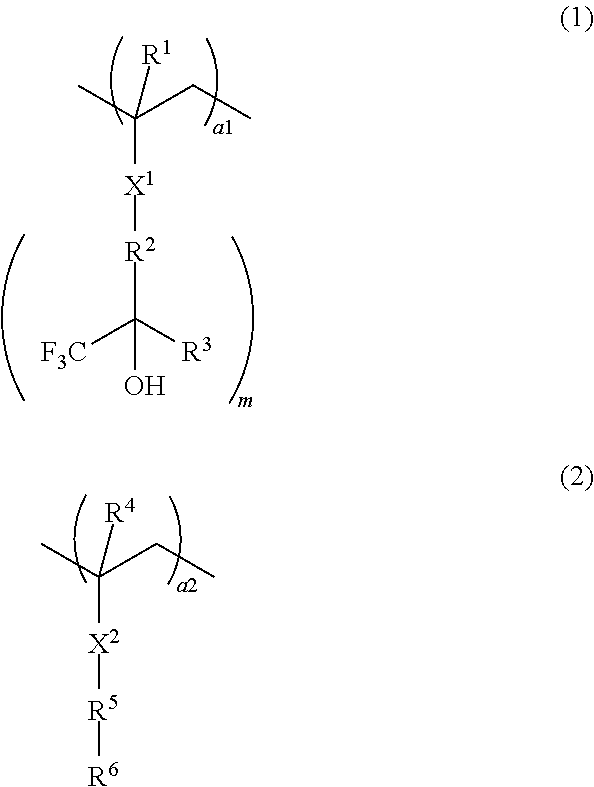

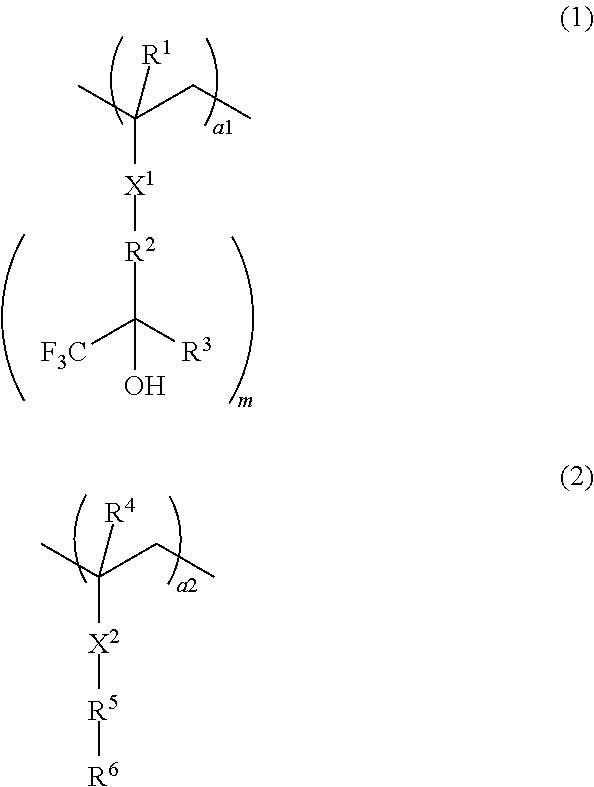

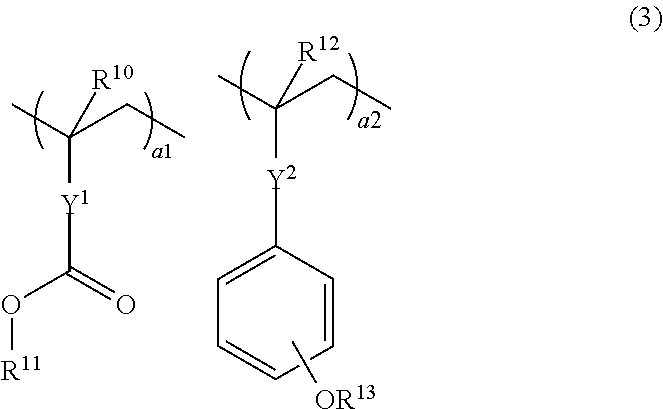

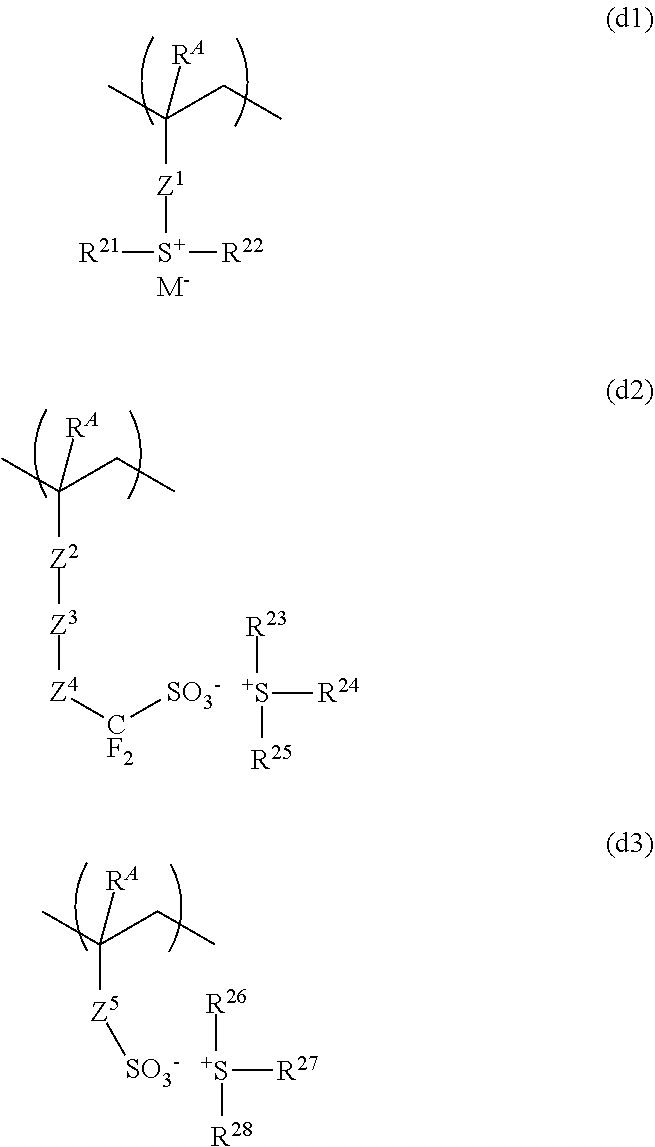

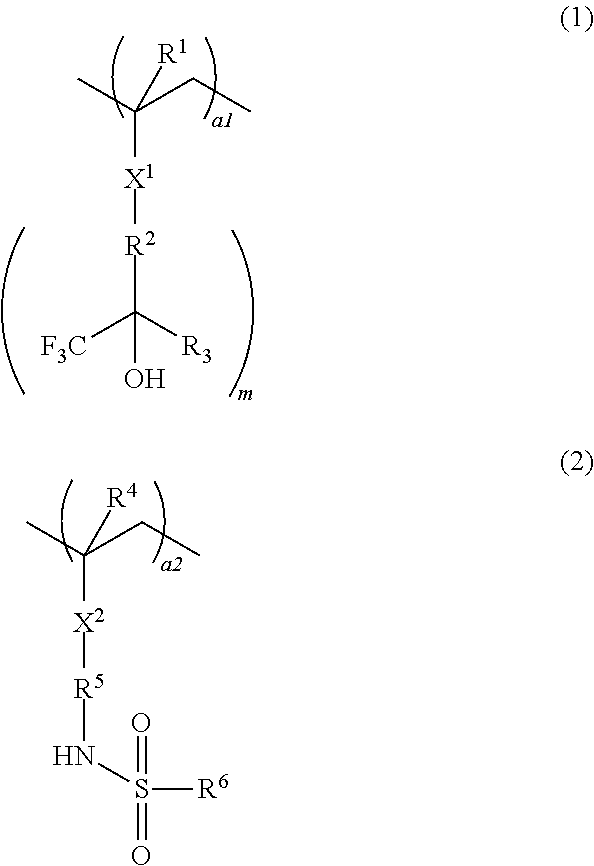

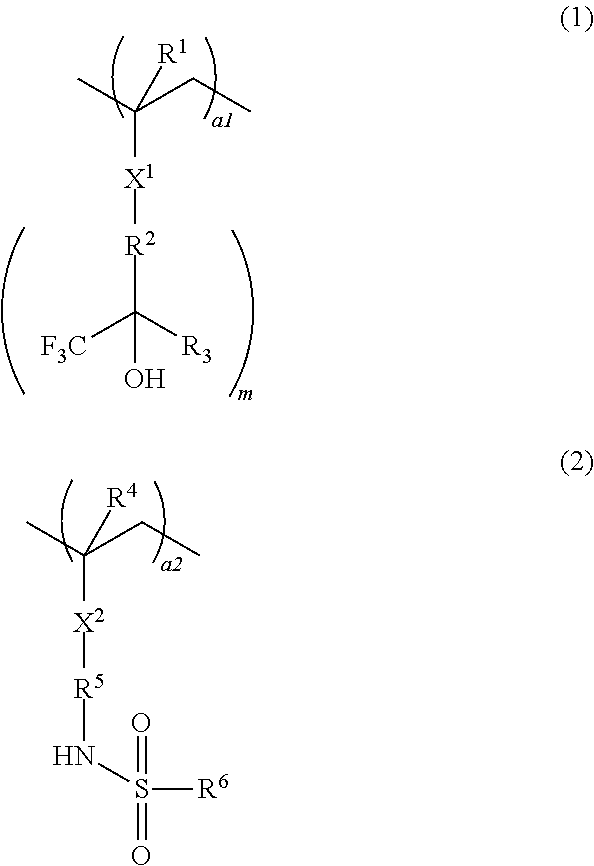

Resist composition, patterning process and polymer

ActiveUS20140178820A1Reduce edge roughnessInhibition formationPhotosensitive materialsElectric discharge tubesResistSolubility

An additive polymer comprising recurring styrene units having an ester group bonded to a CF3—C(OR2)—R3 group (wherein R2 is H, acyl or acid labile group, R3 is H, CH3 or CF3) such as 1,1,1,3,3,3-hexafluoro-2-propanol is added to a polymer capable of increasing alkali solubility under the action of acid to formulate a resist composition. The resist composition can minimize outgassing from a resist film during the EUV lithography and form a resist film having a hydrophilic surface sufficient to prevent formation of blob defects on the film after development.

Owner:SHIN ETSU CHEM IND CO LTD

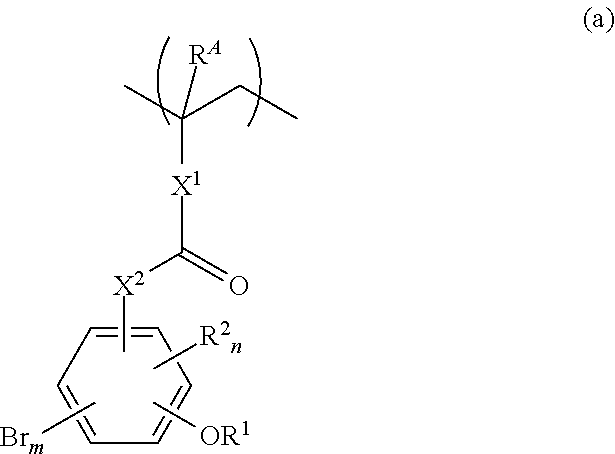

Resist composition and patterning process

ActiveUS20180373148A1High sensitivityImproved profilePhotomechanical coating apparatusPhotomechanical exposure apparatusPolymer sciencePhenol

A resist composition comprising a polymer comprising recurring units having an optionally substituted brominated phenol has advantages including high sensitivity, high resolution and reduced acid diffusion and forms a pattern of good profile with improved CDU.

Owner:SHIN ETSU CHEM IND CO LTD

Resist composition and patterning process

ActiveUS9152050B2Emission reductionInhibition formationSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusSolubilityResist

A polymer capable of increasing alkali solubility under the action of acid, as a base resin is blended with a polymer comprising recurring units derived from a styrene having 1,1,1,3,3,3-hexafluoro-2-propanol as a polymeric additive to formulate a resist composition. The photoresist film formed using the resist composition is effective for minimizing outgassing therefrom during the EUV lithography, reducing LWR after development, and suppressing formation of blob defects after development because of its hydrophilic surface.

Owner:SHIN ETSU CHEM IND CO LTD

Pattern forming method and method of manufacturing semiconductor devices

InactiveUS20070298615A1Reduce dispersionReduce line widthSemiconductor/solid-state device manufacturingPhotosensitive material processingResistVitrification

A pattern forming method is provided. The pattern forming method includes a first step of forming a resist pattern including a lactone group-containing skeleton above an etched layer provided on a substrate; a second step of performing plasma processing using a hydrogen-containing gas to lower a glass transition temperature or a softening point of the resist pattern; and a third step of transferring the resist pattern after the plasma processing to the etched layer by etching, and forming the pattern of the etched layer.

Owner:SONY CORP +1

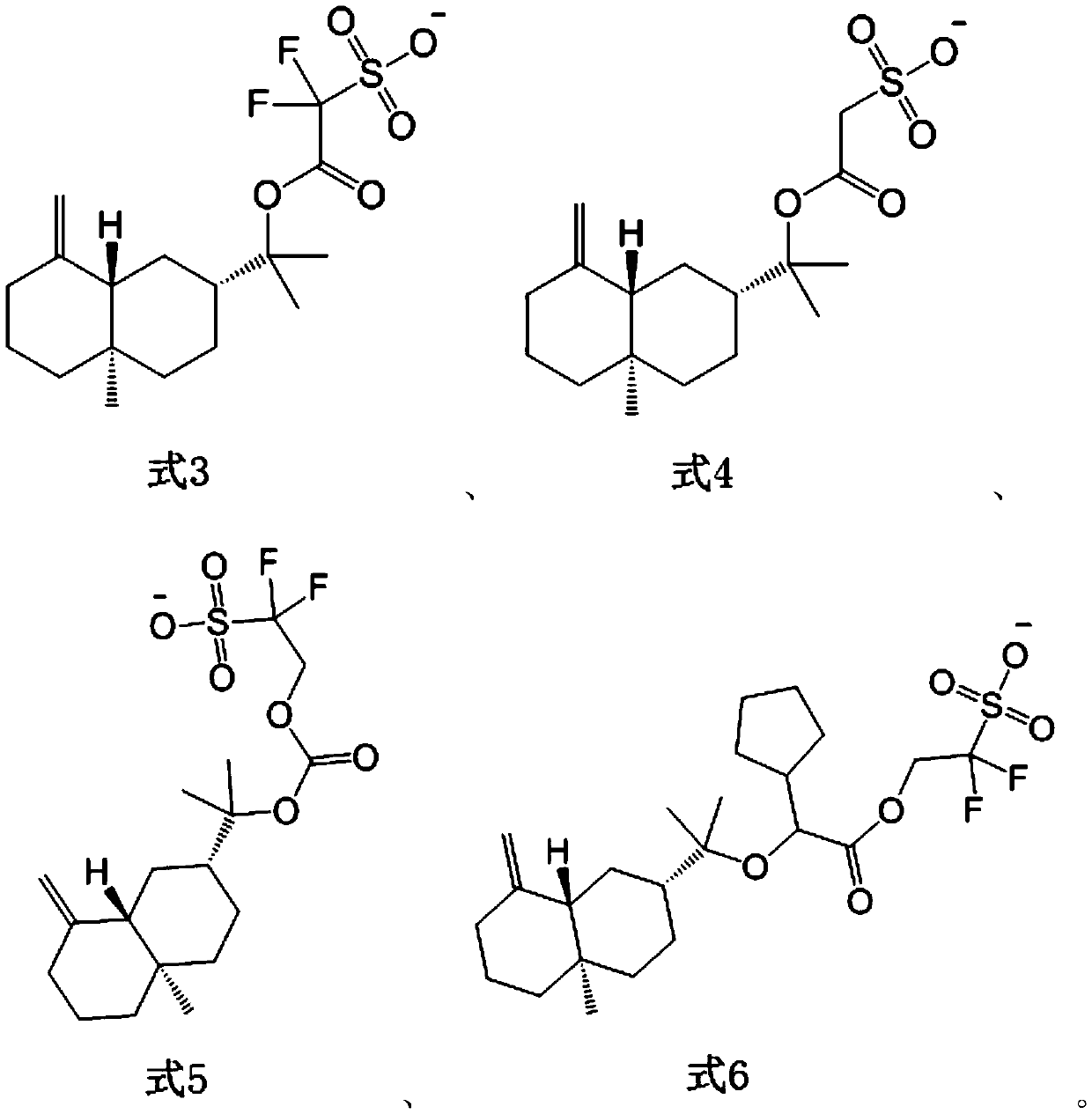

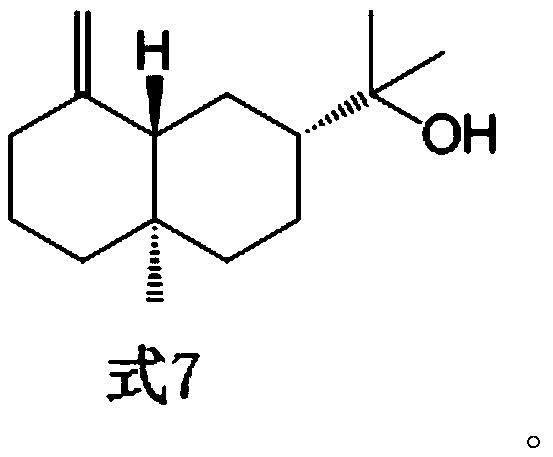

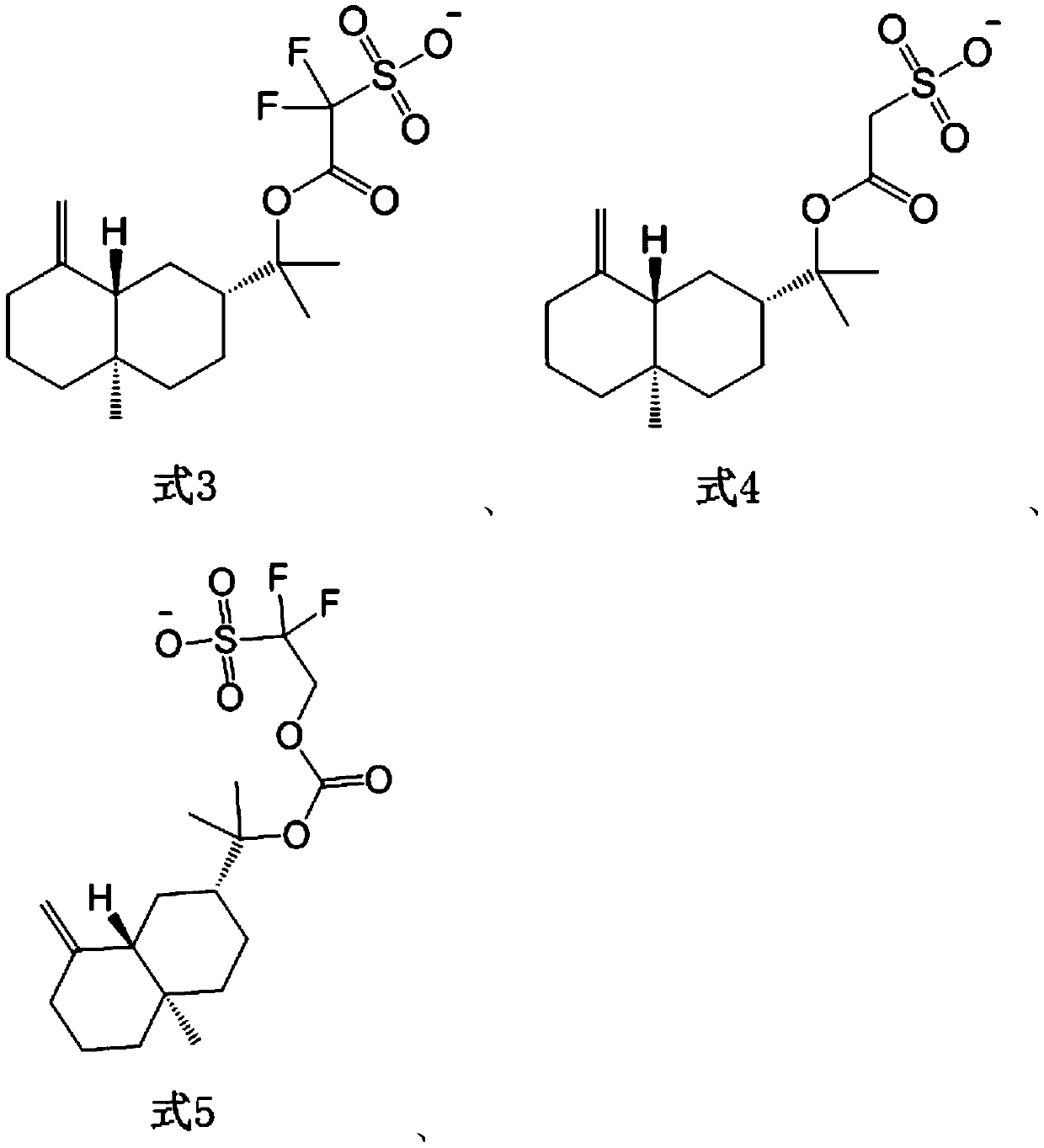

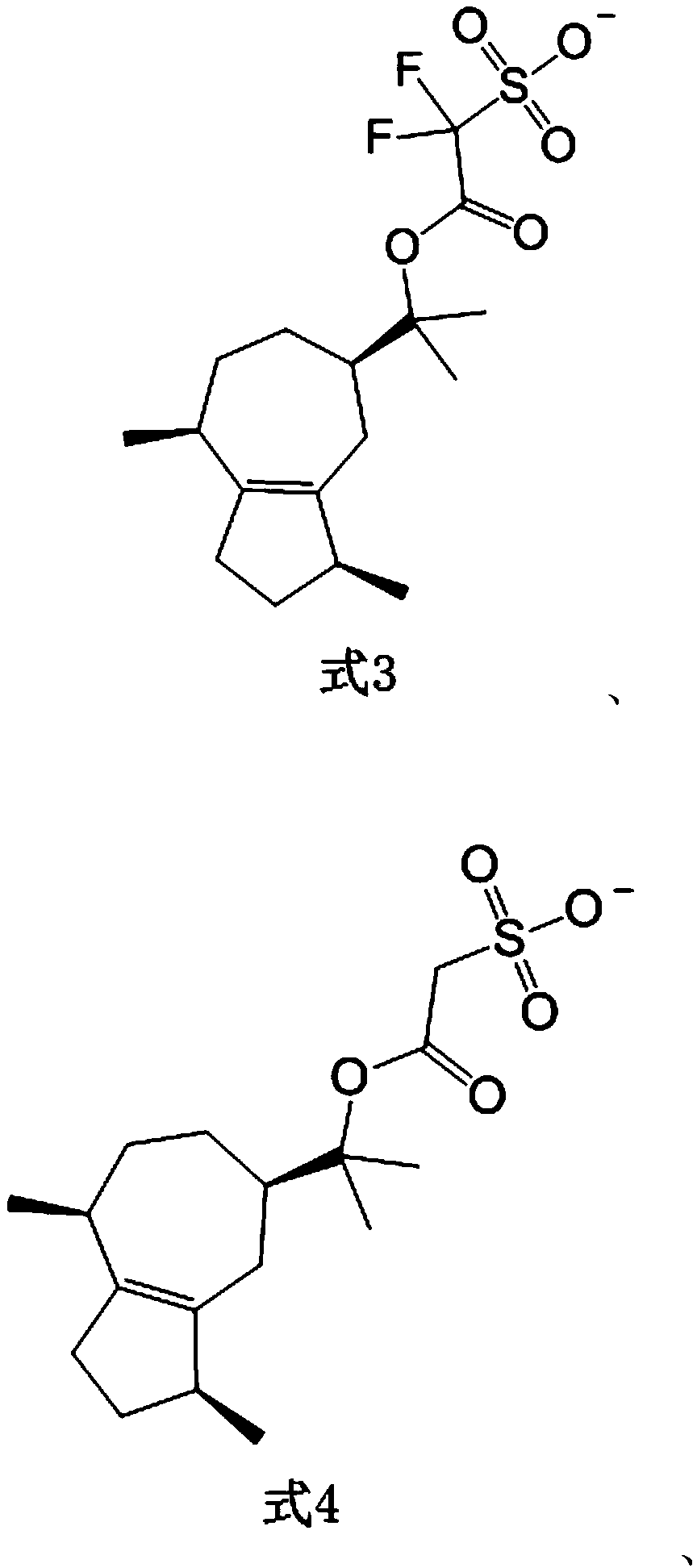

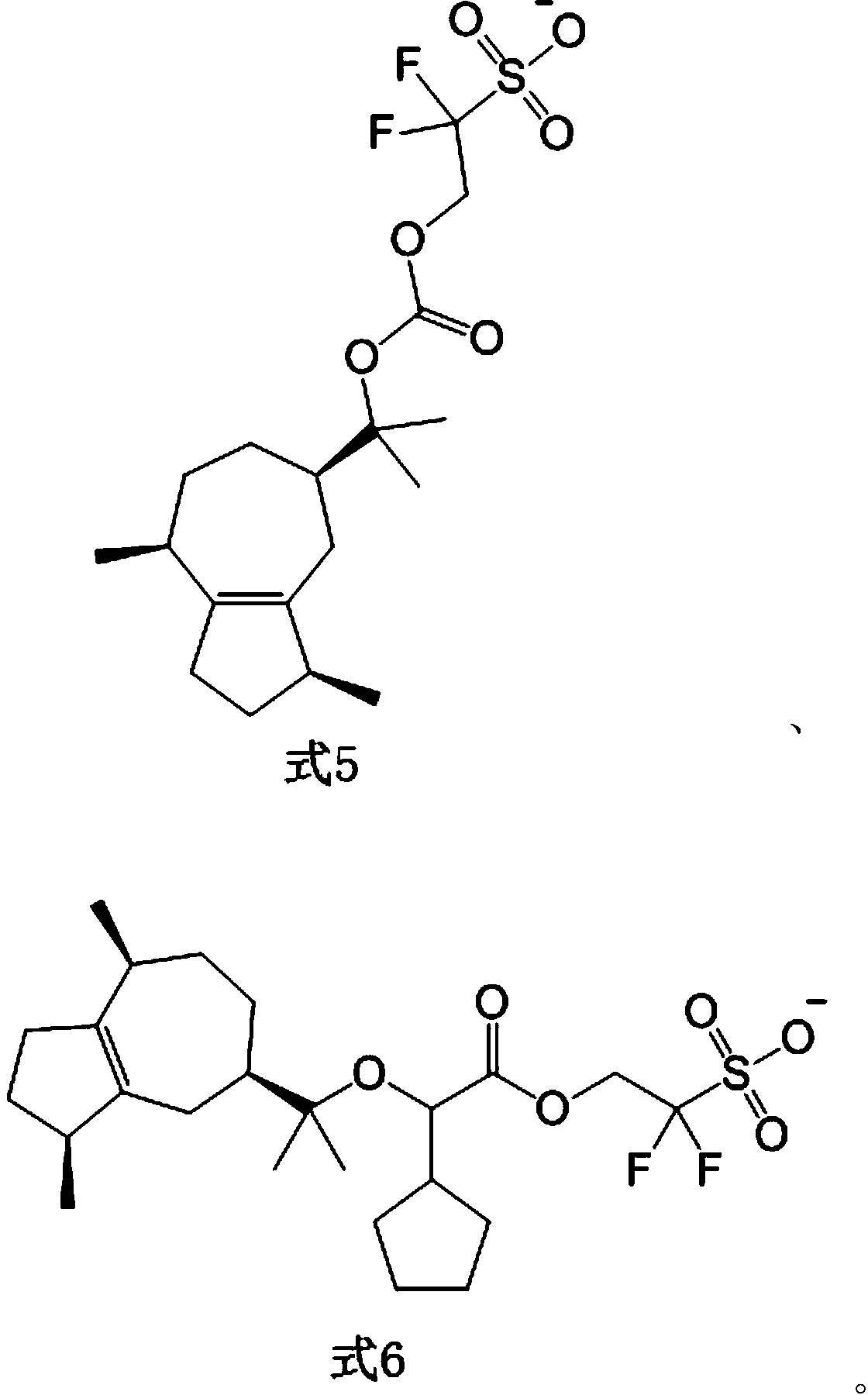

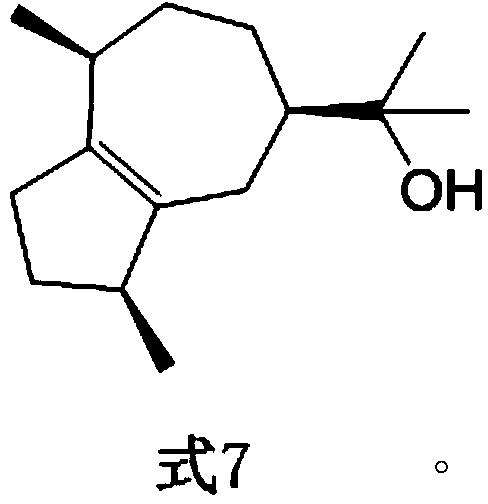

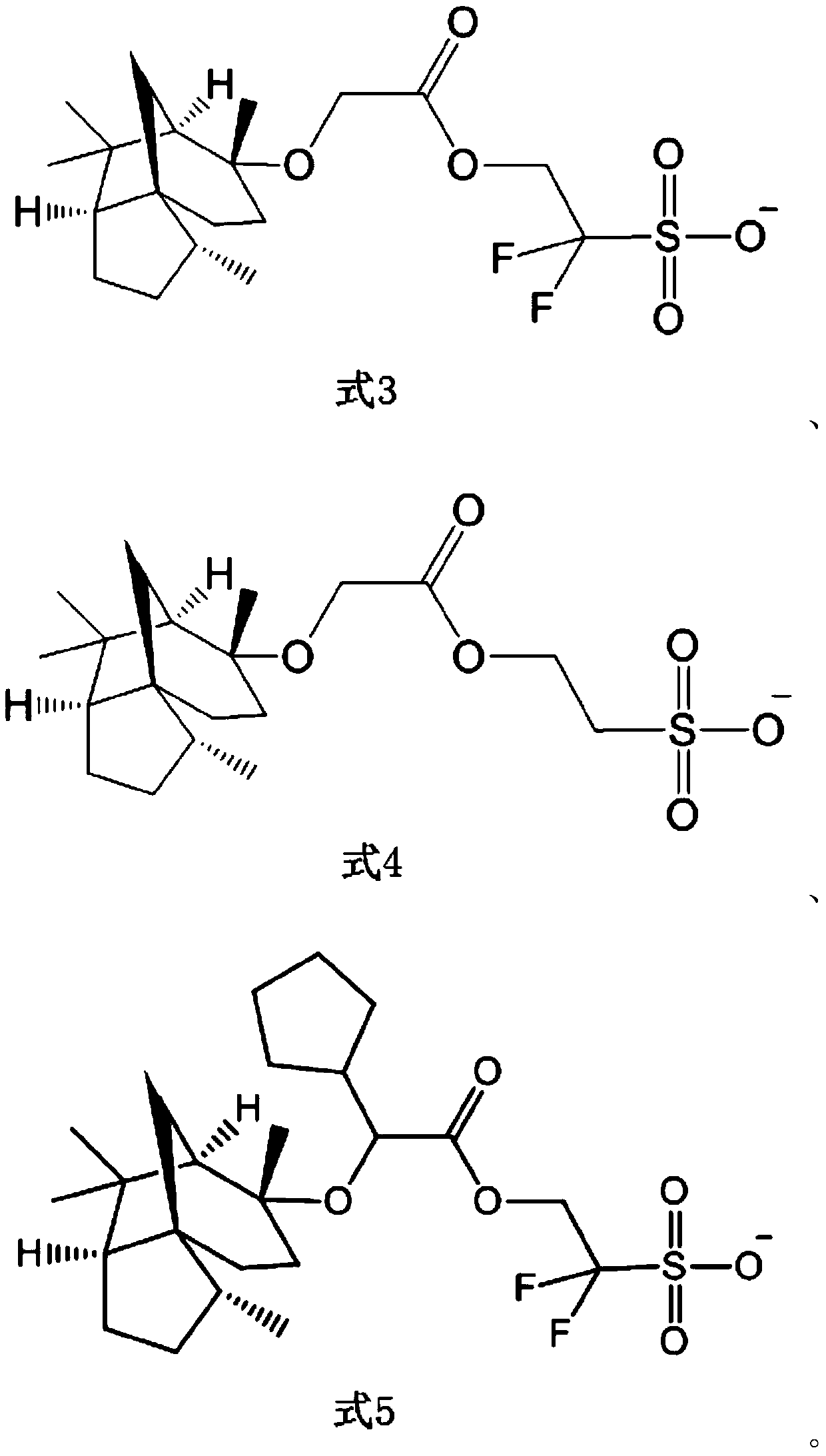

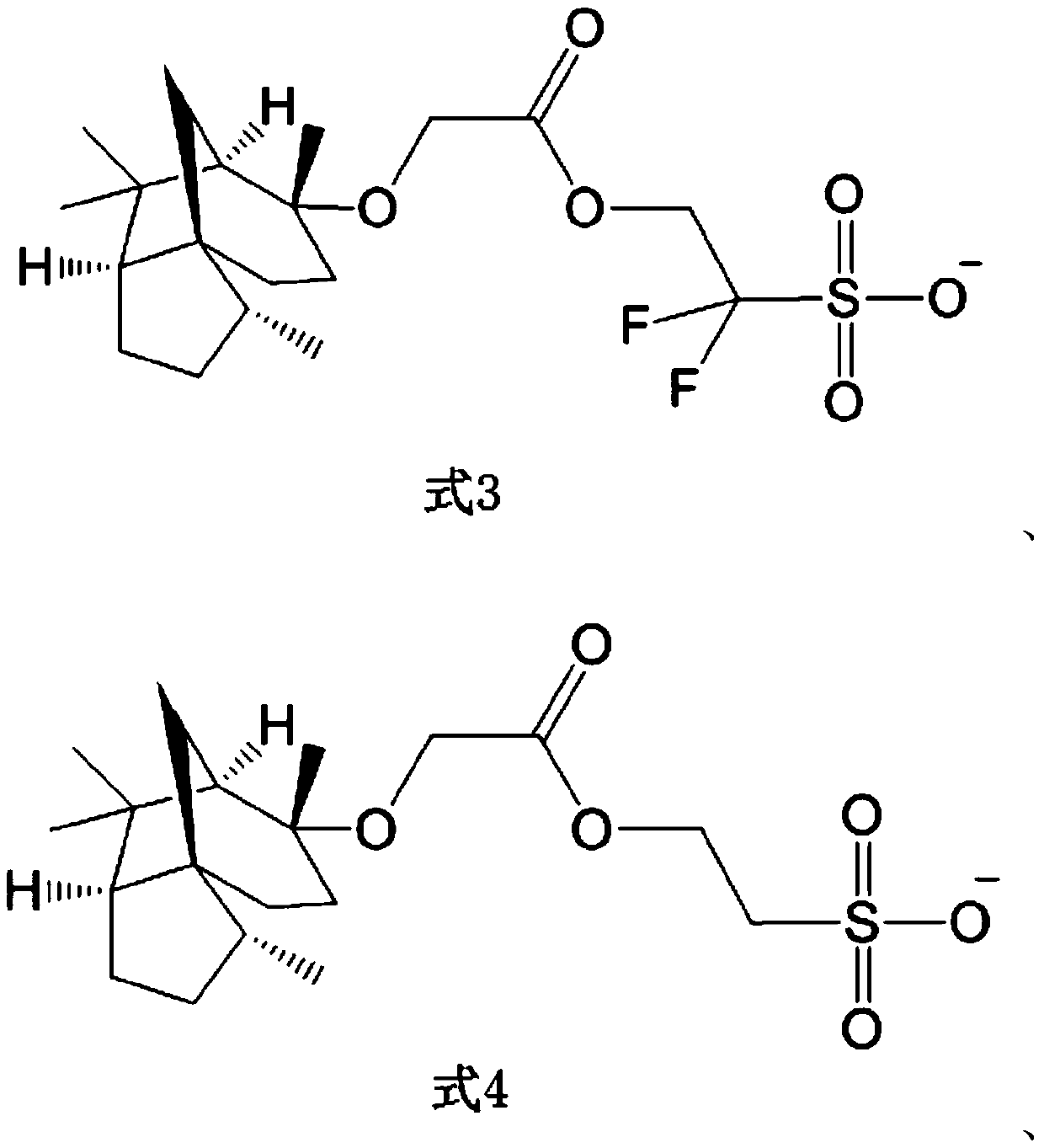

Sulfonium onium salt photoacid generator containing beta-eudesmol structure, and preparation method thereof

InactiveCN111138331AImprove hydrophilic-lipophilic balanceImprove diffusivitySulfonic acids salts preparationPhotosensitive materials for photomechanical apparatusOrganic solventHydrogen atom

The invention relates to the technical field of photoresist, and particularly discloses a sulfonium onium salt photoacid generator containing a beta-cineole structure, and a preparation method thereof. The photoacid generator includes an anion and a cation, the anion and the cation have structures represented by formulas shown in the description; and in the formulas, R represents an alkyl group, acycloalkyl group, a heteroalkyl group, or a heterocycloalkyl group, and P1, P2, and P3 each independently represent a hydrogen atom or an optionally substituted alkyl group having 1 to 12 carbon atoms. The photoacid generator prepared by the invention has good hydrophilicity, can improve the solubility in an organic solvent, and can effectively inhibit the diffusion of acids. The invention further provides the preparation method of the sulfonium salt photoacid generator containing the beta-cineole structure. Beta-cineole is used as a reaction initiator to react and then reacts with sulfoniumhalide to obtain the sulfonium salt photoacid generator containing the beta-cineole structure, so the preparation method is simple.

Owner:上海博栋化学科技有限公司

Method for reducing feature line edge roughness

InactiveUS20060154184A1Reduced line edge roughnessReduce roughnessSemiconductor/solid-state device manufacturingPhotosensitive material processingIon bombardmentPlasma treatment

A method of patterning a feature in a substrate to reduce edge roughness comprises forming a resist layer overlying a substrate, exposing the resist layer to create an image of a feature, and developing the exposed resist layer to leave a portion of the resist layer that creates the image of the feature. The method then includes treating the exposed resist layer with a plasma to cure the portion of the resist layer creating the feature image. The plasma treatment has an ion bombardment level insufficient to substantially etch the underlying substrate. The method then includes etching the underlying substrate to create the feature.

Owner:IBM CORP +1

Sulfonium onium salt photoacid generator containing guaiacol structure and preparation method thereof

PendingCN111056980AImprove hydrophilic-lipophilic balanceThe synthesis process is simpleSulfonic acids salts preparationOrganic solventGuaiacol

The invention relates to the technical field of photoresist, and particularly discloses a sulfonium onium salt photoacid generator containing a guaiol structure and a preparation method thereof. The photoacid generator includes an anion and a cation, the anion and the cation each having a structure in which R represents an alkyl group, a cycloalkyl group, a heteroalkyl group, or a heterocycloalkylgroup, and P1, P2, and P3 each independently represent a hydrogen atom or an optionally substituted alkyl group having 1 to 12 carbon atoms. The photoacid generator prepared by the invention has goodhydrophilicity, can improve the solubility in an organic solvent, and can effectively inhibit the diffusion of acid. The invention also provides a preparation method of the sulfonium onium salt photoacid generator, guaiacol is used as a reaction initiator for reaction and then reacts with sulfonium halide to obtain a sulfonium onium salt compound, and the preparation method of the sulfonium oniumsalt photoacid generator is simple.

Owner:上海博栋化学科技有限公司

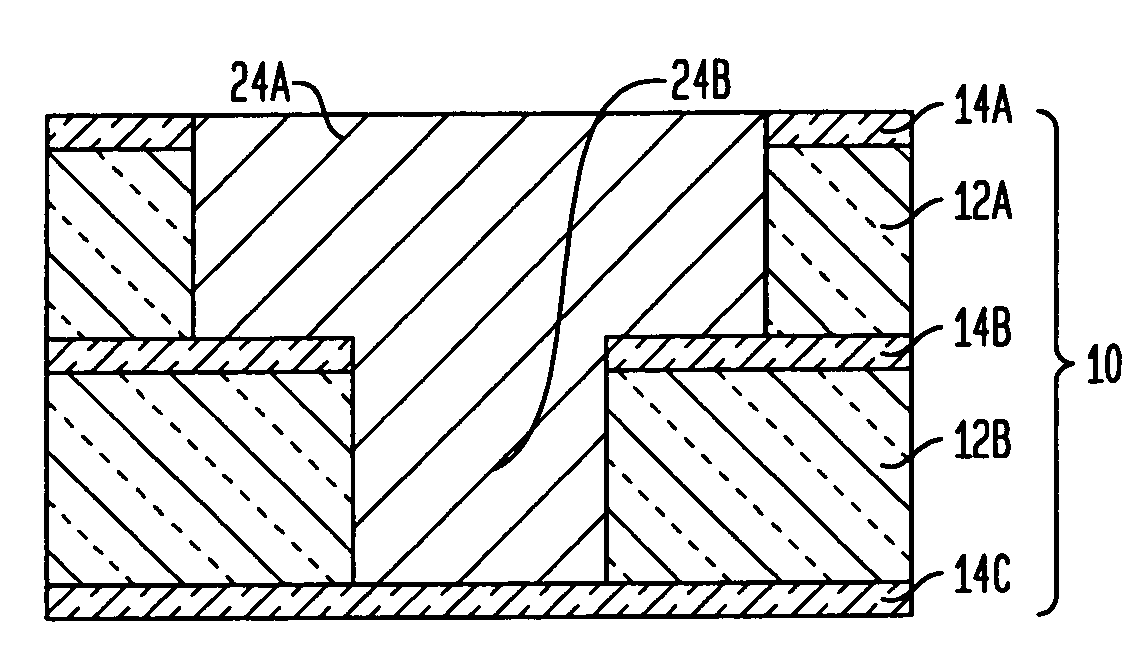

Structures and methods for low-k or ultra low-k interlayer dielectric pattern transfer

InactiveUS7695897B2Expand line spacingIncreasing the thicknessElectric discharge tubesDecorative surface effectsDielectricResist

The present invention relates to improved methods and structures for forming interconnect patterns in low-k or ultra low-k (i.e., having a dielectric constant ranging from about 1.5 to about 3.5) interlevel dielectric (ILD) materials. Specifically, reduced lithographic critical dimensions (CDs) (i.e., in comparison with target CDs) are initially used for forming a patterned resist layer with an increased thickness, which in turn allows use of a simple hard mask stack comprising a lower nitride mask layer and an upper oxide mask layer for subsequent pattern transfer. The hard mask stack is next patterned by a first reactive ion etching (RIE) process using an oxygen-containing chemistry to form hard mask openings with restored CDs that are substantially the same as the target CDs. The ILD materials are then patterned by a second RIE process using a nitrogen-containing chemistry to form the interconnect pattern with the target CDs.

Owner:GLOBALFOUNDRIES INC

Semiconductor device and forming method thereof

InactiveCN109427559ASimple processHigh densitySemiconductor/solid-state device manufacturingEngineeringSemiconductor

The invention relates to a semiconductor device and a forming method thereof. The method comprises the following steps: forming a fragmented top mask structure in a first region of a bottom mask material layer, wherein the top mask structure comprises a top mask layer and the top mask structure also stretches to partial surface of an edge region; using the top template structure as the mask to perform modifying processing on the edge region and a third region of the bottom mask material layer; forming a modifying layer in the edge region and the third region of the bottom template material layer; removing the modifying layer and forming a groove in the edge region and the third region of the bottom template material layer so that the first region and the middle region of the bottom mask material form a bottom mask layer between adjacent grooves. The method simplifies the imaging craft process.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Sulfonium onium salt photoacid generator containing cedrol structure and preparation method thereof

PendingCN111123645AGood hydrophilic-lipophilic balanceIncrease fat solubilityOrganic compound preparationCarboxylic acid esters preparationOrganic solventHydrogen atom

The invention relates to the technical field of photoresist, and particularly discloses a sulfonium salt compound containing a cedrol structure, a preparation method of the sulfonium salt compound, aphotoacid generator and an application of the photoacid generator. The sulfonium onium salt compound containing the cedrol structure comprises anions and cations, the anion and the cation each have astructure in which R1 and R2 each independently represent an alkyl group, a cycloalkyl group, a heteroalkyl group, or a heterocycloalkyl group, and P1, P2, and P3 each independently represent a hydrogen atom or an optionally substituted alkyl group having 1 to 12 carbon atoms. The photoacid generator prepared by the invention has good hydrophilicity, can improve the solubility in an organic solvent, and can effectively inhibit the diffusion of acid. According to the preparation method provided by the invention, the sulfonium onium salt compound containing the cedrol structure is obtained by reacting the sulfonic acid compound containing the cedrol structure with the sulfonium halide, and the preparation method is simple.

Owner:上海博栋化学科技有限公司

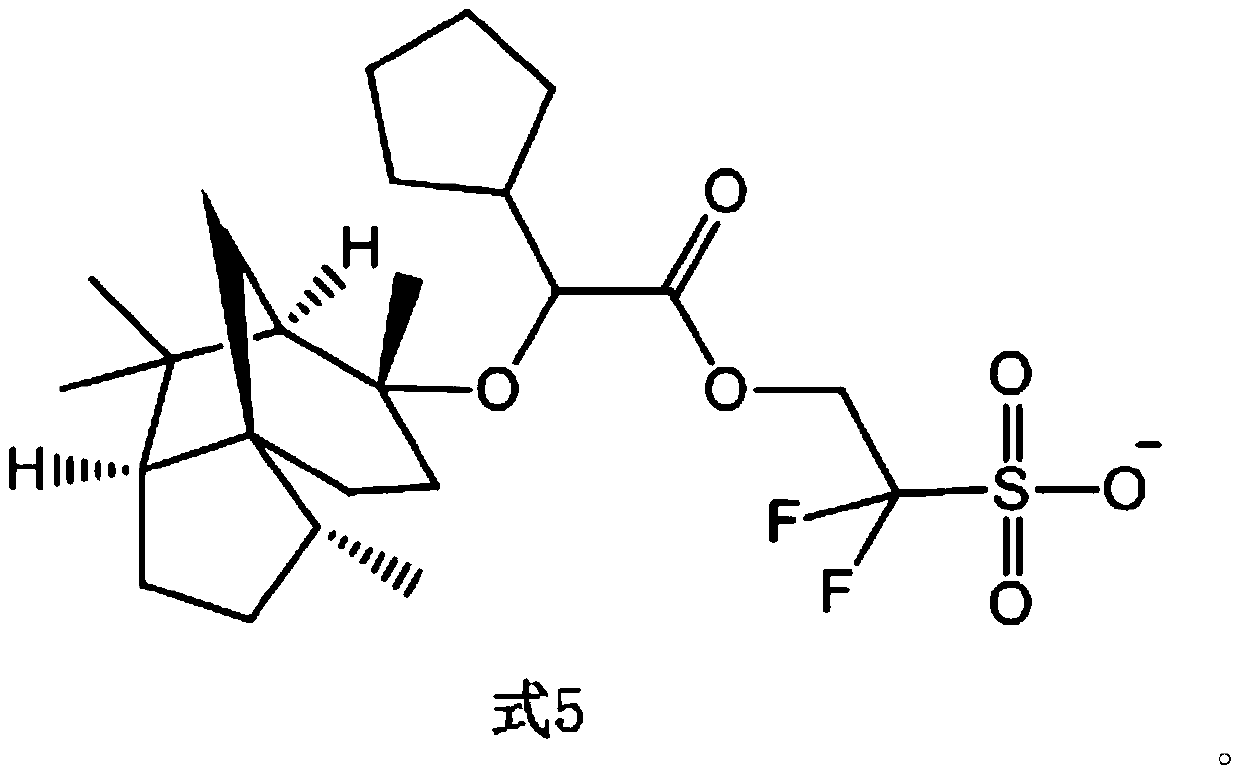

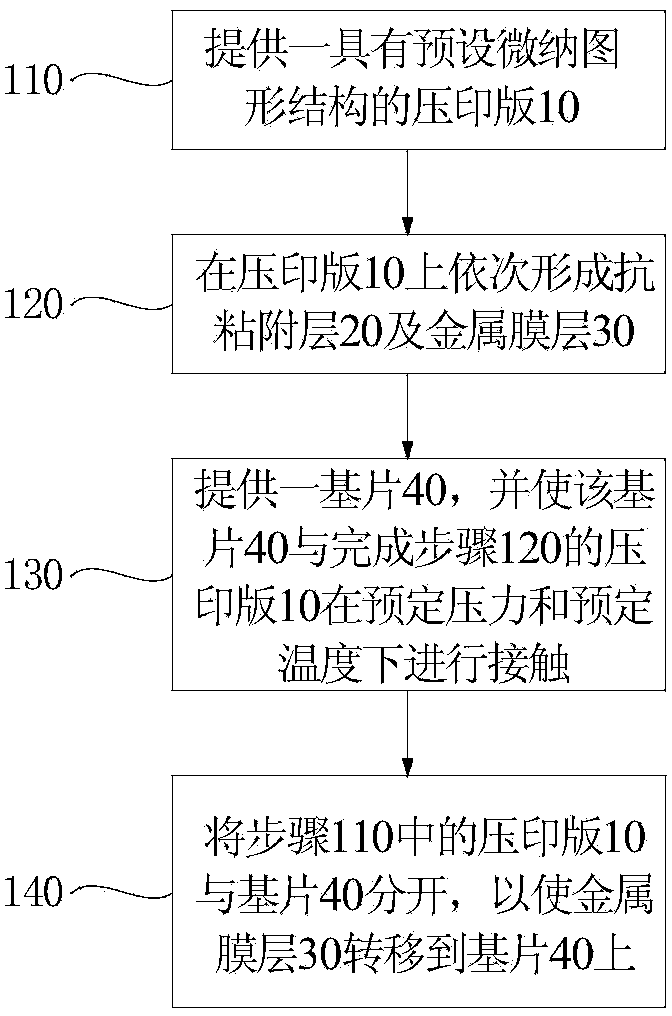

Metal patterning method

ActiveCN105502281ASimple processHigh precisionDecorative surface effectsChemical vapor deposition coatingMicro nanoNano structuring

The invention discloses a metal patterning method. The metal patterning method comprises the following steps: A) providing an imprinting plate with a preset micro-nano pattern structure; B) forming an anti-adhesion layer and a metal film layer in sequence on the imprinting plate; C) providing a substrate, and making the substrate come into contact with the imprinting plate being subjected to the step B) under a predetermined pressure and at a predetermined temperature; and D) separating the imprinting plate obtained in the step A) from the substrate to transfer the metal film layer onto the substrate in order to form a nano-metal structure on the substrate. According to the metal patterning method disclosed by the invention, the imprinting plate provided with a structural body of which a side wall is indent is utilized, so that the edge roughness of the nano-metal structure transferred onto the substrate can be reduced effectively, and metal patterning in a vacuum environment can be realized. Moreover, the metal patterning method is high in accuracy and simple in process; the cost of metal patterning, particularly metal nano-structure patterning is lowered greatly; and meanwhile the machining efficiency can be increased.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

Resist composition and patterning process

ActiveUS20170003590A1Improve throughputReduce developmentSemiconductor/solid-state device manufacturingPhotomechanical coating apparatusPolymer scienceAlcohol

A resist composition is provided comprising (A) a fluorine-containing polymer, (B) a base resin, (C) an acid generator, and (D) a solvent mixture of a first solvent which is a C5-C8 ketone, C4-C6 alcohol, C3-C6 ether or C4-C9 ester and a second solvent which is a lactone ring-containing C6-C9 compound. A pattern is formed by coating the resist composition, prebake, exposure, and development. In immersion lithography, the resist film is improved in water slip. In EB or EUV lithography, outgassing is suppressed and edge roughness is reduced.

Owner:SHIN ETSU CHEM IND CO LTD

Resist composition and patterning process

ActiveUS20140065546A1Reduce edge roughnessInhibition formationPhotosensitive materialsElectric discharge tubesResistSolubility

A polymer capable of increasing alkali solubility under the action of acid, as a base resin is blended with a polymer comprising recurring units derived from a styrene having 1,1,1,3,3,3-hexafluoro-2-propanol as a polymeric additive to formulate a resist composition. The photoresist film formed using the resist composition is effective for minimizing outgassing therefrom during the EUV lithography, reducing LWR after development, and suppressing formation of blob defects after development because of its hydrophilic surface.

Owner:SHIN ETSU CHEM IND CO LTD

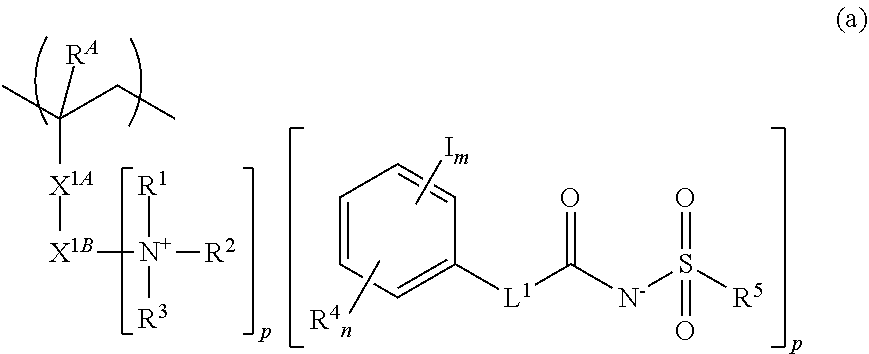

Positive resist composition and patterning process

ActiveUS20200393760A1High sensitivityHigh resolutionPhotosensitive material processingPolymer scienceHydroxy group

A positive resist composition comprising a base polymer comprising recurring units (a) having the structure of an ammonium salt of N-carbonylsulfonamide having an iodized aromatic ring, and recurring units (b1) having an acid labile group-substituted carboxyl group and / or recurring units (b2) having an acid labile group-substituted phenolic hydroxyl group exhibits a high sensitivity, high resolution, low edge roughness and dimensional uniformity, and forms a pattern of good profile after exposure and development.

Owner:SHIN ETSU CHEM IND CO LTD

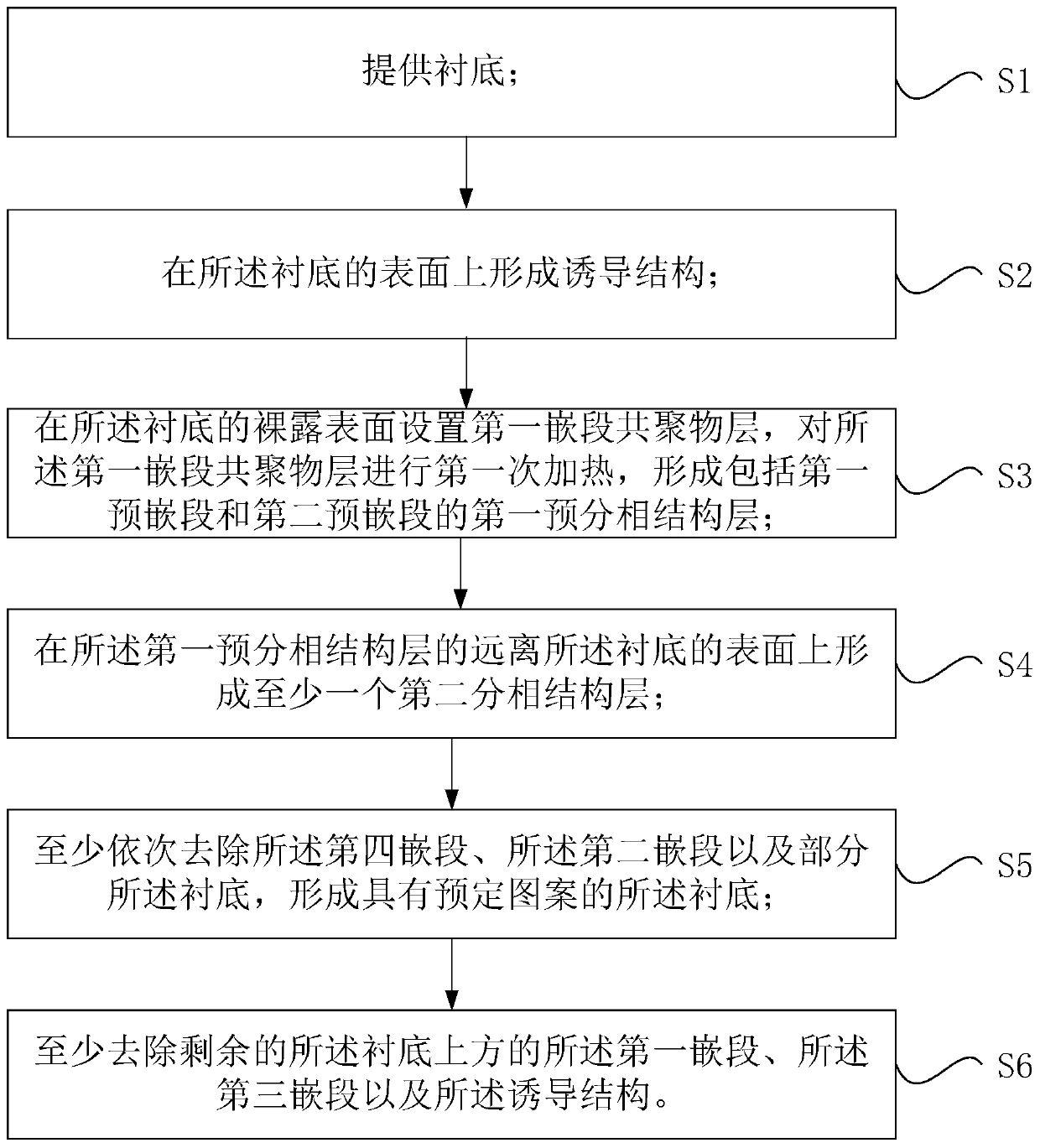

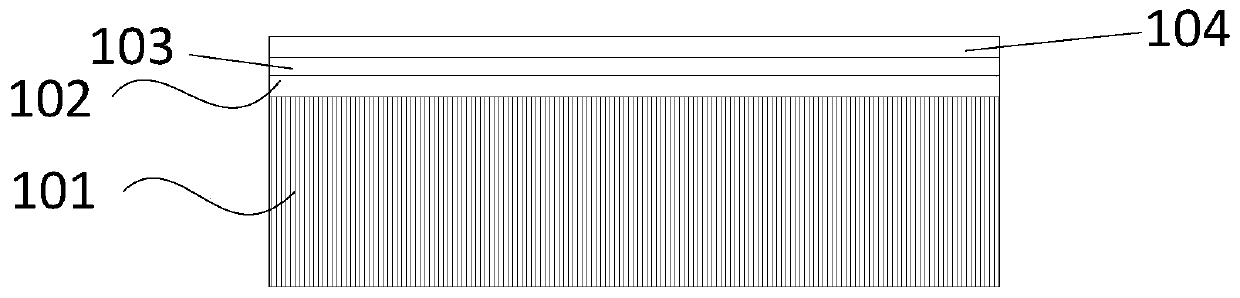

Semiconductor structure and manufacturing method thereof

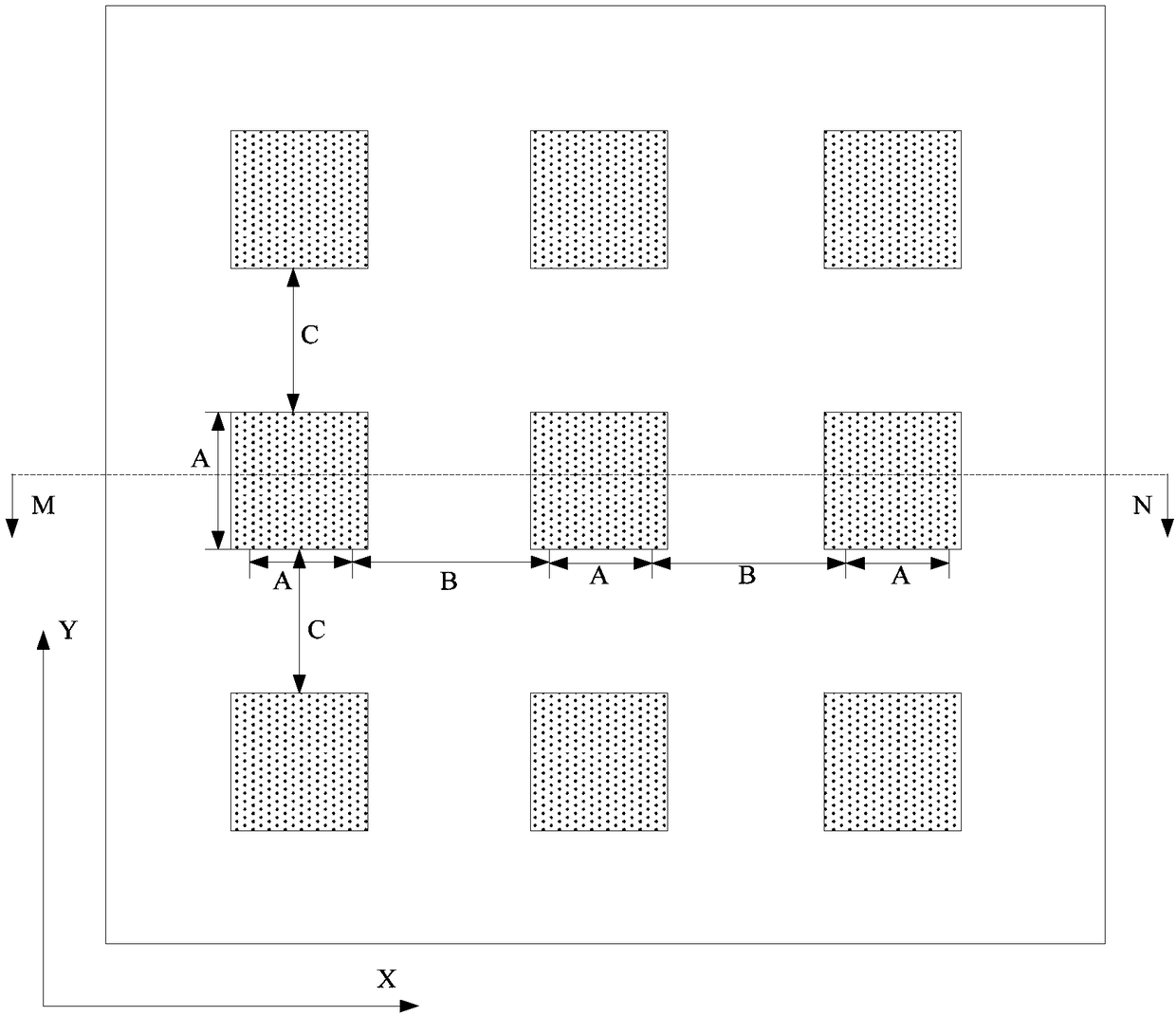

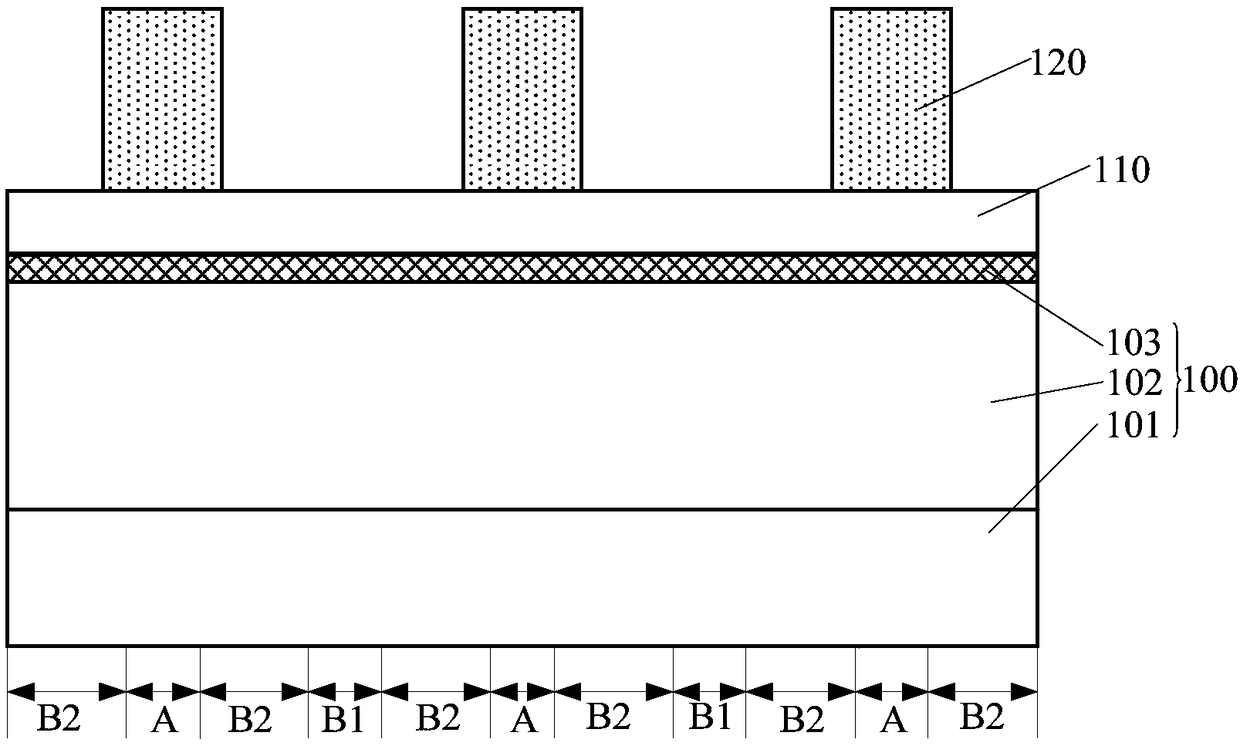

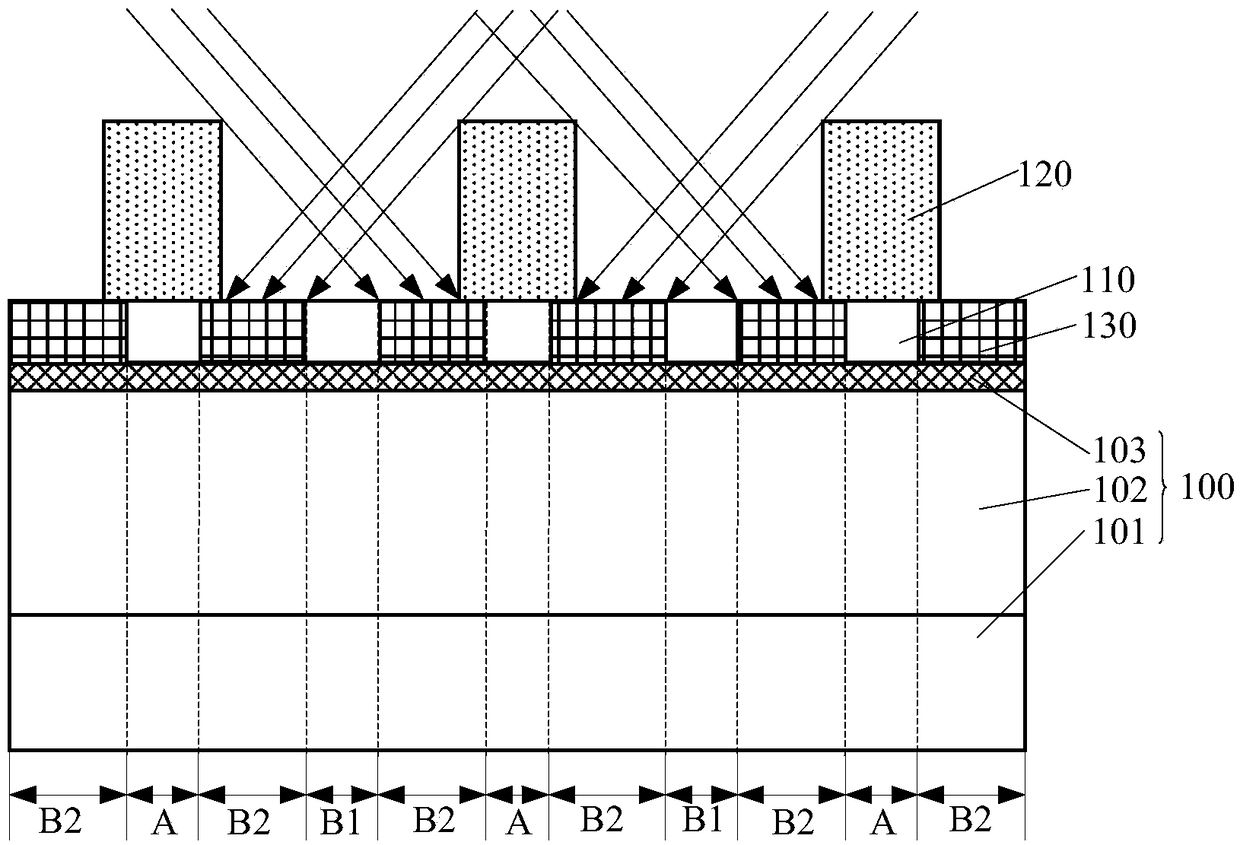

ActiveCN109712871AIncreased process windowLess uniformPhotomechanical apparatusSemiconductor/solid-state device manufacturingPhase splittingSemiconductor structure

The invention provides a semiconductor structure and a manufacturing method thereof. The manufacturing method comprises the following steps: S1, providing a substrate; S2, forming an induction structure on the surface of the substrate; S3, arranging a first block copolymer layer on the exposed surface of the substrate, and heating the first block copolymer layer for the first time to form a firstpre-split-phase structure layer comprising a first pre-block and a second pre-block; S4, forming at least one second split-phase structure layer on the surface, far away from the substrate, of the first pre-split-phase structure layer; S5, at least removing the fourth block, the second block and part of the substrate in sequence to form the substrate with a predetermined pattern; S6, at least removing the first block, the third block and the induction structure above the remaining substrate. According to the manufacturing method, a phase splitting process is carried out twice, and the manufactured structure has fewer defects, is better in uniformity and is lower in edge roughness.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Patterning process

ActiveUS20160363866A1Enhance water slipReduce edge roughnessSemiconductor/solid-state device manufacturingPretreated surfacesSolventBoiling point

A pattern is formed by coating a resist composition comprising a fluorine-containing polymer, a base resin, an acid generator, and an organic solvent, baking the composition at 50-300° C. in an atmosphere of a solvent having a boiling point of 60-250° C., exposure, and development. In immersion lithography, the resist film is improved in water repellency and water slip, and LWR after pattern formation is reduced. In EB or EUV lithography, outgassing is suppressed and LWR is reduced.

Owner:SHIN ETSU CHEM IND CO LTD

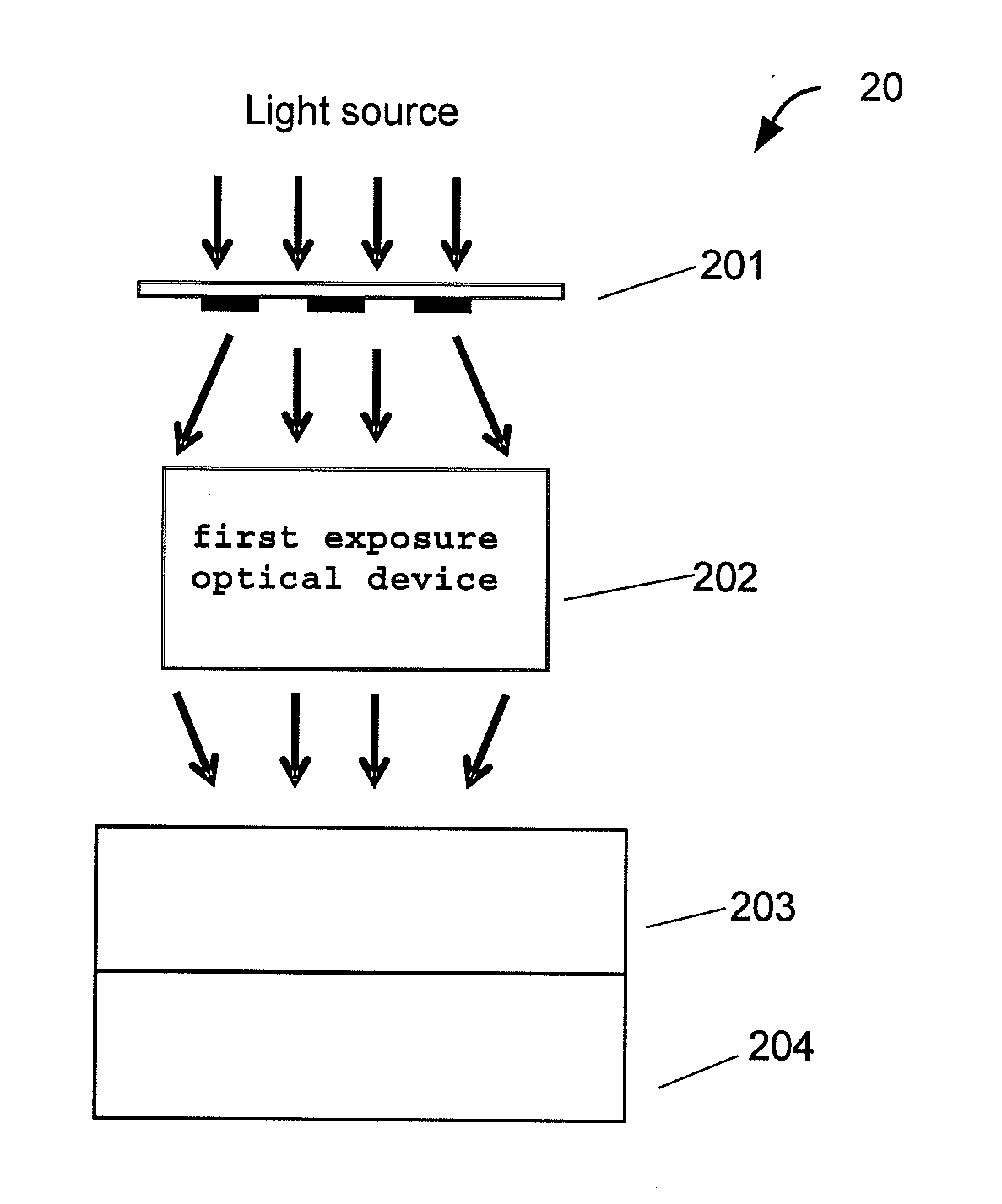

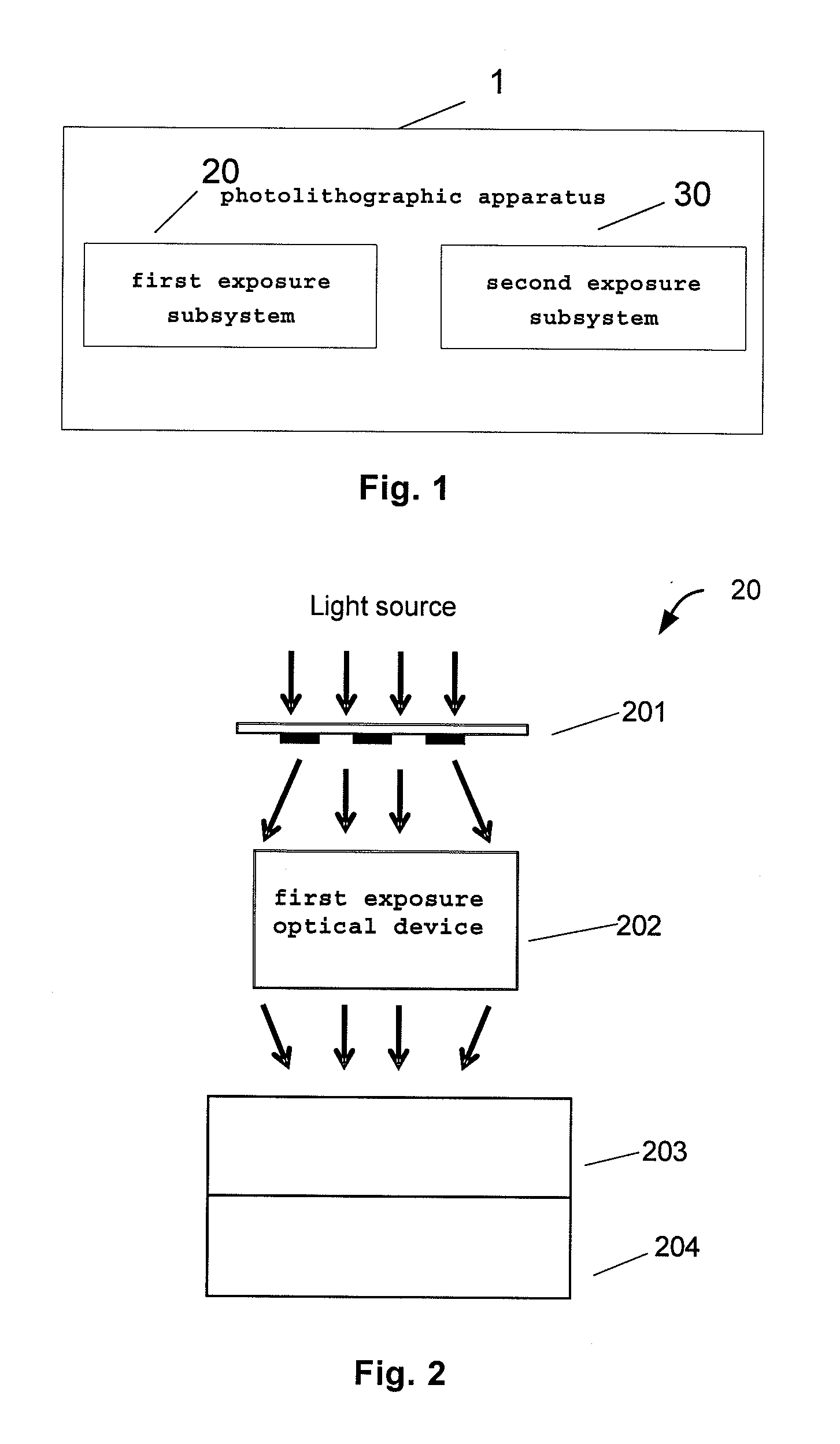

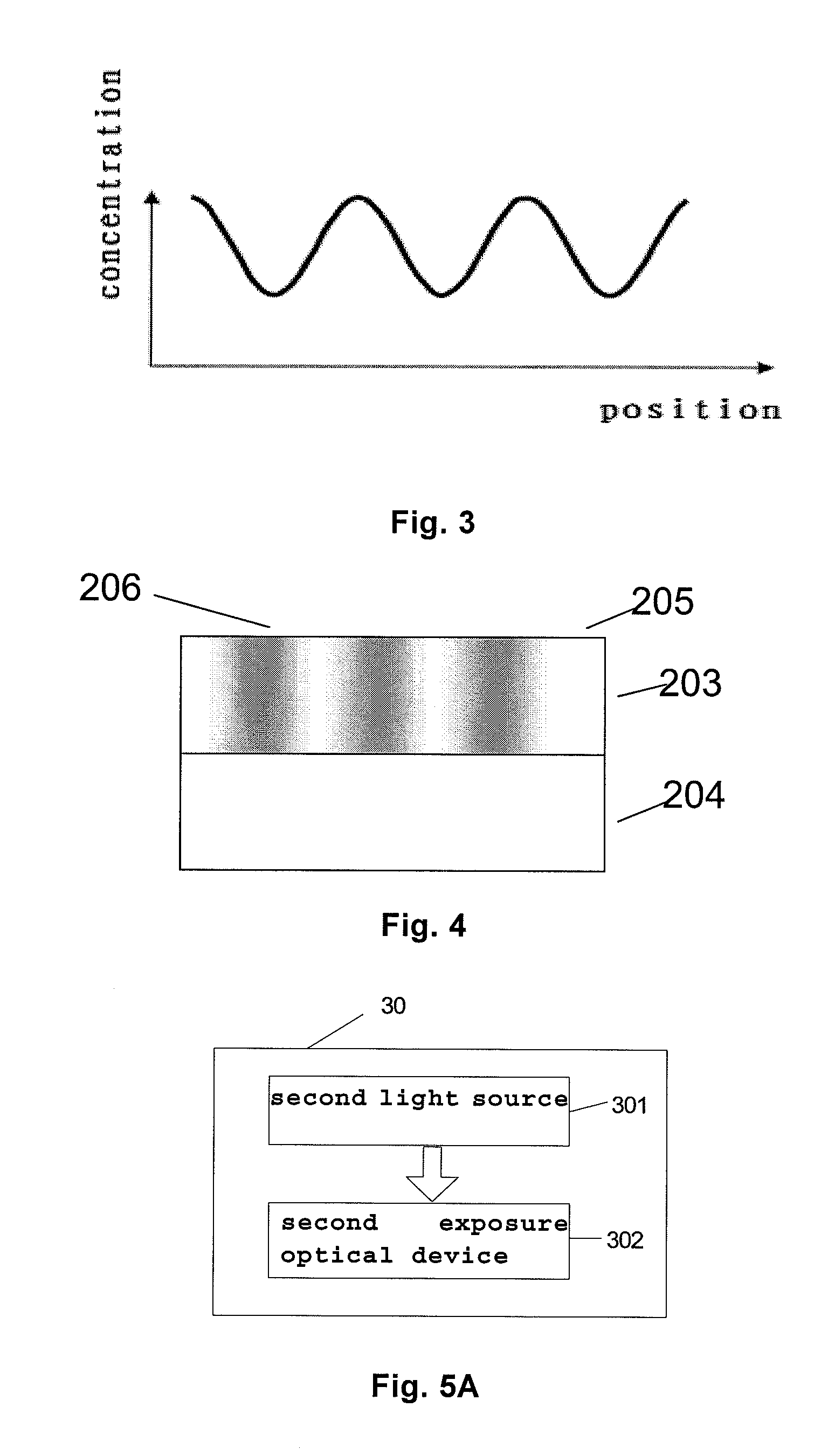

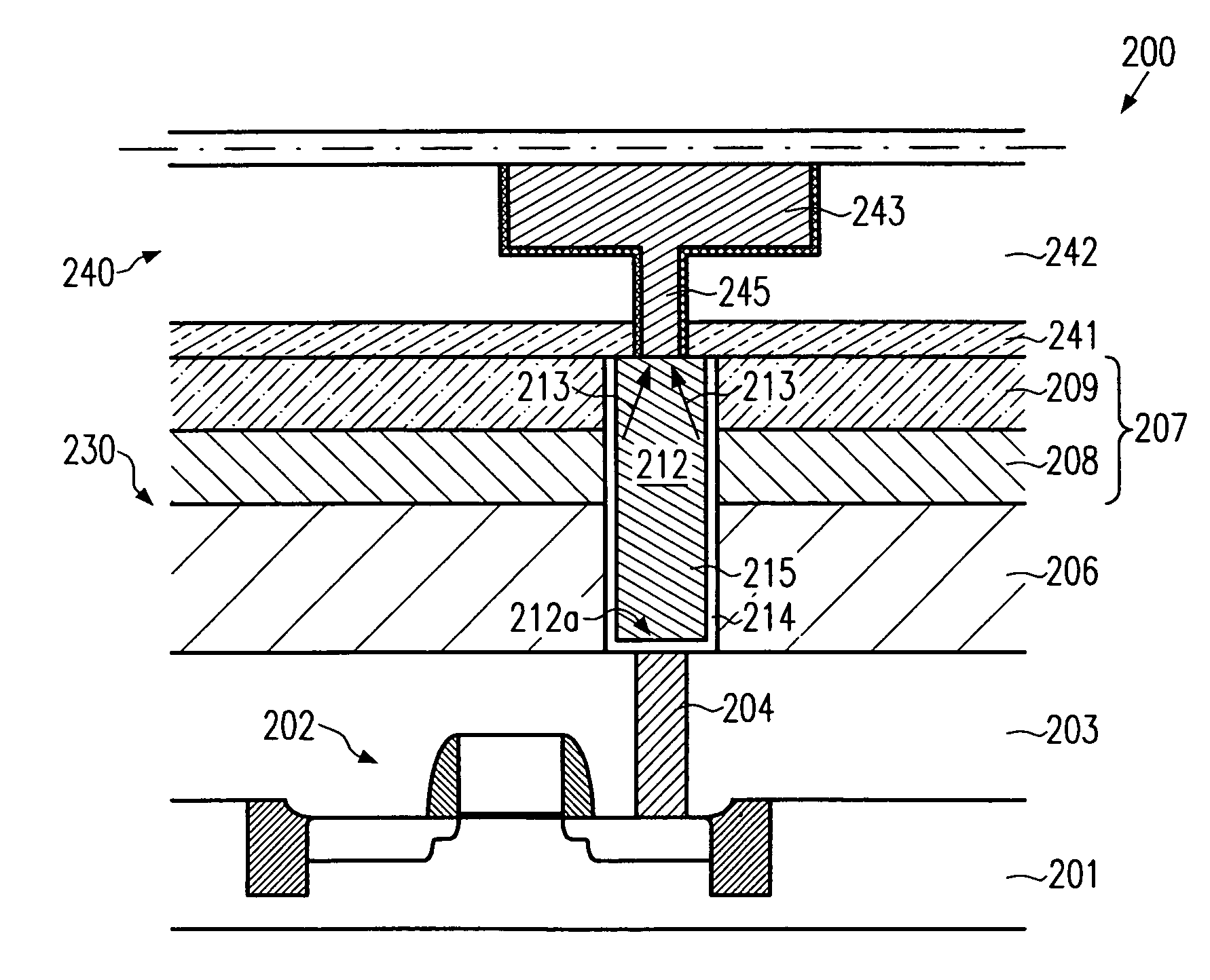

Photolithographic apparatus

ActiveUS20130083302A1Increase contrastReduce edge roughnessPhotomechanical apparatusPhotographic printingResistLatent image

A photolithographic apparatus for use with a photo-resist comprises a first component that generates a first chemical substance and produces a chemical amplification action and a second component that generates a second chemical substance. The photolithographic apparatus comprises a first exposure subsystem for selectively illuminating a surface of the photo-resist using a light of a first wavelength band such that the first component generates the first chemical substance and a second exposure subsystem for uniformly illuminating the surface using a light of a second wavelength band such that the second component generates the second chemical substance. The second chemical substance reacts with the first chemical substance to reduce the mass concentration of the first chemical substance in the photo-resist and improves the contrast of a latent image of the first chemical substance formed in the photo-resist.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Method for forming a metallization layer stack to reduce the roughness of metal lines

ActiveUS7279415B2Deleterious effectReduced dimensionSemiconductor/solid-state device manufacturingLithographic artistEngineering

A method for making a simplified dielectric layer stack for the first metallization layer is provided in combination with an improved anisotropic etch process, wherein the etch attack at the trench perimeter is reduced for a patterning process on the basis of a 193 nm lithography. In the simplified layer stack, a bottom etch stop layer formed beneath a low-k dielectric layer may be omitted, thereby reducing production costs while enhancing product performance by lowering leakage currents in the first metallization layer.

Owner:ADVANCED MICRO DEVICES INC

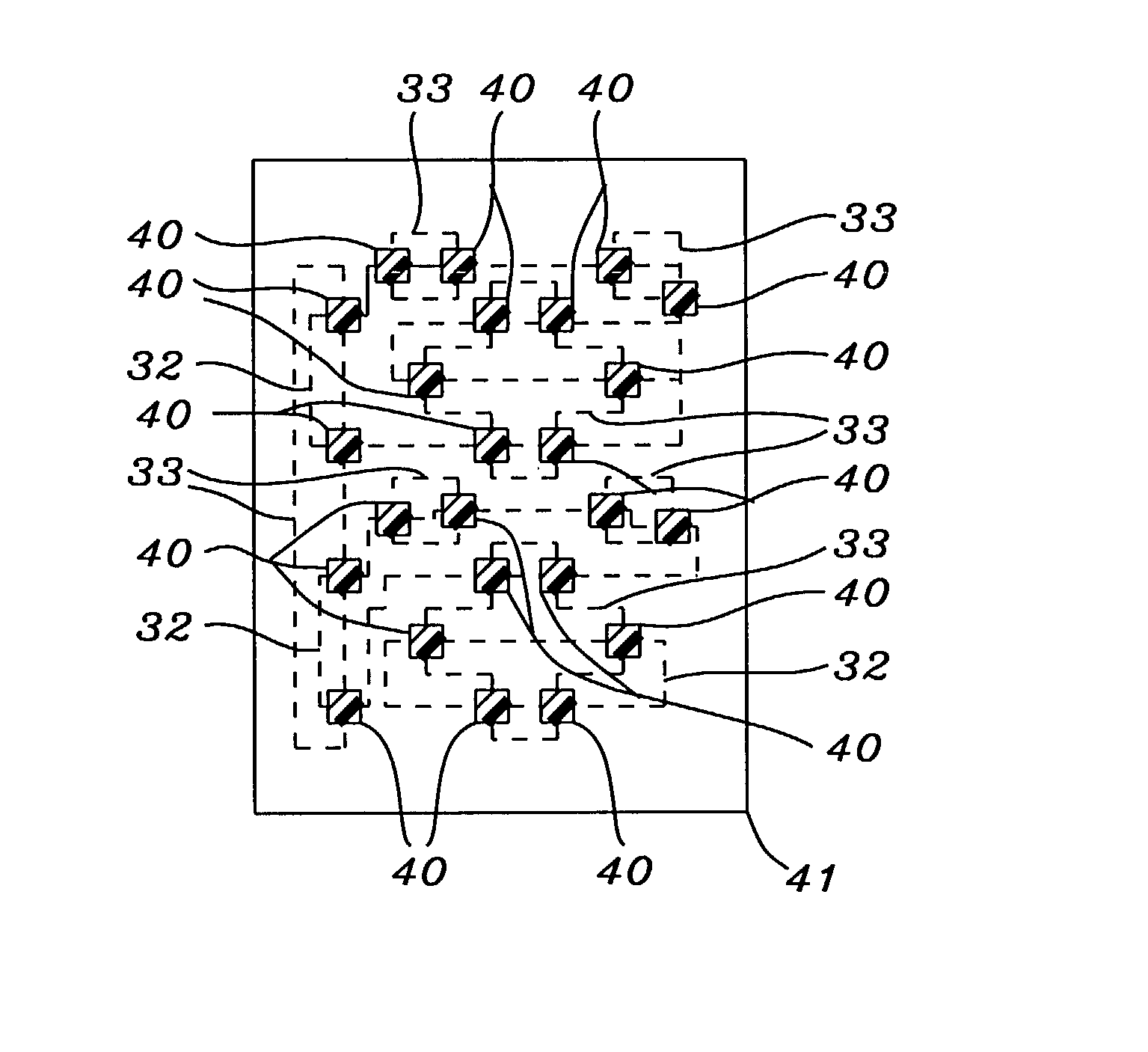

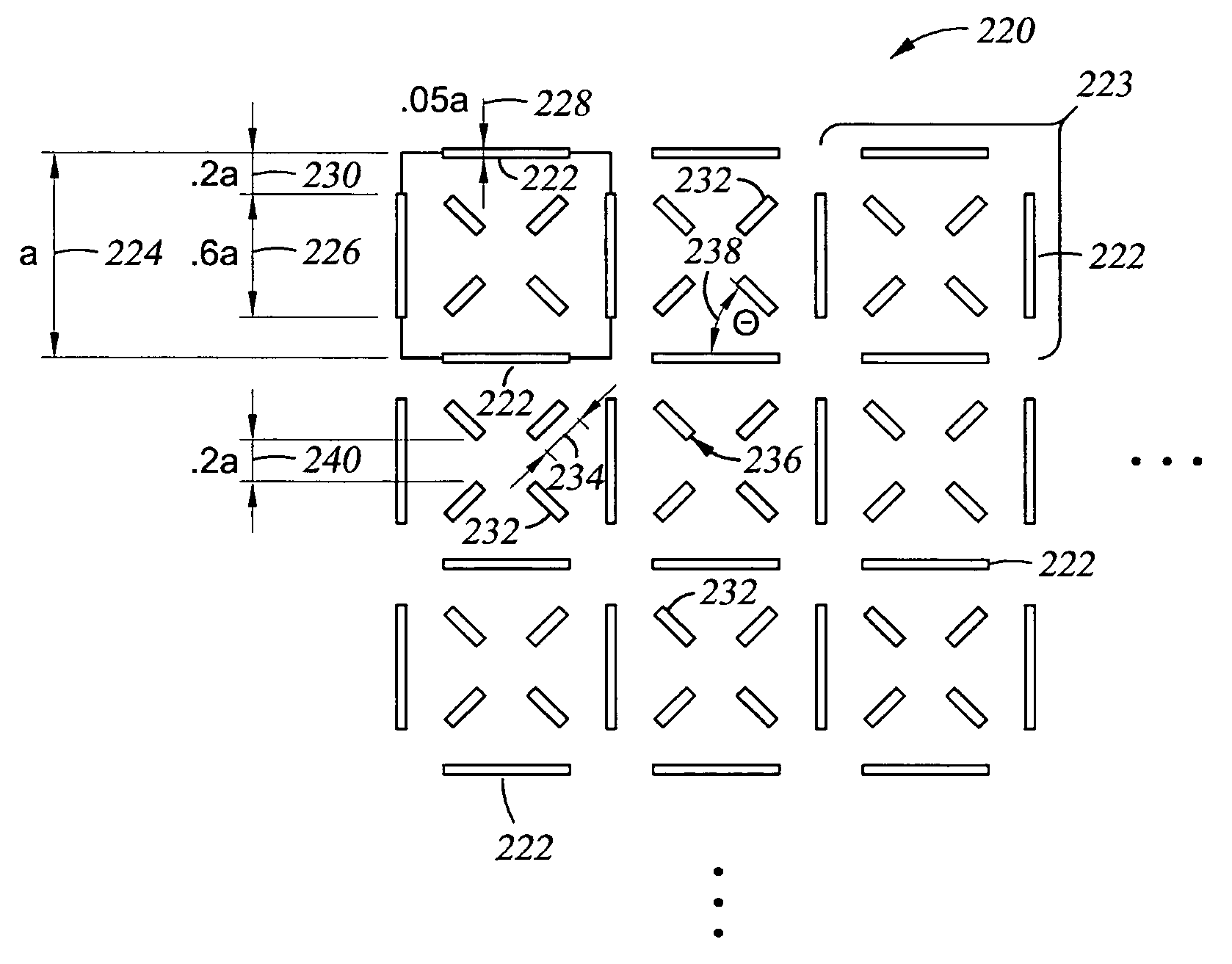

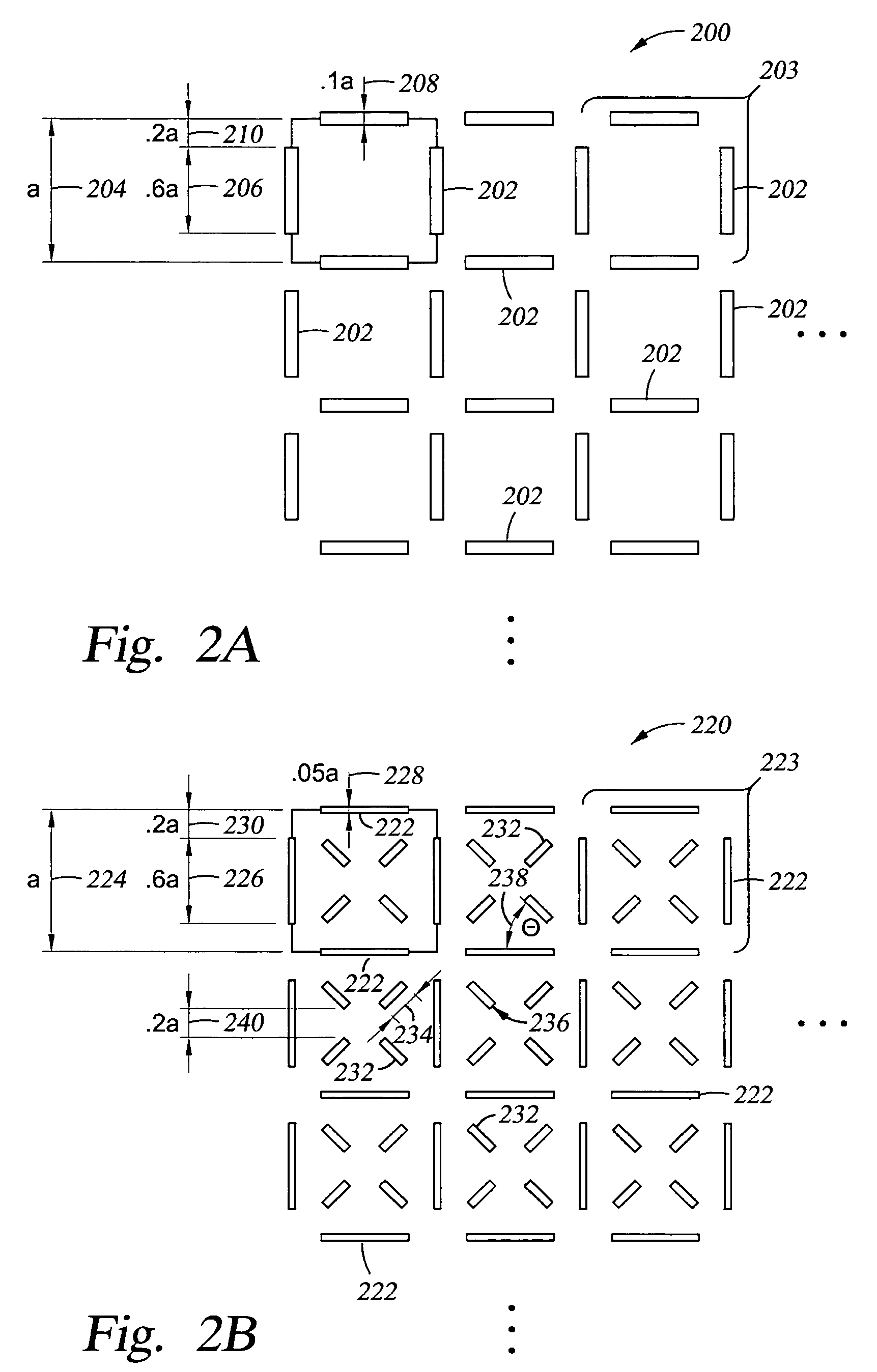

Method and apparatus which enable high resolution particle beam profile measurement

InactiveUS7368731B2Simple materialHigh resolutionThermometer detailsBeam/ray focussing/reflecting arrangementsSurface finishMetrology

The PSF for a metrology array for high resolution particle beam profile measurement has been improved by improving five major elements of the metrology array. While improvement in each of the five elements provides and improved PSF, a combination of all five of the elements provides an unexpected synergistic effect. The individual elements include the use of a plurality of slots as apertures; use of a high-Z material in forming the array; employing sidewalls on the slotted opening apertures where the sidewall forms an angle with a horizontal surface at the base of the array which is at least 75°; employing a knife edge where the upper corner radius ranges from about 1 nm to about 5 nm; and providing a surface finish at the upper corner of each knife edge which is less than 5 nm RMS.

Owner:APPLIED MATERIALS INC